Управляющий регистр для буферного запоминающего устройства

Иллюстрации

Показать всеРеферат

Изобретение относится к вычислительной технике и может быть использовано в БИС буферных запоминающих устройств типа FIFO на совмещенных транзисторных структурах (инжекционных схемах). Целью изобретения является расширение области применения регистра за счет обеспечения возможности асихронной работы и формирования требуемых по длительности сигналов управления сдвигом. Эта цель достигается путем организации в управляющем регистре внутренней асинхронной времяформующей цепи, состоящей в каждом разряде из триггера 1, усилителя 5 и логического элемента 10. Такая цепь производит асинхронное формирование требуемых по длительности сигналов, управляющих сдвигом в элементах памяти накопителя ЗУ. При этом, во-первых, импульсы на выходах сдвига управляющего регистра уплотнены, во-вторых, во времяформирующей цепи содержится идентификатор задержки переключения элементов памяти 28, благодаря чему при отклонении питающих инжекционных токов время срабатывания инжекционных элементов памяти хотя и изменяется, но соответственно изменяется и длительность формируемых импульсов, оставаясь всегда такой, какая необходима для надежного переключения элементов памяти. 3 ил.

СОЮЗ СОВЕТСНИХ

СОЦИАЛИСТИЧЕСНИХ

РЕСПУБЛИН

„„SU„„149940 (51)4 G 11 С 19/00

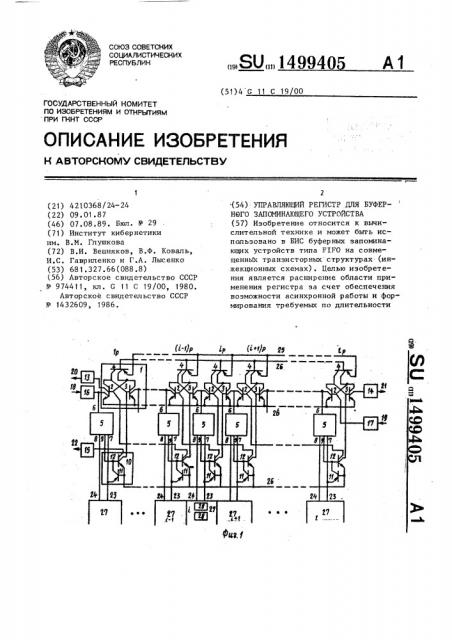

ОПИСАНИЕ ИЗОБРЕТЕНИЯ (i-Г)р (с+ /р уу

Фиг. 1

ГОСУДАРСТВЕННЫЙ КОМИТЕТ

ПО ИЗОБРЕТЕНИЯМ И ОТНРЫТИЯМ

ПРИ ГКНТ СССР

Н А BTOPCHOMY СВИДЕТЕЛЬСТВУ (21) 4210368/24- 24 (22) 09.01.87 (46) 07.08,89. Бюл. ¹- 29 (71) Институт кибернетики им. В.М. Глушкова (72) В.И. Вешняков, B.Ô. Коваль, И.С. Гавриленко и Г.А. Лысенко (53) 68 1.327.66(088 .8) (56) Авторское свидетельство СССР № 974411, кл. G 11 С 19/00, 1980.

Авторское свидетельство СССР № 1432609, 1986.

2 (54) УПРАВЛЯЮЩИЙ РЕГИСТР ДЛЯ БУФЕРНОГО ЗАПОМИНАЮЩЕГО УСТРОЙСТВА (57) Изобретение относится к вычислительной технике и может быть использовано в БИС буферных запоминаюших устройств типа FIFO на совмещенных транзисторных структурах (инжекционных схемах) . Целью изобретения является расширение области применения регистра sa счет обеспечения возможности асинхронной работы и формирования требуемых по длительности

1499405 сигналов управления сдвигом. Эта цель достигается путем организации в управляющем регистре внутренней асинхронной времяформующей цепи, состоящей в каждом разряде из триггера I усилителя 5 и логического элемента 10. Такая цепь производит асинхронное формирование требуемых по длительности сигналов, управляющих сдвигом в элементах памяти накопителя ЗУ. При этом, во-первых, импульсы на выходах сдвига управляющл о регистра уплотнены, во-вторых, во времяформирующей цепи содержится идентификатор задержки переключения элементов памяти 28, благ одаря ч ему при отклонении питающих инжекционных токов время срабатывания инжекционных элементов памяти хотя и изменяется, но соответственно изменяется и длительность формируемых импульсов, оставаясь всегда такой, какая необходима для надежного переключения элементов памяти. 3 ил.

Изобретение относится к вычислительной технике и может бьггь использовано в буферных запоминающих устройствах (ЗУ) типа Р?ГО на совмещенньгх и-р-п-р-транзисторных структурах (инжекционных схемах).

Цель изобретения — расширение области применения регистра за счет возможности асинхронной работы и формирования требуемых по длительности сигналов управления сдвигом.

На фиг. 1 приведена схема управляющего регистра и его подключение к числовым линейкам (ЧЛ) буферного

ЗУ; на фиг. 2 — схема усилителя; на фиг. 3 — схема элемента памяти (ЭП) ЧЛ.

Управляющий регистр (УР) содержит 35 в каждом i-м разряде, i =- 1., 1, триг-. гер 1, состбящий из первого . и второго 3 ключевых и-р-и-транзисторов и совмещенного с ними токозадающего транзистора 4, усилитель 5, имеющий 40 вход 6, первый.. 7 и второй 8 токовые выходы, потенциальный выход 9, и логический элемент 10, состоящий из токозадающег о р-п-р-транзистора

11 и тслючевого и-р-и-транзистора 12, 45 три вьп.-одных буферных формирователя

13-15 и два входных буферных формирователя 16 и 17. На схеме (фиг . 1) показаны также вход 18 записи, вход

19 считывания, выход 20 готовности записи, выход 21 готовности считывания, выход 22 наращивания памяти

УР, выходы 23 и 24 управления сдвигом

УР, шина 25 инжекционного питания, шина 26 нулевого потенциала УР, числовые линейки 27, состоящие из элементов 28 памяти.

Усилитель 5 (фиг. 2) содержит и-р-и-транзисторы 29 и 30, совмещенные с р-п-р-транзисторами 31 и 32, и-р-и-транзистор 33, пять резисторов 34-38, шину 39 питания.

Элемент памяти (фиг. 3) содержит и-р-и-транзисторы 40 и 41> сонмещенные с р-и-р-транзистором 42, и-р-и-транзисторы 43 и 44, совме.ценные с р-и-р-тоанзи тором 45.

Диоды 46 и 47 являются общими для всей ЧЛ. 48 — инжектор накопителя буферного ЗУ. Элементы памяти каждой ЧЛ парафаэно связаны с соответствующими элементами памяти предыдущей и последующей ЧЛ.

Управляющий регистр работает следующим образом.

При частичном заполнении ЗУ определенное количество триггеров правой расти УР установлено в "1", а .невой части — в "0". единичное состояние триггера соответствует (. аю, когда транзистор 2 открыт, а транзистор 3 закрыт.

В рс.киле хранения открьгг один из двух транзисторов: 2 н i"ì триггере нли 3 в (i-1)-м, вследстн. чег: ходные транзисторы 29 (фиг. 2) всех усилителей 5 закрыты, чр» v.— сторы 32 открыты, и базы траяз ".-..торов 12 блокированы нулевым потенциалом. Транзисторы 33 закрыты, на токовых выходах усилителей всех разрядов УР напряжение 0 В.

При записи в буферное ЗУ нового информационного слова на вход 18 подается короткий импульс, и в базу входного транзистора 29 первого усилителя инжектируется заряд, транзистор 29 открывается, а транзистор 30 закрывается и разблокирует базу транзистора 12. База транзистора 33 заряжается, на первом и втором выходах г т е (1i(ip»<г;

СГ )гг((15ЛЕ>Г (>1 Тона 0 Кт)! (". i1;? .<);! !iI слОВО з<11(оситсЯ В i! iР;) ВуJo 1 (l!<(ЯОГИ(т .!1}1:.>.у (1р 0}1 С 0" 1 . И Нлтс((.j(! <(З 1 p,"! <(! )? б (1 3 у т р а 11 з и с т ) p р ) - . <з

"7 7 !)Янзl!С (О;. 2 От)(р(IВП г ..) „)?Г>:<7 °вЂ”

OT (?И(? т! ЕГО О! ВОДИ Г(H 1!<

rI Е!30i О )! 01 <З ПП)1" 1!i (<<()Я< сто))а 3 и тр г? > пер I!(7! ()

1: ((;:p

Гс;,ти те)!11 Г! . !)а=; )1>1; . 1>Г

СС 1 <7(I(7?3 ((li Г? <., ), <"! . ° !. i. тт<,

} 1}(Р У)Г>т сЯ и) (Г! 5з(т,(?. i В „,!. тсля "7 Второго ра .ря;,,:", !)0;; ",:;:., ИПФГ)}) }1<11(ИОНН<)С

И 3 (!Op!?()1! (д 1!ЯК

П () i,". II) (I>

11 1:

1 ° t (. . T(.:(В !! .3>нггr 11 тт-, -;i 1,", I! !

1(?(, i ()i i >(".! (; 1)(I .ii! . .:.:;>Г

< (!I! а .> 1:. ° !? г. !> . »i !!i) I)i! НП 1! ! I

> (I т!

I — т! г, < г

;т;б: т !

Г? f ii i ::.,! (iii" )

:;(!! Ii !)i

1 }1.

Ок 0!1<<;:!1 .; (?) "}((!. <(. :.т,

П))с)) (. . }3(1)(?.т 01 i

1 ! !! i I 0 . ()(Г

Г! г>, i ) i Л:

:; С): 01<31 )1! . i!: 7

<?, (Т О>? 1 (? П! .

Вl? Г():.(; ) (! ) I i ." 1,, .. !.-;-,гг;гт;1,.! i

}(Р I НС ) !3, j jj) <?Л

) i;i(. > н (, i i ) i! ТI .!!: i (., ., 1. 11 5 СТ i!. .".! f (i! ii I j < J!j . i!I .; .) i: г i !!!i,", е,. I !!:i

;!T-,)т1 3.)г ГР; ()т г(! Р;i

У(1 (111 1 Г Н}(7, i,-! )1 11(I 01) 0 i i, I>ii

) г!

Р;- 3() 71))(З Я ба 3 У 7 т, ; i }i i I Ñ Ò AP т .

O3((iT) ((I.I)! )+I;j) I}? <((Г(?)1 Р а - () г(етгт,-*; ° зу транзистора 12. ;,з» тра?,"и!с <.;;)а

33 i ã0 разрл:т;1 . с!! -.!17 е)1!! Парня:а (}т-1)я;г;<>(я(<т 1)3 тг "1:< ) i i! т тт );10 I

Г(П ;).Ш >Я т На ?ГИТ "P!! j) .1 }! ЗПС 0,,:! ).i! н(?Г(Г)яжен(.е пт?ре;ЕЕ<ется с по}?и;.< ш.;;

) на вет ицкпу прп? : p!l!, О, L, с г

11эпрЯ)?(еiп!е !(н -,i:,-(!,, .;:1>се 11,:1 .! "(i" 0,, ,1 T3TОРОМ 8 Б:.):..О,-; .:,: >П!!".: .. )(((:.;! Г ". 1 i i ) Р 111 U <Я (. Т (i . 1 (; т I i ),! ((.. !: (т С 1!;) !: 1:. i

ЦИ I(<) }1„31!P)1;!(((,-;т,:) ) j !I.С ii.:(! i (( т(Е <} 7 {ф!1Г ° ), i i!1! I«) !","..: ): р П. 1 ) >г

}1П)(<Е(<}г! .!! ., .,(; )i б !".. (- ) ра 11 ?ii 1 Ора 12 ь J. р}(зр,(Г(с j (ã:. 37 ð;1 ?)рлk>оп т

К РГO OKTPi?В)>>а}(И() т !?00310 Ч СГ 0 <;Ò В(7;т?

) >

СЯ гlа Ш}(Н5> 2<) 3,) j)>i i, б;) -:1! Тра)1.<?1(. Ор Э

3 трлггерл l. го раар:.; .:: i ба 3!)! Гт>:-.л-

->-}.I0T(Г)а 2 !.! -! ) -Гг); а 1:!;i,;I, 3()З 1!

-,,т,>;(а()i («, I> (! г 1 — 1: —;: (>i(! !

1499405 транзистора 29 в 1-м усилителе, и на

его выходах формируются импульсы, по которым ипформационттое слово пз (1-1) — и ЧЛ переписываетгя в 1-ю

5 открывается транзистор 12 1.-го разряда, и 1-й триггер переключается обратно в "1", а (1-1)-й переключается в "0 . Далее аналогично формируются импульсы на выходах (1-1)-го

il усилителя. ттаркерный 0 продвигается по УР до тех пор, пока в "0" . не переключится грапичный триггер, 11 11 . находящийся до этого в 1, и соответственно, по выходам УР справа налево "пробегают 1 импульсы, За такой цикл весь массив хранимых в ЗУ данных сдвигается на одну позицию к выходу.

Формироваттие 2 д происходттт аналогично режиму записи.

Таким образом, УР oróöåñYâëÿåò асинхронное формирогаппе rо своим смежным выходам уплотненных (соприкасающихся) во времени импульсов. Перекрытие импульсов приводит к сквозттым переносам в накопителе и, следовательно, к сбоям, а паузы между импульсами приводят к понижеHHIQ быстродействия.

Запись и считывание в буферном ЗУ

30 асинхронны и независимы. Возможно одновр еменное мног ократ ное обр ащени е для записи и считывания с различной частотой. При этом по УР движутся навстречу маркерные "1" и "0", прерывание их в граничном разряде происхо- 35 дит аналогичтто рассмотренному случаю без конфликтных ситуаций. Максимальная частота записи/считывания определяется длительностью формируемых импульсов и равна 1/2 ".„.

Рассмотрим и сопоставим процессы переключения ЭП и УР. В режиме хранения транзисторы 40 и 41, образующие триггер хранения, запитаны через диод 45

46 и транзистор 42 током хранения, а транзисторы 43 и 44, образутощтте входной парафазный триггер, не запитаны.

При формировании пмттульсов ток питания транзисторов 40 и 4 1 увеличивает- 50 ся приблизительно па порядок, и запитыватотся транзисторы 43 и 44. Открывается тот из них, база которого соединена с коллектором закрытого транзистора 40 (или 41) (i-1)-го ЭП.

Допустим, что конструктивно транзисторы 43 и 44 идентичны транзистору 12, Инжекция заряда в их базы осуществляется от одной и той же шинЫ

23, следовательно, транзисторы 43, 44 и 12 переключаются за одно и то же время.

После открывания транзистора 43 (44) ЭП и транзистора 12 нулевой потенциал воздействует на базы транзистора 40 (41) ЭП и транзистора 3 в i-м, а также транзистора 2 в (i-1)-м разрядах УР, разряжая их, что приводит к закрыванию этих транзисторов, причем возможно временное выравнивание переходных процессов закрывания указанных транзисторов путем регулирования величины тока питания по инжектору УР (шине 25) . Аналогичным образом достигается временное выравнивание переходных процессов открывания транзистора 41 (40) ЭП и транзистора 2 в 1 — м, а также транзистора 3 в (i-1)-м разрядах УР.

Момент открывания транзистора

41 (40) является окончанием времени переключения ЭП (i „), поскольку в этот момент происходит фиксирование состояния ЭП внутренней триггерной связью, Таким образом, имеют место два идентичных во времени переходных процесса: последовательное переключение трех транзисторных структур в

ЭП и последовательное переключение трех аналогичных структур в УР. Другими словами, времяформирующая асинхронная цепочка УР составлена так, что содержит в себе идентификатор задержки переключений 311.

Для надежного переключения ЭП; имеющих некоторый технологический разброс параметров, необходимо, чтобы длительность импульса ц была несколько больше времени С „. С момента окончания переключения ЭП импульс 9 д длится еще некоторое время, определяемое зарядом базы транзистора 30 и разрядом базы транзистора 33 (задержкой выключения уси" лителя) .

Из-за отклонения режимных и технологических параметров в буферном.

ЗУ (температуры, напряжения питания, эффективности инжектора, удельного сопротивления резистора и других) происходит значительное изменение инжекционных токов и-р-и-р-транзисторных структур, что приводит к изменению времени их переключения.

Однако благодаря идентификатору задержки переключения ЭП во время

1499405

L)i1 e<,i — .1МЦ С С С,:;1 формирующей цепи УР длительность

7 всегда будет такой, какая необходима для надежного переключения

ЭП накопителя, но без временной избыточности.

Таким образом, предлагаемый УР обеспечивает асинхронное формирование оптимальных по длительности сигналов управления сдвигами в накопителе буферного ЗУ: импульсы на i-м и (i+1)-м выходах регистра во времени уплотнены (соприкасаются), а во времяформирующей пепи УР содержится идентификато;. "лдержки переключения ЭП накопителя, вследствие чего длительности управляющих импульсов оптимальны. УР может быть составной частью БИС буферного ЗУ, которая может быть изготовлена rro стандартной изопл:.парной технологии. орMyна.> .петен«я

Управляющий г1;.1 тр для буферного зяпоиил 1 niitp c. р< 11 > содс 1. -".:11ти11

K;!...ä: (..1зря",с триггер, сост -:"1 с .. о . вт 1,, i:0 ключевых И ! С;1. Л.:".ЮП ".i О P 11 Р= ..;пи..ра, . it с р которого сс". ци е11 с в .t!)и -:нже1,. 1о11ногс пн1ания рег";стра а I!p.>аы1.:t горо,. кол: ектор». соединены соответ венно с базамт. . ервого и второго и первыми коллект .... -:"с второго и первого ключевых и-р -г=

1 анзисторов. эмиттеры которых и база

35 .".озадающс о ц - . -р-т1:анзистора соее11ы < пп1лой t:ó: с:с :; I.-отенциал= т а v усилите ь. вход котор .го .-цпнен с вторым 1солл::,т "ом пепг;.— ключевого и-р- и-тралзистора чригдан1-.ого разряда « . все». ..;,х. кроме пер с:л — т» орыь. хс,с— !, :ои Вторut о ".эистoра rp,".. -: IImpcтвующег.. азряда. первьп1 токовый в1.ссод усилителя в каждом разряде является первым выходом управления сдвигом регистра, первый выходной буферный формирователь, вход которого соединен с третьим коллектором первого

50 ключевого и-р-и-транзистора триггера первого разряда, а выход является выходом готовности записи регистра, первый входной буферньп1 формирователь, выход которого соединен с вторым коллектором первого ключевого и-р-и-транзистора триггера первого разряда, а вход является входом записи регистра, второй выходной буферный формирователь, вход которого соединен с вторым коллектором второго ключевого п-р-и-транзистора триггера последнего разряда, а выход является выходом готовности считывания регистра, второй входной буферный формирователь, выход которого соединен с базой первого ключевого п-р-и-транзистора триггера последнего разряда, а вход является входом считывания регистра, о т л и ч а ю шийся тем, что, с целью расширения области применения регистра за счет возможности асинХронпой рабо1ч формирования тр бус.;.- . по длить « сти сигна I.i! уг— рав ения сдвигом, в него введен . третий выходной буферный формиров-тель и в каждый разряд регистра ло. гический элемент, сос.:: оящий из ключ=вого п-р — n-транзистора и токоэада::щего р-п-р-транзистора, колл ек! ар

1»о1орс.го соединен с базой ключе.зс 1 о

; - - цанзистора. -..: D — " .;< р-о

;-ля - "-:вес. -р-и-тра11з1 стора и; и .л.:1 <.улевого 1отенциала рег,".стр:, второй токовый выход усилителя дого разряда является соотве=с::-- . ì выходом упр 1i.JIPI" c ä=;rir . .:.-: р=.. гистра„потенци льный выход уси;.:-;-теля в каждом разряд» соеди.-.=.-; с базой ключевогo n — р-и-транзистор=и,".гическ1го элемента данного ра"=ряда, пер вьпъ коллек-,о;-. ко- -.э=.- . апина.- с базой второго ключ.-.-вог -. п--р-.n--.:..=. лзистора три1 гера данло. . аэр;-.:., а, а второй кл:.-,"- стор в каждом р:,çðÿäe, кроме первого„"оез"чен с базой первого ключ: — =- G "..--р-и-транзистора триггера предыдущего разряда, второй коллектор ключевого rt-p-итранзистора логического элемента первого разряда соединен с входом выходного буферного формирователя, выход которого является выходом наращивания памяти регистра.

1499405

: оставитель А. Дерюгин

Техред N, Ходанич

Корректор Л.Патаи

Редактор 11. Тупица

Заказ 4700/51 Тираж 558 Подписное

БНИИПИ Государственного.комитета по изобретениям и открытиям при ГКНТ СССР

113035, Москва, Ж-35, Раушская наб., д. 4/5

Производственно-издательский комбинат "Патент", r, Ужгород, ул. Гагарина, 101