Устройство управления для доменной памяти

Иллюстрации

Показать всеРеферат

Изобретение относится к вычислительной технике и может быть использовано при построении магнитных доменных запоминающих устройств. Целью изобретения является уменьшение энергопотребления за счет подключения только необходимых в текущий момент блоков памяти. Устройство позволяет определять, в каких конкретно блоках памяти физически расположен массив, начальный и конечный адреса которого заданы, и подключать источник питания только к этим блокам. 2 ил.

СОЮЗ СОВЕТСНИХ

СОЦИАЛИСТИЧЕСКИХ

РЕСПУБЛИН

„SU 1499407 (51) 4 С 11 С 29/00

ОПИСАНИЕ ИЗОБРЕТЕНИЯ

Н ABTOPCHOMV СВИДЕ ГЕЛЫ ТВУ

ГОСУДАРСТНЕННЫЙ НОМИТЕТ

ПО ИЗОБРЕТЕНИЯМ И ОТНРЫТИЯМ

ПРИ П.1НТ СССР (21) 4309796/24-24 (22) 03. 08.87 (46) 07.08.89. Бюл, В 29 (72) Л.И. Савельев, О. В. Росницкий, С.Б. Торотенков, В. Н. Ковалев, В.И. Косов и А.Д. Жучков (53) 681.325(088.8) (56) Авторское свидетельство СССР

И 519761, кл. G 11 С 19/00, 1976.

Авторское свидетельство СССР

Р 1053161, кл. С 11 С 11/14, 1983. (54) УСТРОЙСТВО УПРАВЛЕНИЯ ДЛЯ ДОМЕННОЙ ПАМЯТИ

Изобретение относится к вычислительной технике и может быть использовано при построении доменных магнитных запоминающих устройств.

Цель изобретения — уменьшение энергопотребления за счет подключения только необходимых в текущий момент блоков памяти.

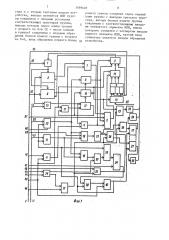

На фиг. 1 приведена функциональная схема устройства; на фиг ° 2 — алгоритм функционирования устройства.

Устройство (фиг. 1) содержит генератор 1, группу 2 управляющих входов, первый элемент И 3, первый триггер 4, второй элемент И 5, первый элемент 6 сравнения, третий элемент ИЛИ 7, группу 8 блоков памяти, группу 9 элементов И, четвертый элемент ИЛИ 10, первый 11 и второй 12 элементы ИЛИ, первый 13 и второй 14 регистры числа, третий триггер 15, вспомогательный регистр 16 адреса, первый счетчик

17, сумматор 18, второй элемент 19

2. (57) Изобретение относится к вычислительной технике и может быть использовано при построении магнитных доменных запоминающих устройств.

Целью изобретения является уменьшение энергопотребления за счет подключения только необходимых в текущий момент блоков. памяти. Устройство позволяет определять, в каких конкретно блоках памяти физически расположен массив, начальный и конечный адреса которого заданы, и подключать источник питания только к этим блокам.

2 ил. сравнения, регистры начального 20 и конечного 21 адресов, группу 22 адресных входов устройства, блок 23 полупостоянной памяти, второй триггер 24, дешифратор 25, группу 26 элементов ИЛИ, гфуппу 27 триггеров, второй счетчик 28, четвертый триггер

29, третий 30, четвертый 31 и пятый

32 элементы И, группу 33 ключей, шестой элемент И 34, вход 35 числа 4, ) устройства, входы синхроимпульса 36, считывания 37, сброса 38, управляющий

39, следующего адреса 40, начала такта 41, записи 42, признака работы с массивом 43, признака поадресной работы 44, первый тактовый 45, запуска 46, второй TBKToBbIH 47, обращения 48, конечного адреса 49, начального адреса 50, адресный 51.

Устройство работает следующим образом.

Перед началом работы с входа 38 сброса устройства подается сигнал

3 1499407

"Сброс" на входы элемента ИЛИ 10 и далее на входы группы 26 элементов

ИЛИ, триггеров 27, счетчика 28 и на первые входы регистра 20 начального адреса и регистра 21 конечного адреса, а также па входы элемента ИЛИ 11, устанавливающего триггер 4 в исходное состояние, на вход элемента

ИЛИ 12, на входы первого регистра 10

13 числа и второго регистра 14 числа, и ца вход триггера 15, sa счет которых устройство устанавливается в исходное состояние. Затем с входов

43 или 44 признака работы устройства 15 на триггер 24 поступает сигнал, определяющий работу доменной памяти с массивами информации или поадресной записи, или считывания информации, :: r

Если запись или считывание пнформации поадреспое, то на регистрах начального лдрсса 20 и конечного адреса 21 будет одинаковый код адреса. Следовательно, на выходе дешифратора 25 пе будет управляющего потенциала, а управляющий потенциал с выхода элемента 19 сравнения не проходит через элемент И 30 (этот сигнал при работе с массивами по оконча IHH работы откгпочает питание с блоков памяти). В этом режиме работы тактовый нмпульс с группы 2 входов проходит через элемент И 31 и далее через группу 26 элементов.ИЛИ поступает на входы группы 27 триггеров, за счет которых ключи 33 включают питание на все блоки 8 памяти.

При этом первый блок памяти включается за счет прохождения управлягощего потенциала на триггер 15 через эле- 40 мент И 32 °

В случае, если необходима выборка или запись массивами, то в исходном состоянии группа 27 триггеров находится в нулевом, а триггер 15 45 устанавливается в единичное состояние управлягощим потенциалом с входа

46 запуска устройства. За счет этого первый ключ группы 33 ключей подключает питание только на первый блок 8 памяти. При этом на регистре

20 начального адреса и регистре

21 конеч ного адр еса установлены коцы адресов, поступивших с шины

22 адреса. Эти адреса поступают на сумматор 18, где вычитается из конечного адреса начальный адрес, и на элемент 19 сравнения. Вычитание адресов происходит по сигналу обращения к памяти, пришедшего на третий вход сумматора 18, при этом полученный код поступает на дешифратор 25, выходной потенциал с которого через элементы ИЛИ группы 26 устанавливает тот или иной триггер группы

27 в единичное состояние. За счет этого управляющий потенциал поступает на тот или иной ключ группы

33 и подыгючается питание на дополнительный блок памяти, содержащий некоторые старшие адреса нужногО массива по отношению к начальному.

При этом при работе происходит непрерывное сравнение адресов на дополнительном элементе 19 сравнения (увеличение начального адреса происходит путем добавления единицы):

Если адреса сравниваются, то на выходе элемента 19 сравнения появится разрешающий потенциал, который поступает на первый вход элемента И 30, на другом входе которого уже присутствует разрешающий потенггиал, пришедший с трггг;гера 24. За счет этого триггер 29 устанавливается в единичное состояние и тактовые импульсы с второго тактового входа 47 устройства поступают на вход счетчика 28.

Через время, равное времени переполнения счетчика, выходной импульс с него поступает на вход элемента

ИЛИ 10 и далее на сброс группы 27 триггеров, отключающих питание с дополнителыгых блоков памяти, при этом устройство управления снова находится в исходном состоянии и гготребляет питание только за счет первого, "дежурного" блока памяти, что при больших объемах памяти существенно снижает энергопотребление запоминающего устройства в целом.

Формула изобретения

Устроиство управления для доменной памяти, содержащее группу блоков памяти, генератор импульсов, первый и второй элементы ИЛИ, первый триггер, элемент сравнежгя, первый и . второй элементы И, первый счетчик, группу элементов И, блок полупостоянной памяти, первый и;второй регистры числа, регистры начального и конечного адресов, вспомогательный регистр адреса, причем тактовые входы блоков памяти группы соединены с выходом генератора импульсов, тактовьп вход которого является входом числа, информационный вход которого

| является входом числа устройства, отличающееся тем,что, с целью уменьшения энергопотребле5 ния за счет подключения только необходимых в текущий момент блоков памяти, в него введены третий и четвертый элементы ИЛИ, элементы И с третьего по шестой, второй элемент сравнения, триггеры с второго по четвертый, группа элементов ИЛИ, группа триггеров, группа ключей, второй счетчик, дешифратор и сумматор, первый вход которого соединен с выходом регистра начального адреса и с первым входом второго элемента сравнения, второй вход которого соединен с выходом регистра конечного адреса

20 и с вторым входом сумматора, выход второго элемента сравнения соединен с первым входом третьего элемента

И, второй вход которого соединен с прямым выходом второго триггера, 25 входы сброса и установки которого являются соответственно входами при. знаков работы с массивом и поадресной работы устройства, инверсный выход второго триггера соединен с

ЗО первым входом четвертого элемента

И, второй вход которого является первым тактовым входом устройства, выход четвертого элемента И соединен с первым входом пятого элемен35 та И и с первыми входами элементов

ИЛИ группы, второй вход пятого элемента И является входом запуска устройства, выход пятого элемента И соединен с входом установки третьего триггера, вход сброса которого соединен с входом сброса устройства, вторые входы элементов ИЛИ группы соединены с соответствующими выходами дешифратора, вход которого соединен с выходом сумматора, выход третьего элемента И соединен с входом установки четвертого триггера, вход сброса которого соединен с входами сброса регистров начального и конечного адресов, второго счетчика, триггеров группы и с выходом третьего элемента ИЛИ, первый вход которого соединен с входом сброса устройства, второй вход третьего элемента ИЛИ соединен с выходом второго счетчика, счетный вход которого соединен с выходом пятого элемента И, первый и второй входы которого соединены соответственно с выходом четвертого триг5 1499407 синхроиипульса устройства, первый вход первого элемента И является входом считывания устройства, второй вход первого элемента И соединен с выходом первого .триггера и с первым входом второго элемента If. второй вход которого соединен с третьим входом первого элемента И и с выходом первого элемента сравнения, первый вход которого соединен с выходом регистра начального адреса, второй вход первого элемента сравнения соединен с выходом вспомогательного регистра адреса, вход сброса которого соединен с первыми входами первого и второго элементов ИЛИ, с входами. сброса первого и второго регистров числа и вспомогательного регистра адреса и с входом сброса устройства, информационные входы регистров конечного и начального адресов являются соответственно входами конечного и начального адресов устройства, адресный вход блока полупостоянной па- мяти является адресным входом устройства, управляющий вход блока полупостоянной памяти соединен с управляющими входами блоков памяти группы и с управляющим входом устройства, вход следующего адреса устройства соединен с тактовым входом регистра начального адреса, вход начала такта устройства соединен с вторым входом первого элемента ИЛИ, выход которого соединен с входом сброса первого триггера, вход установки которого соединен с выходом блока полупостоянной памяти и со счетным входом первого счетчика, вход сброса которого соединен с выходом второго элемента

ИЛИ, второй вход которого соединен с выходом переполнения первого счетчика и с входом записи вспомогательного регистра адреса, выход первого элемента И соединен с входом записи второго регистра числа, разряды информационного входа которого соединены с выходами соответствующих элементов И группы, первые входы которых соединены с третьим входом второго элемента И и с входом записи устройства, выход второго регистра числа соединен с четвертым входом второго элемента И, выход которого соединен с управляющим входом генератора импульсов, вторые входы элементов И группы соединены с соответствующими разрядами выхода первого регистра

1499407. ЧБ гера и с вторым тактовым входом устройства, выходы элементов ИЛИ группы соединены с входами установки соответствующих триггеров группы, выходы которых через ключи группы с второго по К-й (К - число ключей в группе) соединены с входами обращения блоков памяти группы с второго по К-й, вход обращения первого блока

Ф7

/Щ .ЧЬ

Щ

18 памяти группы соединен через первый ключ группы с выходом третьего триггера, выходы блоков памяти группы соединены с соответствующими входами четвертого элемента ИЛИ, выход которого соединен с четвертым входом первого элемента ИЛИ, третий вход сумматора является входом обращения устройства..

1499407

Тир.аж 558

Подписное

ВНИИПИ Государственного комитета по изобретениям и открытиям при ГКНТ СССР

113035, Москва, Ж-35, Раушская наб., д. 4/5

Производственно-издательский комбинат "Патент", r. Ужгород, ул. Гагарина, 101

Редактор Н.Тупица

Заказ 4700/51

Составитель И. Андреев

Техред М. Ходанич Кор р ект ор 0. Ципл е