Устройство синхронизации

Иллюстрации

Показать всеРеферат

Изобретение относится к электросвязи. Цель изобретения - увеличение быстродействия. Устройство содержит фазовый детектор 1, усилитель 2 постоянного тока, пропорционально-интегрирующий фильтр 3, сумматоры 4 и 5, управляемый генератор 6, дифференцирующий блок 7, ограничитель 8, пороговый блок 9, формирователь 10 сигналов счета, реверсивный счетчик 11, ЦАП 12 и 13, управляемые аттенюаторы 14 и 15, ключ 16, запоминающий блок 17, АЦП 18, накопитель 19, генератор 20 импульсов, измеритель 21 амплитуды и усредняющий блок 22. Цель достигается за счет обеспечения более точного соответствия между частотной расстройкой и напряжением, его устраняющим. 2 ил.

СОЮЗ СОВЕТСКИХ

РЕСПУБЛИК списочник изоврктКНил

К ASTOPCHOMY СВИДЕТЕЛЬСТВУ

ГОСУДАРСТВЕННЫЙ КОМИТЕТ

ПО ИЗОБРЮЕНИИЭ И ОТКРЫТИЯМ

ПРИ ГКНТ CCCP (21) 4341920/24-09 (22) 06.11,87 (46) 07.08 ° 89. Бюл. ¹ 29 (71) Уральский политехнический институт им. С.И. Кирова (72) В.И. Неволин (53) 621.396.662(088,8) (56) Зайцев Г.В., Стеклов В.К. Комбинированные следящие системы. — Киев:

Техника, 1978, с..263.

Авторское свидетельство СССР № 1327287„ кл. Н 03 L 7/00, 1985. (54) УСТРОЙСТВО СИНХРОНИЗАЦИИ (57) Изобретение относится к электросвязи. Цель изобретения — увеличение быстродействия. Устройство содержит,SU.„1499494 А 1 Р Н 03 L 7/02 // Н 04 . 7 02

2 фазовый детектор 1, усилитель 2 постоянного тока, пропорционально-интегрирующий фильтр 3, сумматоры и 5, управляемый генератор 6, дифференцирующий блок 7, ограничитель 8, пороговый блок 9, формирователь 10 сигналов счета, реверсивный счетчик

11, ЦАП 12 и 13, управляемые аттенюаторы 14 и 15, ключ 16, запоминающий блок 17, АЦП 18, накопитель 19, генератор 20 импульсов, измеритель

21 амплитуды и усредняющий блок 22 °

Цель достигается за счет обеспечения более точного соответствия между частотной расстройкой и напряжением, его устраняющим. 2 ил.

3 149949

Изобретение относится к электросвязи и может быть использовано в системах передачи информации.

Целью изобретения является повы- .

5 шение быстродействия.

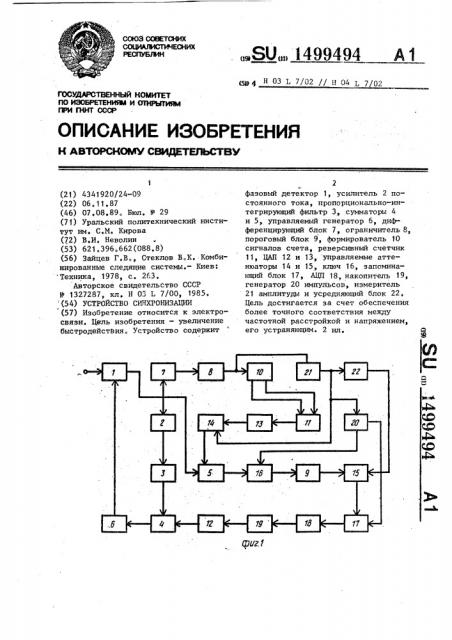

На фиг. 1 изображена структурная электрическая схема устройства синхронизации; на фиг. 2 — временные диаграммы сигналов, поясняющие работу устройства синхронизации.

Устройство синхронизации содержит фазовый детектор (ФД) 1, усилитель

2 постоянного тока (УПТ), пропорционально-интегрирующий фильтр (ПИФ) 3, 15 первый и второй сумматоры 4 и 5, управляемый генератор 6, дифференцирующий блок 7, двусторонний симметричный снизу ограничитель 8, порого, вый блок 9, формирователь 10 сигна- 20 лов счета, реверсивный счетчик (PC)

11, первый 12 и второй 13 цифроаналоговые преобразователи (ЦАП), первый

14 и второй 15 управляемые аттенюаторы, ключ 16, запоминающий блок 17, 25 аналого-цифровой преобразователь 18, накопитель 19, генератор 20 импульсов, измеритель 21 агатлитуды, усред- няющий блок 22, Устройство синхронизации работает следующим образом.

При частотном рассогласовании, меньшем полосы пропускания кольца фазовой автоподстройки (ФАП), содержащего ФД 1, УПТ 2, ПИФ 3, первый сумматор 4 и управляемый генератор 6 введение последнего в синхронный режим работы осуществляется за счет работы данного кольца ФАП.

При частотных расстройках, не 40 отрабатываемых кольцом ФАП, на выходе ФД 1 появляется напряжение би-, ений (фиг. 1 и 2а). Это напряжение имеет периодический характер, причем уже первая гармоника этого напряжения находится за пределами прозрачности ГИФ 3. Поэтому такое напряжение биений не поступает на вход управляемого генератора 6 из-за подавления в ПИФ 3 и кольцо ФАП не сраба- 5 тывает, Вследствие пилообразной характеристики ФД 1 напряжение биений содержит участки с большой крутизной, которые свидетельствуют о нал чии час» 55 тотной расстройки. Эти участки выделяются с помощью дифференцирующего блока 7 (фиг ° 2б), выходное напряжение которого имеет вид коротких нм4 пульсов одной полярности. При другом знаке частотной расстройки полярность импульсов противоположная.

С выхода дифференцирующего блока

7 импульсы поступают на ограничитель

8, форма импульсов на выходе которого подобна форме входных импульсов, но те входные импульсы, амплитуда которых меньше порогового напряжения, на выход ограничителя 8 не пройдут.

С выхода ограничителя 8 импульсы поступают одновременно в измеритель

21.и формирователь 10, который после соответствующей нормировки и преобразования подает импульсы одной полярности, например, на.суммирующий вход РС 11, а импульсы другой полярности — на вычитающий вход РС 11.

В последнем в цифровом виде накапливается информация о количестве поступивших импульсов, которая в втором ЦАП 13 преобразуется в аналоговую форму (фиг, 2в). Это напряжение ступенчатой формы с помощью первого управляемого аттенюатора 14 изменяется по величине так, чтобы после второго сумматора 5 формироьалось монотонное линейно изменяющееся напряжение (фиг. 2г),, Это напряжение поступает на ключ 16, который открывается генератором 20 на время анали- за Т. Интервал анализа определяется постоянной времени фильтра нижних ччастот или временем интегрирования интегратора в ФД 1.

Для сохранения монотонности напряжения (фиг. 2г) коэффициент передачи первого управляемого аттенюатора 14 должен устанавливаться пропорционально амплитуде биений. При этом независимо от величины частотной расстройки в конце интервала анализа Т на выходе ключа 16 — сигнал одинакового уровня. На этот уровень и настроен пороговый блок 9. После срабатывания последнего его выходное напряжение (фиг. 2д) изменяется обратно пропор-. ционально усредненной амплитуде биений во втором управляемом аттенюаторе 15, Затем это напряжение, величина которого пропорциональна начальной частотной расстройке, запоминается в запоминающем блоке 17.

Далее аналоговое напряжение переводится в цифровую форму с помощью аналого-цифрового преобразователя 18 и накапливается в накопителе 19. Выходной код последнего содержит инфор5 14 мацию о всех изменениях частотной расстройки, происходящих с момента включения устройства синхронизации.

С помощью первого ЦАП 12 цифровой код накопителя 19 преобразуется в аналоговое напряжение, которое суммируется в первом сумматоре 4 с напряжением ошибки ФАП и управляет частотой управляемого генератора 6.

Работа ключа 16, запоминающего блока 17 синхронизируется генератором 20, который формирует стробирующий импульс (фиг, 2е) длительностью

Т и импульс фиксации запоминающего блока 17 (фиг. 2ж) длительностью.1„, которая выбирается из условия выполнения всех операций, связанных с перестройкой частоты управляемого генератора 6, Генератор 20 работает в ждущем режиме и запускается от измерителя 21, который представляет собой фиксатор амплитуды с соответствующим нормированием выходного напряжения (фиг ° 2з). Так как пороговый блок запускается только при наличии биений, то и запуск генератора 20 происходит, в основном, при наличии частотной расстройки.

Для повышения точности установки частоты управляемого генератора 6 при действии помех коэффициент передачи второго управляемого аттенюатора 15 устанавливается напряжением с усредняющего блока 22, который вырабатывает напряжение, среднее за период анализа Т, чем и обеспечивается более точное соответствие между частотной расстройкой и напряжением, его устраняющим. !

Формула изобретения

99494 6

Устройство синхронизации, содержащее последовательно соединенные накопитель, первый цифроаналоговый преобразователь, первый сумматор, управляемый генератор, фазовый детектор, усилитель постоянного тока и пропорционально-интегрирующий фильтр, выход которого подсоединен к второму входу первого сумматора, 5 последовательно соединенные формирователь сигналов счета, реверсивный счетчик и второй цифроаналоговый преобразователь, а также дифферен10. цирующий блок и второй сумматор, входы которых подключены к выходу фазового детектора, аналого-цифровой преобразователь и генератор импульсов, причем второй вход фазового детектора явяяется входом устройства, о т л и ч а ю щ е е с я тем, что, с целью повышения быстродействия, введены последовательно соединенные двусторонний симметричный снизу or20 раничитель, измеритель амплитуды и первый управляемый аттенюатор, выход которого подсоединен к второму входу второго сумматора, последовательно соединенные усредняющий блок, 25 второй управляемый аттенюатор и запоминающий блок, выход которого через аналого-цифровой преобразователь подсоединен к входу накопителя, последовательно соединенные ключ и пороговый блок, выход которого подсоединен к информационному входу второго управляемого аттенюатора, при этом выход измерителя амплитуды подсоединен к входам усредняющего

35 блока и генератора импульсов, первый и второй выходы которого подсоединены соответственно к управляющим входам запоминающего блока и ключа, информационный вход которого подключен

40 к выходу второго сумматора, вход и выход двустороннего симметричного снизу ограничителя подключены соответственно к выходу дифференцирующего блока и входу формирователя сигналов

45 счета,. а выход второго цифроаналогового преобразователя подсоединен к информационному входу первого управляемого аттенюатора.

1499494

Составитель В. Орлов

Техред М. Дщык

Корректор М. Шароши

Редактор И. Шулла

Заказ 4707/55 Тираж 884 Подписное

ВНИИПИ Государственного комитета по изобретениям и открытиям при ГКНТ СССР

113035, Москва, Ж-35, Раушская наб., д. 4/5

Производственно-иэдательский комбинат "Патент", г. Ужгород, ул. Гагарина, 101