Устройство для исправления ошибок в кодовой комбинации

Иллюстрации

Показать всеРеферат

Изобретение относится к электросвязи. Цель изобретения - повышение помехоустойчивости. Устройство содержит усилитель 1 с регулируемым коэффициентом усиления, усилитель 2 с постоянным коэффициентом усиления, компаратор 3, ключи 4 и 9, сумматор 5, блок 6 сравнения,пороговые блоки 7 и 8, элементы ИЛИ 10 и 15, накопитель 11, сумматоры 12 и 14 по модулю два, элемент И 13 и блок 16 обнаружения ошибок. При обнаружении ошибок формируется и передается сигнал переспроса на повторную передачу. Для уменьшения числа потерь, возникающих в случае искажения двух повторений, обеспечивается исправление ошибки во втором повторении комбинации путем формирования сигналов "стирания". Устройство по п.2 формулы отличается выполнением порогового блока 8.1 з.п.ф-лы, 3 ил.

СОЮЗ СОВЕТСКИХ

СОЦИАЛИСТИЧЕСКИХ

РЕСПУБЛИК (gg 4 Н 03 М 13/02

0ПИСЛНИК ИЗОБРКТКНИЯ

К АВТОРСКОМ .Ф СВИДЕТЕЛЬСТВУ

ГОСУДАРСТВЕННЫЙ КОМИТЕТ

ПО ИЗОБРЕТЕНИЯМ И ОТКРЫТИЯМ

ПРИ ГКНТ СССР (61) 1324089 (21) 4262051/24-09 (22) 15.06.87 (46) 07.08.89. Бюл. Р 29 (72) Ю.И. Николаев, О.Н. Жуков, О.П. Малофей, С.В. Науменко и Л.С. Сорока (53) 62!.394.441(088.8) (56) Авторское свидетельство СССР

Р 1324089, кл. Н 03 М 13/02, 1986. (54) УСТРОЙСТВО ДЛЯ ИСПРАВЛЕНИЯ

ОШИБОК В КОДОВОЙ КОМБИНАЦИИ (57) Изобретение относится к электросвязи. Цель изобретения — повьппение помехоустойчивости. Устройство содержит усилитель 1 с регулируемым коэффициентом усиления, усилитель 2

„.БЦ„„14995ОЗ А 2

2 с постоянным коэффициентом усиления, компаратор 3, ключи 4 и 9, сумматор

5, блок 6 сравнения, пороговые блоки 7 и 8, элементы ИЛИ !О и 15, накопитель 11, сумматоры 12 и 14 по . модулю два, элемент И 13 и блок 16 обнаружения ошибок. При обнаружении ошибок формируется и передается сигнал переспроса на повторную передачу. Для уменьшения числа потерь, возникающих в случае искажения двух повторений, обеспечивается исправление ошибки во втором повторении комбинации путем формирования сигналов стирания. Устройство по п. 2.формулы отличается выполнением пороговоЯ го блока 8. 1 з.п.ф-лы, 3 ил., 1 табл.

149

Уровни сигнала

Выход ервого второго омпа- компаатора ратора

0 21 второго порогового блока 8

А

Б

1

Изобретение относится к электросвязи, может быть использовано в системах передачи дискретной информации с решающей обратной связью и является усовершенствованием изобретения по авт,св. Р 1324089.

Целью изобретения является повышение помехоустойчивости.

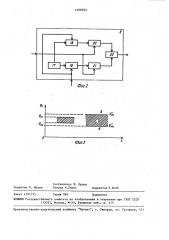

На фиг. 1 представлена структурная электрическая схема устройства для исправления ошибок в кодовой комбинации; на фиг. 2 — структурная электрическая схема второго порогового блока; на фиг. 3 — временные диаграммы сигналов, поясняющие работу устройства для исправления ошибок в кодовой комбинации.

Устройство для исправления ошибок в кодовой комбинации содержит усилитель 1 с регулируемым коэффициентом усиления, усилитель 2 с постоянным коэффициентом усиления, компаратор 3, первый ключ 4, сумматор 5, блок 6 сравнения, первый 7 и второй 8 пороговые блоки, второй ключ 9, первый элемент ИЛИ 10 накопитель ff первый сумматор 12 по модулю два, элемент И 13, второй сумматор 14 по модулю два, второй элемент ИЛИ 15, блок 16 обнаружения ошибок.

Второй пороговый блок. 8 содержит блок 17 опорного напряжения, первый

18 и второй 19 управляемые усилители, первый 20 и второй 21 компараторы и сумматор 22 по модулю два.

Устройство для исправления ошибок в кодовой комбинации работает следующим образом.

Принимаемая кодовая комбинация подается на первый 7 и второй 8 пороговые. блоки и усилители 1 и 2 (фиг. 1), Усиленный в W pas с выхода усилителя сигнал Y(n)W(n) поступает на вход компаратора 3, где производится сравнение произведений 7(п)1((п) с опорным сигналом. По результатам сравнения компаратор 3 управляет ключом 4, разрешая прохождение сигнала gÄY(n) с выхода усилителя 2, либо инверсно, либо неинверсно, т.е, определяет знак произведения p„V(n).

Полученный сигнал одновременно с

1 сигналом с выхода усилителя f поступают соответственно на первый и второй входы сумматора 5, на выходе которого в зависимости от знака произведения р Y(n) получается разность

h или сумма Y(n) N(n) +p„Y(n), которая

9503 4 поступает на блок 6 сравнения, где сравнивается .с сигналом, поступающим на него с выхода усилителя 1. На вы5 ходе блока 6 сравнения в случае действия в канале связи нестационарной помехи получается уровень, который пропорционален интенсивности помех.

Напряжение на выходе блока 6 срав1p нения регулирует коэффициент усиления усилителя 1, уровень порога в первом пороговом блоке 7 и поступает на дополнительный вход второго порогового блока 8, 15 Блок 8 работает следующим образом.

С дополнительного входа второго порогового блока 8 (фиг. 2) сигнал управления поступает на управляющие входы первого 18 и второго 19 управ20 ляемых усилителей 18 и 19, на информационные входы которых подаются опорные напряжения U „,,и U!, (фиг. 3) с выходов блока 17 опорного напряжения. На выходах первого 18 и второго

19 управляемых усилителей, уровни

U „„ U „ изменены в соответствии ( с управляющим сигналом (в данном случае ширина полосы стираний увеличена).

30 Далее уровни U H U „ „подаются на первый 20 и второй 21 компараторы, где сравниваются с входным сигналом. Работа компараторов пояснена в таблице, где А, Б, В - уровни сиг- нала (фиг. 3). !

Таким образом, на выходе второго порогового блока 8 сигнал появляется только тогда, когда при сравнении уровней порогов и сигнала последний находится в интервале стираний, что соответствует о некачественно принятом символе, С выхода первого порогового бло- .

I ка 7 комбинация в виде последовательности нулей и единиц через второй ключ 9 и первый. элемент ИЛИ 10 запи5 14995 сывается в накопитель 11, через второй элемент ИЛИ 15 комбинации вводится в блок 16 обнаружения ошибок.

В случае необнаружения ошибок блок

16 обнаружения ошибок разрешает выда- чу комбинации из накопителя 11 на информационный выход устройства для исправления ошибок в кодовой комбинации, 10

В случае обнаружения ошибок блок

16 обнаружения ошибок формирует и передает сигнал переспроса на повторную передачу. При этом информационный вход второго ключа 9 переключает- 16 ся с первого выхода второго ключа 9, связанного с первым элементом ИЛИ 10, на второй выход второго ключа 9, связанного с первым 12 и вторым 14 сумматорами. Принятая комбинация второ- 20 го повторения с второго выхода второго ключа 9 через второй сумматор

14 и первый элемент ИЛИ 10, осуществляя последовательный сдвиг первого повторения в первый суьжатор 12, запи-25

- сывается в накопитель 11, а через второй элемент ИЛИ 15 поступает в блок 16 обнаружения ошибок. Если ошибка не обнаружилась, то информация из накопителя 11 выдается полу- 30 чателю. Для уменьшения числа потерь, возникающих в случае искажения обоих повторений, обеспечивается исправление ошибки.во втором повторении комбинации. Для этого на первом сумматоре 12 происходит поразрядное сравнение обеих комбинаций при одновременном выявлении вторым пороговым блоком 8 ненадежных элементов (стираний) второго повторения. ре- 40 зультат сравнения поступает на элемент И 13, на который также выдаются сигналы стирания, формируемые вторым пороговым блоком 8, Инверти03 6 рование разрядов комбинации второго повторения на первом сумматоре 12 происходит в том случае, когда на первом и втором входах элемента

И 13 одновременно появляются сигнал несовпадения двух повторений, формируемый первым сумматором 12, и сигнал стирания выявлений вторым пороговым блоком 8. В абсолютном большинстве случаев это соответствует исправлению искаженной комбинации.

Формула изобретения (1, Устройство для исправления ошибок в кодовой комбинации по авт. св. Р 1324089, о т л и ч а ю щ ее с я тем, что, с целью повышения помехоустойчивости, выход блока сравнения подсоединен к дополнительному входу второго порогового блока.

2. Устройство по п. 1, о т л ич а ю щ е е с я тем, что второй пороговый блок содержит последовательно соединенные блок опорного напряжения, первый управляемый усилитель, первый компаратор и сумматор по модулю два, последовательно соединенные второй управляемый усилитель и второй компаратор, выход которого подсоединен к второму входу сумматора по модулю два, информационный вход второго управляемого усилителя подключен к второму выходу блока опорного напряжения, причем объединенные вторые входы первого и второго компараторов, объединенные управляющие входы первого и второго управляемых усилителей и выход сумматора по мьдулю два являются соответственно входом, дополнительным входом и выходом второго порогового блока.

1499503

Составитель В. Орлов

Техред N.Äèäûê Корректор Т. Колб

Редактор И. Шулла.

Заказ 4707/55

Тираж 884

Подписное

ВНИИПИ Государственного комитета по изобретениям и открытиям при ГКНТ СССР

113035, Москва, Ж-35, Раушская наб., д. 4/5

Производственно-издательский комбинат "Патент", г. Ужгород, ул. Гагарина, 101