Регистрирующее устройство

Иллюстрации

Показать всеРеферат

Изобретение относится к устройствам регистрации информации на электрочувствительной бумаге в виде графиков и таблиц. Цель изобретения - упрощение устройства. Устройство содержит группы элементов ИЛИ, включенные между первой и второй ступенями дешифраторов младших и старших разрядов, расширитель 16 импульсов меток времени, элемент И 15 и два элемента НЕ 14 и 18. Схема включения меток времени по шине 17 через расширитель 16 импульсов и элемент И 15 и синхроимпульсов по шине 13 через элемент НЕ 14 и элемент И 15 на входы группы 3.1-3.4 элементов ИЛИ позволила сократить аппаратурные затраты и упростить устройство. 1 ил.

СОЮЗ СОВЕТСНИХ

СОЦИАЛИСТИЧЕСНИХ

PECflVS JlHH

А1

„.ЯО„„1500830

{51)4 G 01 D 15/08

ОПИСАНИЕ ИЗОБРЕТЕНИЯ

H АВТОРСКОМ,Ф СВИДЕТЕЛЬСТВУ

1(с

f.n

ГОСУДАРСТВЕННЫЙ НОМИТЕТ

flO ИЗОБРЕТЕНИЯМ И ОТКРЫТИЯМ

ПРИ ГКНТ СССР (21) 4177579/24-10 (22) 10.11..86 (46) 15.08.89. Бюл. И 30 (72) И.Г.Полищук и Н.А.Шарова (53) 681.84(088.8) (56) Регистрирующее устройство Гуl

БИ.044.003 ТО, 1986. (54) РЕГИСТРИРУЮЩЕЕ УСТРОЙСТВО (57) Изобретение относится к устройствам регистрации информации на электрочувствительной бумаге в виде графиков и таблиц. Цель изобретения упрощение устройства. Устройство содержит группы элементов ИЛИ, включенные между первой и второй ступенями дешифраторов младших и старших разрядов, расширитель 16 импульсов меток времени, элемент И 15 и два элемента НЕ 14 и 18. Схема включения меток времени по шине !7 через расширитель 16 импульсов и элемент И 15 и синхроимпульсов по шине 13 через элемент НЕ 14 и элемент И 15 на вхо,ды групп 3.1-3.4 элементов ИЛИ позврлила сократить аппаратурные затраты и- упростить устройство. ил.

3 150083

Изобретение относится к устройст- вам информации на электрочунстнительной бумаге в виде графиков, таблиц и предназначено для совместного использования с устройствами обработки информации.

Целью изобретения является упрощение устройства.

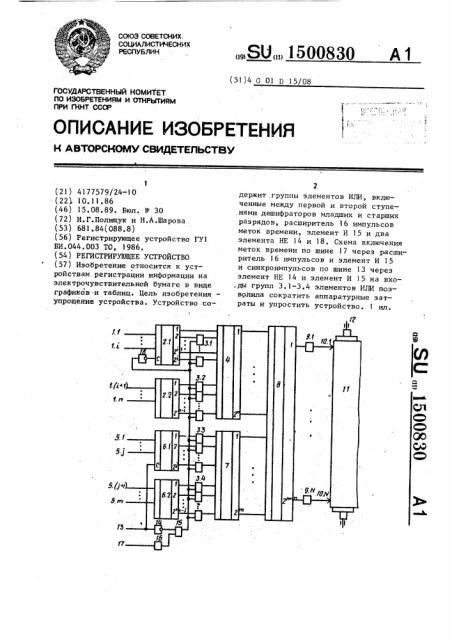

На чертеже показана структурная схема устройстна.

Устройство содержит входы 1 младших разрядов, соединенные с входами первой 2.1 и втррой 2.2 частей пер-. вой ступени дешифратора младших pas- 15 рядов, часть выходон которых непосредственно, а остальные через группы 3,1, 3.2 элементов ИЛИ соединены с входами второй ступени 4 дешифрато-, ра младших разрядов. Входы 5 старших 20 разрядов соединены с входами первой

6.1 и второй 6.2 частей первой ступени дешифраторов старших разрядов, выходы которых через группы 3.3, 3.4 элементов ИЛИ подключены к входам, 25 второй. ступени 7 дешифратора старших разрядов.

Выходы дешифраторов младших и старших разрядов соединены с входами выходного дешифратора 8, к выходам 30 которого подключены через формирователи 9 тока пишущие электроды 10, устанонленные через токочувствительную бумагу 11 на металлический валик 12. Шина 13 синхронизации сое- 35 динена со стробирующим входом первой части 6.1 первой ступени дешифратора старших разрядов и через второй элемент НЕ 14 — с одним входом эле-...:. мента И 15, к другому входу которо- 40

ro через расширитель 16 импульсов . подключена шина 17 меток времени, а выход элемента И 15 соединен с вторыми входами элементов ИЛИ и через первый элемент НЕ 18 — со стробирую- 45 щим входом первой части 2.1 первой ступени дешифратора младших разрядов.

Для возбуждения тока в пишущих электродах 10 поступающий (n+m)разрядный двоичный код (n и m - чис50 ло младших и старших разрядов соответственно) с помощью дешифраторов

2, 4, 6-8 преобразуется в Б-позиционный код (Б - число уровней кванто-, вания), причем дешифратор младших разрядов имеет 2 выходов, дешифратор старших разрядов — 2 выходов, а

1+ Я выходной дешифратор М = 2" выходов, т.е. номер возбуждаемого выхода де0 4 шифратора определяется произведением порядковых номеров возбужденных выходов дешифраторон младших и старших разрядов.

При приходе синхроимпульса и импульса меток времени н разные моменты элемент И 15 закрыт, .дешифраторы младших и старших разрядов формируют сигналы по поступающему (n+m)разрядному коду и через выходной дешифратор, формирователь 9 и пишущий электрод 10 на бумаге 11 регистрируется точка, соответствующая значению входной информации. В момент поступления импульса метки синхроимпульс отсутствует, элемент И 15 разрешен и импульс метки поступает на входы вторых ступеней дешифраторон 4, 7 младших и старших раэрядон. Сигналы появляются одновременно на всех выходах дешифратора 7 и на четных выходах дешифратора 4, и выходной дешифратор 8 формирует импульсы на всех четных выходах. На бумаге 11 появляется вертикальная линия. Через элемент НЕ 18 импульс метки времени во время регистрации метки запрещает работу первой части 2.1 первой ступени,дешифратора во избежание появления на бумаге лишних точек.

При совпадении метки времени с синхроимпульсом сопровождающий информацию синхроимпульс с шины 13 через элемент НЕ 14 запрещает..прохождение через элемент И 15 импульса метки времени. Для регистрации метки времени, поступающей одновременно с синхроимпульсом на шину 17, импульс метки через расширитель 16 поступает-. на элемент И 15, разрешенный с выхода элемента НЕ 14 после окончания синхроимпульса.

Формула изобретения

Регистрирующее устройство, содер-. жащее двухступенчатые дешифраторы младших и старших разрядов, каждый иэ которых состоит иэ двух частей, входы которых соединены с информационными входами устройства; а выходы подключены к входам выходного дешифратора, выходы которого через формирователи тока соединены с пишущими электродами, контактирующими с электрочувствительным носителем информации, шину синхронизации, подключейную к стробирующему входу первой части первой ступени дешифратора

Составитель Д.Шилин

Тех р ед М . Дидык

Корректор Т.Палий

Редактор И.Рыбченко

Заказ 485)/34

Тираж ббО

Подписное

ННИИПИ Государственного комитета по изобретениям и открытиям при ГКНТ СССР

113035, Москва, Ж-35, Раушская наб., д. 4/5

Производственно-издательский комбинат "Патент", г.ужгород, ул. Гагарина,101

5 150 старших разрядов, шину меток времени, о т л и ч а ю щ е е с я тем, что, с целью упрощения устройства, в него введены четыре группы элементов ИЛИ; два элемента НЕ, элемент И и расширитель импульсов, при этом нечетные выходы первой части первой ступени дешифратора младших разрядов непосредственно и четные выходы через элементы ИЛИ первой группы подключены к соответствующим входам дешифратора второй ступени младших разрядов, другие соответствующие входы которого соединены через элементы

ИЛИ второй группы с выходами второй части первой ступени дешифратора

0830 6 младших разрядов, выходы первой и второй частей ступени дешифратора старших разрядов подключены через элементы ИЛИ соответственно третьей

5 и четвертой групп к соответствующим входам второй ступени дешифратора старших разрядов, другие входы элементов ИЛИ четырех групп соединены через первый элемент НЕ со стробирующим входом первой части первой ступени дешифратора младших разрядов и с выходом элемента И, один вход которого через второй элемент НЕ соединен с шиной синхронизации, а другой вход через расширитель импульсов подключен к шине меток времени.