Функциональный преобразователь

Иллюстрации

Показать всеРеферат

Изобретение относится к вычислительной технике и предназначено для использования в системах управления гибкими автоматизированными производствами, технологическими процессами, в специализированных вычислительных устройствах. Целью изобретения является расширение класса решаемых задач. Для достижения поставленной цели в устройство введены одноразрядный блок памяти, дешифратор, блок узлов памяти, третий коммутатор, третий триггер, четвертый и пятый элементы И, третий счетчик. Дополнительно введенные элементы позволяют реализовать функциональное преобразование заданного числа непрерывных строго монотонных функций путем использования записанных в узлы памяти блока локальных трендов воспроизводимых функций. Расширение класса решаемых задач достигается при незначительном увеличении оборудования и сохранении высоких точностно-временных характеристик. Алгоритм преобразования состоит из двух этапов. На первом этапе развертка функции осуществляется увеличенным шагом в некотором среднем разряде с использованием локальных трендов этого разряда и приращение функции реализуется квантами. На втором этапе ведется развертка мелким шагом в младшем разряде. 1 ил.

СОЮЗ СОВЕТСНИХ.

СОЦИАЛИСТИЧЕСНИХ

РЕСПУБЛИН

ÄÄSUÄÄ 1501021 (51)4 G 06 F 1/02 е

ОПИСАНИЕ ИЗОБРЕТЕНИЯ

К А ВТОРСКОМУ СВИДЕТЕЛЬСТВУ

ГОСУДАРСТВЕННЫЙ НОМИТЕТ . ПО ИЗОБРЕТЕНИЯМ И ОТНРЫТИЯМ

ПРИ ГКНТ СССР (21) 4375508/24-24 (22) 05.02.88 (46) 15..08.89. Бюл. № 30 (71) Гомельский конструкторско-технологический и экспериментальный институт по техническому перевооружению и подготовке производства (72) Г.И.Кашалов (53) 681.325 (088.8) (56) Авторское свидетельство СССР . № 1171774, кл. G 06 F 1/02, 1983.

Авторское свидетельство СССР

¹ 1300466, кл. G 06 F 7/552, 1985. (54) ФУНКЦИОНАЛ >НЫЙ ПРЕОБРАЗОВАТЕЛЪ (57) Изобретение относится к вычислительной технике и предназначено для использования в системах управления гибкими автоматизированными производствами, технологическими процессами, в специализированных вычислительных устройствах. Целью изобретения является расширение класса решаемых задач. Для достижения поставленной цеУстройство относится к области вычислительной техники и предназначено для использования в системах управления гибкими автоматизированными производствами, технологическими процессами, в специализированных вычислительных устройствах.

Целью изобретения является расширение класса решаемых задач за счет возможности преобразования заданного числа непрерывных монотонных функций.

2 ли в устройство ввецены одноразрядный блок памяти, дешифратор, блок узлов памяти, третий коммутатор, третий триггер, четвертый и пятый элементы И, третий счетчик. Дополнительно введенные элементы позволяют реализовать функциональное преобразование заданного числа непрерывных стро1

ro монотонных функций путем использо— вания записанных в узлы памяти блока локальных трендов воспроиз водимых функций..Расширение класса решаемых задач достигается при незначительном увеличении оборудования и сохранении высоких точностно-временных характеристик. Алгоритм преобразования сос- а тоит из двух этапов. На первом этапе

6 развертка функции ссуцесз вяяется уве- Q) личенным шагом в некотором среднем разряде с использованием локальных ( трендов этого разряда и приращение функции реализуется квантами. На втоЬаава ром этапе ведется развертка мелким шагом в младшем разряде. 1 ил.

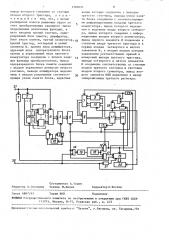

На чертеже представлена функциональная схема преобразователя.

Устройство содержит одноразрядный блок 1 памяти, дешифратор 2, блок 3 узлов памяти, коммутатор 4, сумматор

5, коммутаторы 6, 7, сумматор 8, регистры 9, 10, схему 11 сравнения, счетчик 12, триггер 13, элемент ИЛИ

14, триггер 15, генератор 16 импульсов, элементы И 17 и 18, счетчик 19, регистр 20, элементы 21-23 задержки, элемент Н 24, элемент и. 1И 25, триггер 26, элементы И 27 и 28, счетчик

3 150102

29, тактовый вход 30 устройства, вход

31 задания функции устройства. Первый сумматор 8 вьп«олнен комбинационным, а второй 5 — накапливающим.

B общем виде метод преобразования непрерывно строго монотонных функций запишется следующим образом:

L+(p+1) = L+(p) +а 8,.(р)

p+t 10 этап 1 с, = r. ? (и), о=о

F(t ) = F(tp„) + sign (г) 2

1„()+1) = L (ð+1) /2 = Ср+,, этап 2 Г 3+1 t р + L (j + 1) >

F(t. ) F(t ) + sign (r) 2 где r 1 — для строго монотонно возрастающих -функций и r -1 - для 20 строго монотонно убывающих функц«п" .

Начальные значения L (o) = d Мо;

d4 S (о) = Л с, где и ср и Л «p — конеч««ые разности взаимообратной функции ф (t) на равномерной сетке с шагом 2 . В качестве начального значения функции берется ее значение

F(t,) .

Йомер q разряда, в котором осуществляется развертка с увеличенным 30 шагом, определяется иэ выражения (Z1 V p„)

q ) 3=1 — »g (— — — — — -) г 1 +< э

1. p+1 где a « + « конечные ра

Ф z ФФ1 ти первого и второго порядка взаимнообратной функции ф(с) на равномерных сетках соответственно с шагами 2 «и

2 1. На практике достаточно проверить условие в тех узлах сетки, где 40 функция F(t) имеет наибольшую кривизну.

Для непрерывных строго монотонных функций как правило q y 1 - - (, где

) $ — целое с избытком.

Устройство работает следующим образом.

В исходном состоянии регистр 9 и сумматор 5 записан двоичный код интервала постоянства 1.<(o), счетчики

12 и 19, .триггеры 13, 15, 26 обнулены.

Первый счетньп» импульс с входа 30 устройства поступает на счетчик 12, 1 увеличивая его содержимое на 2, и через элемент ИЛИ 14 на счетный вход триггера 15, переключая его в единицу. Пройдя элемент 21 задержки, счет1

4 ный импульс сбрасывает в ноль младшие (3 — q) разряды счетчика 19. Единица с прямого выхода триггера 15 поступает на входы элементов И 17 и 18.

Элеме1«т И 18 открыт сигналом "1" с инверсного выхода триггера 13.

Код функции поступает с входа 31 устройства на дешифратор 2 и коммутатор 4. Код с выхода дешифратора 2 поступает на входы разрешения- блока

3 узлов памяти и разрешает считывание информации с j-го узла, в котором записаны локальные тренды j-й преобразуемой функции. B коммутаторе 4 код с входа 31 управляет передачей на вход сумматора 5 локальных трендов с j-го узла блока 3.

Тактовые импульсы генератора 16 импульсов, пройдя открытый элемент И

18, поступают на вход пересчета с ве" сом 2 счетчика 19, увеличивая его

-% содержимое на 2 . Кроме того, такToBbIe H n nbob« crepes oTKpblTblH сигналом "1" с инверсного выхода триггера

26 элемент И 27 поступают на счетный вход счетчика 29, увеличивая его со«держимое на "1". По заднему фронту тактового импульса счетный триггер 26 переключается в "1". Считанное из

j-го узла значение очередного локального тренда q-ro разряда поступает через коммутатор 4 на вход сумматора 5. Следующий тактовый импульс поступает через открытый сигналом "1" с прямого выхода триггера 26 элемент

И 28 на тактирукиций вход сумматора 5, в котором осуществляется вычисление очередного интервала постоянства

L „(р+1) .

По заднему фронту токтового импульса триггер 26 изменяет свое состояние на противоположное, осуществляя пересчет тактовых импульсов по модулю 2.

Код с выхода сумматора 5 поступает через коммутатор 6 на вход второго слагаемого сумматора 8, на вход первого слагаемого которого поступает код с выхода регистра 9. В результате выполнения операции сложения на выходе сумматора 8 появляется двоичньл код аргумента t . В схеме 11 сравнения код с выхода сумматора 8 сравнивается с кодом аргумента

6 поступающим с выхода счетчика 12.

Если t 1 (е, то на выходе схеВ мы 11 сравнения остается ноль. В этом

10? 1

5 150 случае в регистр 10 записывается код с выхода сумматора 8. При развертке с увеличенным шагом н регистр 9 запи— сывается код с ныхода сумматора 8 независимо от результата сраннения.

При появлении на выходе схемы 11 сравнения единицы тригrep 13 переключается в единицу и ноль с его инверс ного выхода закрывает элемент И 24 и в регистре 10 остается прежнее значение суммы интервалов постоянства

q-ro разряда.

Реализуется переход ко второму этапу преобразования, т.е. к развертке мелким шагом. Тактовые импульсы через открытый сигналом с прямого выхода триггера 13 элемент И 17 посту-Л пают на вход пересчета с весом 2 счетчика 19. На вход первого слагаемого сумматора 8 поступает через коммутатор 7 код с выхода регистра 10, а на вход второго слагаемого поступает сдвинутый в коммутаторе 6 на (3 — q) разрядов в сторону младших .код (р+1)-го интервала постоянства

q-ro разряда. B результате выполнения н сумматоре 8 операции сложения на

его выходе появляется код аргумента который сравнивается в схеме 11

У сравнения с кодом выхода счетчика 12.

Код аргумента t . записывается в ре,1+2 гистр 10. В это время в регистр 20 осуществляется запись содержимого счетчика 19. Синхронизация записи в регистры 10 и 20 осуществляется импульсами с выхода второго элемента

ИЛИ 25. Второй этап преобразования осуществляется до тех пор, пока на выходе схемы 11 сравнения не появится единица. Тогда триггер 13 переключается в ноль, переключая в свою очередь триггер 15, ноль с прямого выхода которого закрывает элементы И

17 и 18. На этом вычисление текущего значения непрерывной строго монотонной функции F(t) заканчивается, ее значение записано в регистр 20.

При поступлении следующего счетного импульса на вход 30 устройства повторяется описанньп вычислительный процесс.

Формул а изобретения

Функциональный преобразователь, содержащий два счетчика, два суммато. ра, два коммутатора, схему сравнения, три регистра, два триггера, генератор

55 импульсов, два элемента ИЛИ, три элемента И, три элемента задержки, причем тактовый вход преобразователя соединен с первыми входами первого элемента ИЛИ, перно го элемента э адержки и счетным входом первого счетчика, выход которого соединен с первым входом схемы сравнения, второй вход которой подключен к выходу первого сумматора и информационным входам первого и второго регистров, соединенных выходами соответственно с первым и вторым информационными входами первого коммутатора, выход которого соединен с входом первого слагаемого первого сумматора, вход второго слагаемого которого подключен к выходу второro коммутатора, управляющие входы первого и нторого коммутаторов соединены с прямым выходом первого триггера, счетный вход которого подключен к выходу схемы сравнения, инверсный выход первого триггера соединен с первым входом первого элемента И, к второму и третьему входам которого подключены соответственно пря-, мой выход второго триггера и выход генератора импульсов, подключенный к ° первому входу второго элемента И, второй и третий входы которого соединены с прямыми выходами соответственно первого и второго триггеров, выходы первого и второго элементов И подключены к счетным входам второго

-л счетчика с весами соответственно 2 и 2, где и†разрядность аргумента, q — номер разряда, с которого ведется развертка с увеличенным шагом, выход второго счетчика соединен с информационным входом третьего регистра, выход второго элемента И соединен через второй элемент задержки с первым входом второго элемента ИЛИ, подключенного выходом к входу синхронизации второго регистра, выход первого элемента И подключен через третий элемент задержки к входу синхронизации первого регистра и первому входу третьего элемента И, второй вход которого соединен с инверсным выходом первого триггера, выход третьего элемента И соединен с вторым входом второго элемента ИЛИ, выход первого элемента эапержки подключен к,входу установки н 0" младших 3-q разрядов второго счетчика, прямой выход первого триггt ра соединен с вторым входом неpBGr элемента ИЛИ, / 150102 1 8 выход которого соединен со счетным

Составитель А.Зорин

Редактор О.Спесивых Техред М.Дилык Корректор Л. Бескид

Тираж 668

Заказ 4867/43

Подписное

ВНИИПИ Государственного комитета по изобретениям и открытиям при ГКНТ СССР

113035, Москва, Ж-35, Раушская наб., д. 4/5

Производстие. но- издательский комбинат "Патент", r.Óæãîðîä, ул. Гагарина, 101 входом второго триггера, о т л и— ч а ю шийся тем, что, с целью расширения класса решаемых задач за

5 счет преобразования заданного числа непрерывных монотонных функций, в него введены третий счетчик, одноразрядный блок памяти, дешифратор,, блок узлов памяти, третий коммутатор, 10

I третий триггер, четвертый и пятый элементы И, причем вход дешифратора, адресный вход одноразрядного блока памяти и управляющий вход третьего коммутатора соединены с входом задания функции преобразователя, выход одноразрядного блока памяти соединен с входом управления реверсом второго счетчика, выходы дешифратора подклю, чены к входам разрешения соответст- 20 вующих узлов памяти блока, адресные входы которых соединены с выходом третьего счетчика, выходы узлов памяти блока соединены с соответствующими информационными входами третьего коммутатора, выход которого подключен к кодовому входу второго сумматора, выход которого соединен с информационным входом второго коммутатора, выход первого элемента И подключен к счетному входу третьего триггера и к первым входам четвертого и пятого элементов И, к вторым входам которых подключены соответственно прямой и инверсный выходы третьего триггера, выходы четвертого и пятого элементов

И соединены соответственно со счетным входом третьего счетчика и тактовым входом второго сумматора, выход второго элемента ИЛИ подключен к входу синхронизации третьего регистра.