Многоканальное устройство для ввода аналоговых данных

Иллюстрации

Показать всеРеферат

Изобретение относится к измерительной и вычислительной технике и может быть использовано в системах сбора данных и обработки аналоговой информации. Целью изобретения является повышение быстродействия устройства за счет совмещения во времени процессов кодирования информации и чтения данных при любом варианте распределения по диапазону значений входных аналоговых сигналов. Устройство содержит первый счетчик 1, первый цифроаналоговый преобразователь 2, каналы 3 ввода аналоговых данных, блок 4 формирования приоритетного адреса, второй цифроаналоговый преобразователь 5, блок 6 управления эталоном, первый блок 7 элементов И, первый элемент ИЛИ 8, аналоговый сумматор 9, третий цифроаналоговый преобразователь 10, первый компаратор 11, второй элемент ИЛИ 12. Указанная цель достигается за счет введения второго цифроаналогового преобразователя 5, блока 6 управления эталоном, первого блока 7 элементов И, первого элемента ИЛИ 8, аналогового сумматора 9, третьего цифроаналогового преобразователя 10, первого компаратора 11 и второго элемента ИЛИ 12. 6 ил.

СОЮЗ СОВЕТСНИХ

СОЦИАЛИСТИЧЕСКИХ

РЕСПУБЛИК (59 4 G 06 F 3/05

ОПИСАНИЕ ИЗОБРЕТЕНИЯ

К А STOPCHOMY СВИДЕТЕЛЬСТВУ в. л

ГОСУДАРСТВЕННЫЙ КОМИТЕТ, ПО ИЗОБРЕТЕНИЯМ И ОТНРЫТИЯМ

ПРИ ГКНТ СССР (21) 4380186/24-24 (22) 16 .02.88 (46) 15.08.89. Бюл. Р 30 (71) Таганрогский радиотехнический . институт им. В.Д.Калмыкова (72) В,И.Омельченко, С.Л.Сироткин и Б.И.Строцкий (53) 681.32 (088.8) (56) Авторское свидетельство СССР

Р 1095166, кл. G 06 F 3/05 ° 1982.

Авторское свидетельство СССР

Ф 1273911, кл. С 06 F 3/05, 1985.

ÄÄSUÄÄ 1501025 А 1 (54) ИНОГОКАНАЛЬНОЕ УСТРОЙСТВО ДЛЯ

ВВОДА АНАЛОГОВЫХ ДАННЫХ (57) Изобретение относится к измерительной и вычислительной технике и может быть использовано в системах сбора данных и обработки аналоговой информации, Целью изобретения является повышение быстродействия устройства за счет совмещения во времени процессов кодирования информации и чтения данных при любом варианте распределения по диапазону значений

СЛ

СР

<Р

hD

СЛ

1501025

10 входных впало!овых сигналов. Устрой ство содержит первый счетчик l, первый цифроаналоговый преобразователь

2, каналы 3 ввода аналоговых данных, блок 4 формирования приоритетного адреса, второй цифроаналоговый преобразователь 5, блок 6 управления эталоном, первый блок 7 элементов И, первый элемент ИЛИ 8, аналоговый сумматор 9, третий цифроаналоговый преобразователь 10, первый компаратор

Изобретение относится к области измерительной и вычислительной техники и может быть использовано в системах сбора данных и обработки аналоговой информации.

Целью изобретения является повышение быстродействия устройства за счет совмещения во времени процессов кодирования информации и чтения данных при любом варианте распределения по диапазону значений входных аналоговых сигналов.

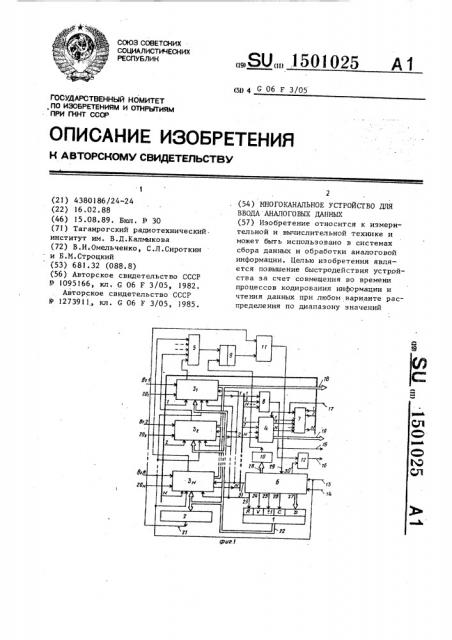

На.фиг. 1 приведена схема устройства; на фиг. 2 — схема канала ввода аналоговых данных; на фиг. 3 †. схема блока управления эталоном; на фиг. 4-6 — временные диаграммы.

Схема (фиг.1) содержит первый .счетчик 1, первый цифроаналоговый . 35 преобразователь (ЦАП) 2, каналы 3 ввода аналоговых данных, блок 4 формирования приоритетного адреса, второй ЦАП 5, блок 6 управления эталоном, первый блок 7 элементов И, пер- 40 вый элемент ИЛИ 8, аналоговый сумматор 9, третий ЦАП 10, первый компаратор 11, второй элемент ИЛИ 12, вход

13 сброса устройства, вход 14 запуска устройства„ выход 15 запроса чте- 45 ния устройства, выход 16 конца операции устройства, вход 17 чтения устройства, выход 18 данных устройства, выход 19 адреса устройства, аналоговые входы 20 устройства, выход 21 первого ЦАП 2, выход 22 счетчика 1, выход 23 установки блока 6, выход 24 полярности блока 6, выход 25 счета блока 6, выход 26 записи блока,6, первую группу выходов 27 данных блока 6, вторую группу выходов 28 данных блока 6, вход 29 данных блока 6, выход 30 копирования блока 6, выход

31 "Работа" блока 6.

11, второй элемент 1Н1И 12. Указанная цель до< тягается за счет введения второго цифроаналогового преобразователя 5, блока 6 управления эталоном, первого блока 7 элементов И, первого элемента ИЛИ 8, аналогового сумматора 9, третьего цифроаналогового преобразователя 10, первого компаратора 11 и второго элемента ИЛИ 12.

6 ил.

Блок 4 формирования приоритетного адреса (фиг.2) содержит второй компа- ратор 32, элемент 33 задержки, первый триггер 34, элемент 35 ЭКВИВАЛЕНТНОСТЬ, первый элемент И 36, третий элемент ИЛИ 37, элемент 38 буферной памяти, второй триггер 39.

Блок 6 управления эталоном (фиг.3) содержит третий триггер 40, четвертый элемент ИЛИ 41, второй, третий и четвертый элементы И 45, 42, 43, одновибратор 44, генератор 46 импульсов регистр 47 последовательных приближений, четвертый триггер 48, второй счетчик 49, пятый элемент ИЛИ 52, регистр 53 данных.

Выход счетчика 1 подключен к входу первого ЦАП 2 и к входам данных элементов 38 буферной памяти в каждом канале -3 ввода аналоговых данных, выход первого ЦАП 2 соединен с вторыми входами каждого компаратора 32 в каналах 3 ввода аналоговых данных, первые входы которых являются аналоговыми входами 20 устройства, информационные выходы элементов 38 буферной памяти всех каналов 3 ввода аналоговых данных объединены и являются выходом 18 данных устройства, а группа выходов адреса блока 4 формирования приоритетного адреса является выходом 19 адреса устройства, в каждом канале 3 ввода аналоговых данных выход компаратора 32 соединен с первым и через элемент 33 задержки с вторым входами элемента 35 ЭКВИВАЛЕНТНОСТЬ, а также поступает на соответствующий вход второго ЦАП 5, выход элемента

35 ЭКВИВАЛЕНТНОСТЬ в каждом канале 3 ввода аналоговых данных соединен с третьим входом элемента И 36, второй вход которого подключен к инверсному выходу триггера 34 и к входу разре1501025

6 щения компаратора 32, а первый вход соединен с выходом 31 "Работа" блока

6 управления эталоном, выход элемента И 36 каждого канала 3 ввода анало5 говых данных соединен с входами установки триггеров 34, 39 с записи соответствующего элемента 38 буферной памяти, вход чтения каждого из которых соединен с соответствующим номеру канала выходом блока 7 элементов И и первым входом элемента ИЛИ 37 одноименного канала 3, выход которого подключен к входу сброса триггера 39 а второй вход соединен с входом 13 15 сброса устройства, вход сброса триггера 34 каждого канала 3 ввода аналоговых данных соединен с входом сброса счетчика 1 и. выходом 23 установки блока 6 управления эталоном, 20 прямой выход второго триггера 39 каждого канала 3 ввода аналоговых данных поступает на соответствующий вход элемента ИЛИ 8 устройства и блока 4 формирования приоритетного адреса, 25 выход второго ЦАП образователя 5 соединен с первым входом аналогового сумматора 9, второй вход которого подключен к выходу третьего ЦАП 10, а выход соединен с вторым входом ком- 30 паратора 11, первый вход которого подключен к выходу 21 первого ЦАП 2, а выход соединен с входом 29 данных блока 6 управления эталоном, стробирующий вход блока 7 элементов И соединен с блокирующим входом блока 4 .формирования приоритетного адреса и является входом 17 чтения устройства, выход первого элемента ИЛИ. 8 подключен к первому входу элемента ИЛИ 4р

12 и является выходом 15. запроса чтения устройства, второй вход второго элемента ИЛИ 12 соединен с выходом 30 кодирования блока 6 управления эталоном, а выход является выходом 45

l6 конца операции устройства, информационный вход счетчика 1 соединен с первой группой выходов 27 данных блока 6 управления эталоном, вторая группа выходов 28 данных которого поступает на вход третьего ЦАП 1О, вход запуска блока 6 является входом 14 запуска устройства, а вход сброса блока 6 является входом 13 сброса устройства, ввод 26 записи блока 6 управления эталоном соединен с синхровходом параллельной записи счетчика 1, выход 25 счета блока 6 управ ления эталоном подключен к счетному входу счетчика 1, а выход 24 полярности соединен с входом управления реверсом счетчика 1, в блоке 6 управления эталоном вход установки триггера 40 соединен с входом 14 запуска устройства и с первым входом элемента ИЛИ 52, выход первого триггера подключен к первому входу элемента И

45 и является выходом 30 кодирования блока 6, второй вход элемента И 45 соединен с первылп входами элементов

И 42, 43, с синхровходом регистра 47 последовательных приближений и с выходом одновибратора 44, вход которого соединен с сипхровходом регистра

53, с выходом элемента ИЛИ 52 и является выходом 26 записи блока 6, выход элемента И 45 подключен к входу генератора 46 и является выходом 31

"Работа" блока 6, выход генератора 46 является выходом 25 счета блока 6, выход генератора 46 соединен со счетным входом счетчика 49 и является выходом счета блока 6, выход счетчика

49 подключен к первому входу блока элементов И 51 и к входу дещифратора

50, все выходы которого, кроме последнего, соединены с соответствующими входами элемента ИЛИ 52, а последний — поступает на первый вход элемента ИЛИ 41, второй вход которого соединен с входом сброса счетчика

49 и является входом 13 сброса устройства, а выход подключен к входу сброса триггера 40, к входу сброса регистра 53 и регистра 47 последовательных приближений и является выходом 23 установки блока 6, вход 29 данных блока 6 управления эталоном соединен с входом данных регистра 47 последовательных приближений, с вторым инверсным входом элемента И 42 и вторым входом элемента И 43, выход которого подключен к входу сброса триггера 48, установочный вход которого соединен с выходом элемента И

42, выход регистра 47 последовательных приближений соединен с вторым входом блока 51 элементов И и является первой группой выходов 27 данных блока 6 управления эталоном, выход блока 51 элементов И соединен с информационным входом регистра 53, выход которого является второй группой выходов 28 данных блока 6 управления эталоном, выход 24 полярности которого является прямым выходом триггера 48.

150)015

Многоканальное устройство для ввода аналоговых данных работает следующим образом. установочным сигналом по входу 13 сброса осуществляется в каждом канале 3 ввода аналоговых данных сброс второго триггера 39 через элемент

ИЛИ 37, а в блоке 6 управления эталоном сброс счетчика 49 и через эле- 10 мент ИЛИ 41 начальная установка триггера 41, регистра 47 последовательных приближений, регистра 53 и через выход 23 установки начальная установка счетчика 1 и в каналах 3 ввода 15 аналоговых данных осуществляется начальная установка триггера 34. При этом сигналом с инверсного выхода триггера 34 в каналах 3 разрешается. работа компаратора 32 и подается раз- 20 решающий сигнал на второй вход элемента И 36, нулевой сигнал с прямого выхода триггера 39, поступающий на входы элемента ИЛИ 8 устройства и на входы блока 4 формирования приоритет- 25 ного адреса, свидетельствует об отсутствии информации в элементе 38 буферной памяти соответствующего канала 3 ввода аналоговых данных; выход счетчика 1 имеет нулевое значение; в блоке 6 управления эталоном с единичного выхода триггера 40 через элемент И 45 запрещается работа генератора 46, регистр 53 обнуляется, исходным состоянием регистра 47 по- 35 следовательных приближений является состояние со взведенным старшим раз" рядом, т.е. на его выходе присутствует код: 100...00, счетчик 49 обнуляется. 40

Работа устройства начинается непосредственно с момента подачи через вход 14 запуска сигнала запуска на вход блока 6 управления эталоном.

Временная диаграмма работы блока 6 45 приведена на фиг. 4.

Сигнал запуска по входу 14 устанавливает в единичное состояние триггер 40 блока 6 управления эталоном и через элемент ИЛИ 52 проходит на вход одновибратора 44, синхровход регистра 53 и через выход 26 записи блока 6 поступает на синхровход параллельной записи счетчика 1. При этом одновибратор 44 формирует импульс отрипательной полярности длительности t с целью заблокировать о на время 5 прохождение разрешающего о сигнала < выхода триггера 40 на управляющий вход генератора 46, единичный сигнал с выхода триггера 40 через выход 30 кодирования блока 6, элемент ИЛИ 12 поступает на выход 16 устройства. Наличие единичного сигнала на выходе 16 свидетельствует о том, что многоканаль— ное устройство для ввода аналоговых данных находится в состоянии выполнения приоритетных функций. В регистр 53 на данном такте работы устройства заносится нулевой код, так как наличие на выходе счетчика 49 нулевой кодовой комбинации, а на выходе регистра 47 последовательных приближений кодовой комбинации с единицей в старшем разряде даст в итоге на выходе блока 51 элементов И нулевую кодовую комбинацию. В счетчик 1 будет записана кодовая комбинация с единицей в старшем разряде, т.е. код, соответствующий половине диапазона аналоговых сигналов.

На фиг. 4 показано, что аналоговый сигнал на выходе первого ЦАП 2 за время t установится равным половине диапазона аналоговых сигналов.

Так как этот сигнал с выхода 21 поступает на вторые входы компараторов

32, на первые входы 20 которых поданы входные аналоговые величины, то часть компараторов 32 сработает, а часть нет. Компаратор 32 срабатывает, т.е. выдает на своем выходе единичный сигнал, если входной сигнал больше

Ф или равен опорному, т.е. сигналу с выхода первого ЦАП 2. С изменением состояния выхода компаратора 32 с помощью элемента 33 задержки и элемента 35 ЭКВИВАЛЕНТНОСТЬ на третьем входе элемента И 36 формируется сигнал, но до поступления разрешающего сигна- . ла "Работа" по входу 31 прохождение его на выход элемента И 36 заблокировано. Поэтому возможное срабатывание компаратора 32 в процессе подготовительных к процедуре измерений операций не приводит к каким-либо изменениям в схеме. Выходы компараторов 32 всвх каналов 3 ввода аналоговых данных поступают на входы второго ЦАП

5. Аналоговый выход ЦАП 5 отмасштабирован таким образом, чтобы при наличии единиц на всех его входах аналоговый сигнал на выходе был бы равен максимальному значению аналогового сигнала на входах устройства, т.е. ,диапазону. Выход ЦАП 5 подключен к

1025

15

25

9 150 первому входу аналогового сумматора

9, на второй вход которого подается сигнал с выхода третьего ЦАП 10, на вход которого по входу 28 поступает управляющий сигнал с регистра 53 блока 6 управления эталоном. Но на перном такте работы устройства на выходе регистра 53 присутствует нулевой

° код, что соответствует нулевому сигналу на выходе третьего ЦАП !О, который также приведен к масштабу входных сигналов. Следовательно, на первом такте работы устройства сигнал на выходе аналогового сумматора 9 соответствует сигналу на его первом входе, Этот сигнал, вес которого пропорционален числу сработавших компа- раторон 32 н блоках 3 при установке эталона, равным половине диапазона, поступает на первый вход компаратора

32, на второй вход которого подается эталонный сигнал по входу 21 с выхода первого ЦАП 2 °

Компаратор 32 срабатывает, если сигнал с выхода аналогового суммато- ра 9 больше или равен эталонному сиг-, налу на его первом входе. Срабатывание компаратора 32 свидетельствует, что в нижней половине диапазона анало говых сигналов находятся сигналы на половине и более аналоговых входах устройства. В противном случае на выходе компаратора 32 сохраняется . нулевой сигнал. Сигнал с выхода компаратора 32 поступает на вход 29 дан.ных блока 6 управления эталоном, где он поступает на информационный вход регистра 47 последовательных приближений и на вторые входы элементов И

42, 43.

Все описанные процессы должны завершиться за время длительности импульса одновибратора 44. С завершением импульса на выходе одновибратора 44 по переднему фронту через элемент И 45 запустится генератор 46, с выхода элемента И 45 по выходу 31 во всех каналах 3 ввода аналоговых данных сигналом "Работа разблокируются элементы И 36, в регистр 47 последо в ател ь ных приближений н бло ке 6 управления эталоном запишется код

I l0... 0O или 010...0 в зависимости от значения сигнала на его информационном входе, триггер 48 блока 6 управления эталоном будет установлен в нулевое или единично» состояние, также в зависимости от значения сигнала на выходе компаратора 32, сигHQJlbl с выхода генератора 46 начинают поступать на счетный вход счетчика 49 и по выходу 25 на счетный вход счетчика 1 ° При этом направление счета— суммирование или вычитание счетчика 1 — определяется по выходу 24 сигналом полярности с выхода второго триггера 48 блока 6 управления эталоном. А именно, единичное значение на выходе компаратора 32 должно приводить к вычитающему режиму работы счетчика 1, так как большая часть входным сигналов находится в нижней половине диапазона аналоговых сигналов и разворачивание эталонной меры целесообразно начинать именно с этой области диапазона. В этом случае первые результаты будут получены в начальной стадии разворачивания эталонной меры и, следовательно, раньше можно будет начать процедуру чтения.

Поступление импульсов на счетный вход счетчика I, выход которого поступает на вход первого ЦАП 2, принодит к разворачиванию эталонной меры, которая поступает на вторые входы компараторов 32 в каналах 3 ввода аналоговых данных. Параллельно эаполняется счетчик 49.

На фиг. 4 разворачивание эталонной меры на выходе первого ЦАП 2 показано вниз от середины диапазона. По мере уменьшения эталонно го сигнала

35 на вторых входах компараторов 32 каналов 3 ввода аналоговых данных ранее сработавшие компараторы будут сбрасываться. При этом на отрица40 тельном фронте на выходе компаратора

32 совокупность элементов 33 задержки и элемента 35 ЭКВИВАЛЕНТНОСТЬ будут формировать выходной импульс, как и на положительном фронте. Но теперь этот импульс будет проходить на выход элемента И 36, так как на первом и втором его входах установлены разрешающие потенциалы. Импульсом с выхода элемента И 36 осуществляется за пись данных по выходу 22 с выхода счетчика 1 в элемент 38 буферной памяти того канала 3 ввода аналоговых данных, компаратор 32 которого вновь сбросился.

Таким образом, так как состояние счетчика 1 на момент сброса соответ— ствующего компаратора эквивалентно в аналоговой форме входному аналоговому сигналу на соответствующем входе

1501025

20 устройства, то, следовательно, в элемент 38 памяти з»носится цифровой эквивалент входного аналогового сигнала. Кроме того, тем же сигналом с выхода элемента И 36 осуществляется установка триггеров 34, 39 соответствующего канала 3 вводя »налоговых данных. С инверсного выхода первого триггера 34 при этом запрещается вы- 10 ход элемента И 36, т е. канал становится невосприимчив к дальнейшим изменениям входных сигналов, так как компаратор 32 также выключается вплоть до появления нового сигнала 15 установки по выходу 23, который может появиться только после завершения всего цикла кодирования. Также . взвоцится триггер 39, сигнал с выхода которого поступает на один из вхо- 20 дов элемента ИЛИ 8 и с его выхода на выход 15 устройства, а также через элемент ИЛИ 12 на выход 16 устройства. Сигнал с выхода триггера 39 по ступает также на один из входов бло— ка 4 формирования приоритетного адреса.

С появлением первого результата в одном из каналов 3 ввода аналоговых данных с учетом наличия сигналов за- 30 проса чтения и конца операции соответственно на выходах 15 и 16 независимо от процедуры кодирования можно осуществлять процедуру чтения.

При чтении данных из элемента 38 буферной памяти любого канала 3 ввода аналоговых данных на его вход чтения от блока 7 элементов И по радиальной линии поступает импульс чтения, который открывает выходы соот †. 40 ветствующего элемента 38 буферной памяти на выход 18 данных и через элемент ИЛИ 37 сбрасывает триггер 39 соответствующего канала..

Следует отметить,. что если бы разворачивание эталонной меры происходило бы не сверху вниз, как это описано, а снизу вверх, т,е. в каналах компараторы на сбрасывались, а устанавливались, то последовательность работы элементов канала была бы такой же, так как на выходе элемента

35 ЭКВИВАЛЕНТНОСТЬ сигнал формируется на обоих фронтах с выхода компаратора 32.

На фиг. 5 приведена временная диаграмма работы канала 3 ввода »н»логовых д»нных.

Таким образом на первом такте работы устройств» происходит разворачив»ние эталонно го сигнала в одной из половины диапазона»налоговых сигналон в нижней либо в верхней в зависимости от того, в какой половине находится я большая ч асть входных величин .

В первом случае счетчик 1 изменит свое состояние от кода 100 ... О до кода 00 ... О, а во втором случае счетчик 1 изменит свое состояние от кода 1000 ° .. 00 до 00 ... О, т.е. до переполнения. В обоих ситуациях счетчик 49 в блоке 6 управления эталоном . аполнится до состояния 100

0 (при равной разрядности счетчиков). Эта кодовая комбинация выделяется дешифратором 50, с выхода которого через элемент ИЛИ 52 формируется второй тактовый сигнал работы устройства. Этим сигналом через одновибратор 44 и элемент И 45 останавливается вновь на время генератор 46.

По выходу 26 в счетчик 1 осуществляется запись нового начального слова.

Это слово будет 010 ... О, если перед этим было разворачивание вверх, или .слово 1100 ... О, если на первом такте было разворачивание вверх. Первый означает начальную установку 1/4 аналогового диапазона, а второй соответственно 3/4 аналогового диапазона. Эти точки будут исходным пунктом второго такта разворачивания эталона.

Каково же положение с компараторами 32 и ЦАП 5? Если разворачивание эталона производилось на первом такте вниз, то это выключит из работы все компараторы 32, сигналы с входов 20 которых лежат в нижней половине диапазона. Если же разворачивание эталонной меры на первом такте работы устройства производилось вверх, то это выключит из дальнейшей работы все компараторы 32 с сигналами, лежащими в верхней половине диапазона.

В первом случае для оценки оставшихся входов в верхней час ги диапазона с помощью ЦАП 5 необходимо к значению на еro выходе добавить значение в половине диапазона. Т.е.: необходим пьедестал в 0,5 диапазона.

Во втором случае, когда на втором такте разворачивание будет в нижней части диапазона, пьедестал не требуется. Для создания пьедестала используется ЦАП 10, аналоговый сумматор 9, 1 4

01025

13

15 а в блоке 6 управления эталоном блок

51 элементов И и регистр 53. Как ни— дим, запись н регистр 53 производится по переднему фронту сигнала с выхода элемента IUIH 52. В начале второго такта на выходе счетчика 49 имеется код 100...0, а на выходе регистра 47 последовательных приближений код 1100...0 или код 0100 ... О. Т.е. в регистр 53 будет записан код

100 ... О или код 00 ... О в зависимости от состояния старшего разряда на выходе регистра 47 последовательных приближений. Но н старший разряд регистра 47 последовательных приближений записывается единица в том случае, если на выходе компаратора II была единица и затем следовало разворачивание эталона вниз. Т.е. с выхода регистра 53 через ЦАП 10 пьедестал будет формироваться именно в . тех случаях, если на предыдущем такте было разворачивание вниз. Аналогичным образом формируется пьедестал ,и на последующих тактах работы устройства. Т.е. пьедестал может быть и в 1/2 диапазона, и в 3/4 диапазона, и в 2/4 диапазона и т.д. Механизм формирования пьедестала показан на временных диаграммах фиг. 6. На фиг.6 показано формирование пьедестала на третьем такте работы устройства. При этом пьедестал формируется после разворачивания вверх в верхней половине диапазона и разворачивания вниз в .нижней четверти диапазона, перед разворачиванием эталона вверх во второй четверти диапазона.

Новый начальный сигнал, установленный на выходе 21 с выхода первого

ЦАП 2, воздействУет на вторые входы компараторов 32 каналов. Вновь взведется часть ранее не срабатывавших компараторов 32, если новое исходное состояние эталона 3/4 диапазона, или сбросится ряд ранее взведенных, но

Hp опрошенных компараторов. если новое исходное значение эталона равно

1/4 диапазона. При этом ЦАП 5 управляют взведенные компараторы 32 за исключением уже опрошенных на первом такте работы.

При этом н верхней части диапазона на входы компаратора 11 будет подано эталонное напряжение в 3/4 диапазона и напряжение с. выхода аналогового сумматора 9, ранное сумме пьедестала в !/2 диапазона, поступающего с выхода ЦАП 10, и напряжению с выхода ЦАП 5. Поскольку предыдущее разворачивание эталонной меры было вниз, то очевидно, что н верхней половине диапазона лежит менее I/2 входных сигналов. Следовательно, так как компараторы всех каналов, сигналы на входах которых лежат в нижней половине диапазона, уже заблокированы, то в зависимости от того, сколько входных сигналов лежит в третьей четверти (при счете снизу) диапазона, на выходе ЦАП 5 может появиться

15 сигнал от О до 1/2 диапазона. T e. суммарный сигнал на выходе аналоroвого сумматора 9 в принципе может находиться в диапазоне от 1/2 до 1,0 диапазона. Следовательно, в зависи20 мости от распределения нходных сигналов в верхней части диапазона компаратор 11 может сработать или не сработать. Аналогично первому такту работы устройства компаратор II cpa25 батывает, если сигнал с выхода аналогового сумматора 9 превышает уровень

s 3/4 диапазона. Это событие i:oçíà.— чает, что число входных сигналов, находящихся в диапазоне от 1/2 до

3р 3/4 диапазона, превышает 1/4, общего числа входных сигналов. Следовательно, дальнейшее разворачивание эталонной меры целесообразно вести именно в этом направлении. 11ожет случиться

35 TGK RTQ IIocJIe разворачивания 9TBJIQ на на первом такте рабсты устройства в верхней части останется вообще менее 1/4 входных сигналов, тогда дальнейшее разворачивание эталона

40 возможно примет не оптимальный характер. Однако это не скажется на конечный результат работы, так как при двух тактах работы устройства выход по чтению за пределы цикла коди45 ронания не может превысить величины (1/4) аналоговых входов, а при трех тактах величины — (1/8) аналоговых входов, т.е. величин получаемых при оптимальном алгоритме разнорачива50 ния, но при худшем распределении нходных сигналов.

В нижней части диапазона на втором такте разворачивания эталона на входы компаратора 11 подается по выходу 21 начальный сигнал в I/4 диапазона и сигнал с выхода ЦАП 5, которыи также может меняться н интервале от 0 до 1/2 диапазона. Напряжение пьедестала. и этом слу

15 150

Б результате сравнения компаратор 11 вырабатывает сигнал, определяющий направление дальнейшего разворачивания эталона. На фиг. 4 показано, что на втором такте работы устройства компаратор !1 не срабатывает. В этом случае по переднему фронту импульса с выхода одновибратора 44 в блоке 6 управления эталоном триггер 48 перейдет в единичное состояние и по выходу 24 полярности переведет счетчик 1 в режим суммирования. Одновременно в регистр 47 последовательных приближений будет записана кодовая, комбинация, соответствующая начальной точке разворачивания эталона на предстоящем третьем этапе работы устройства. В соответствии с вариантом разворачивания эталона на фиг. 4 кодовая комбинация на выходе регистра 47 последовательных приближений на втором такте работы устройства будет следующая — IOIO ... О. Следовательно, начальная точка разворачивания эталона на третьем такте работы устройства будет равна 0,625 диапазона.

С окончанием импульса с выхода одновибратора 44 вновь через первый элемент И 45 запускается генератор 46, а по выходу 31 в каналы ввода 3 аналоговых данных поступает разрешающий сигнал "Работа", который позволяет воспринимать управляющие сигналы с выходов компараторов 32 элементам 38 буферной памяти. Следующая кодовая комбинация, выделяемая счетчиком 49, будет код 1100 ... О, т.е ° в счетчик

I добавится (или убавится ) число импульсов, соответствующее прохождению эталонной мерой при разворачивании четверти диапазона.

Работа устройства на третьем и последующих тактах протекает аналогично . Число тактов в пределе равно разрядности блоков 2 и )0. Особо следует отметить прерывания процесса деления диапазона по правилу дихотомии по признаку наибольшего скопления входных сигналов. Реализуется прерывание процесса дихотомии методом ограничения числа разрядов регистра 47 последовательных приближений и регистра 53 по гравнению со счетчиком l.

Т.е. параллельную запись начальных кодов счетчика 1 производят только в старшие р» зря гил . Дей стви тельно, е< пи, например, ре и" тр 47 последовательных приб. в ж ib,й будет только трех1025!

6 разрядным при цвенаццатиразрядном счетчике I то параллельную запись начальных кодовых комбинаций с»сдует производить только в 3 старших разряда, а в остальные разряды записываются нули. Тогда вследствие то —, го, что на четвертом такте работы устройства вновь вводимая единица вы10 хоцит за пределы разрядной сетки, устройство вновь вернется в предьдущую точку разворачивания, а так как необработанные каналы 3 ввода аналоговых данных остались только в одной

15 части диапазона, пьедестал будет также установлен по результатам предыдущего разворачивания, то последний такт разворачивания эталона неизбежно будет направлен в необработанную

20 зону диапазона. Соответственно числу планируемых тактов работы устройства должен иметь и число выходов дешифратор 50.

Переполнение счетчика 49 соответствует полному прохождению эталоном диапазона аналоговых сигналов. Это состояние счетчика 49 выявляется на последнем выходе дешифратора 50.

Этим сигналом сбрасывает первый триг30 rep 40, регистр 47 последовательных приближений, регистр 53 и по выходу

23 счетчик 1 и триггер 34 в каналах

3 ввода аналоговых данных. Измерительная часть устройства приходит в исходное состояние. Устройство вновь может быть запущено сигналом запуска по входу 14.

Однако хотя процедура измерений и завершена, но не все данные могут

4р быть еще прочитаны из элементов 38 буферной памяти каналов. Поэтому, хотя и сигнал кодирования с выхода

30 снимается на второй вход элемен" та ИЛИ 12, на первом ее входе может

45 еще присутствовать сигнал с выхода элемента ИЛИ 8 запроса чтения. Сигнал с выхода элемента ИЛИ 12 ".Конец работы" сбрасывается только при условии отсутствия запросов на чтение и за5р вершение процедуры. кодирования. . Принципиально содержимое элементов 38 буферной памяти может и не прочитываться, В этом случае устройство работает аналогичным образом, а информация в элементах 38 буферной памяти обновляется.

Чтение данных из многоканального устройства для ввода аналоговых дан-, ных может осуществляться при нали17

1 (.) 1(> чии сигнала За««ро чтения на выходе 1 5. Следует отметить, что этот сигнал в »роцессе кодирования в зависимости от скорости чтения и ин5 тенсивности поступления новых данных может и сниматься. Но всегда, когда присутствует потенциал на выходе 16

"Конец операции" сохраняется возмож ность появления сигнала запроса чтения.

В процессе срабатывания вторых триггеров 39 в каналах 3 ввода анало— говых данных при записи информации в элементы 38 буферной памяти соответственно через элемент ИЛИ 8 формируется сигнал запроса чтения, а на выходе блока 4 формирования приоритетного адреса формируется двоичный код старшего из выставивших запрос кана- 2(1 лов на выходе 19 адреса канала и уни— тарный позиционный код старшего из выставивших запрос канала на группе выходов блока 4 подключенных к входам блока 7 элементов И. По импульсу чте — 25 ния на одноименном входе 17 (старшем из выставивших запрос каналов 3) на выходе блока 7 элементов И появляется сигнал, поступающий по индивидуальной линии на вход чтения соответствующего 3р канала. При этом триггер 39 в соответствующем канале сбрасывается, а выходы элемента 38 буферной памяти открываются на выход 19 данных. Опрошенный канал вследствие сброса триггера 39 снимает запрос, а на выходах блока 4 формирования приоритетного адреса устанавливается адрес следующего по старшинству из запросивших чтение каналов. Таким образом одно- 4р временно осуществляется чтение данных и номера канала, по которому получены эти данные. Для исключения сбоя во время чтения сигналом чтения временно блокируется работа блока 4 формирова- 4 ния приоритетного адреса.

Таким образом устройство позволяет осуществлять процедуру чтения независимо от процедуры кодирования и, кроме того, за счет получения результатов в начальной части процедуры кодирования получается почти полное совмещение во времени кодирова«пгя и чтения данных, что позволяет значительно сократить врсмя ввода даниых B цвг 1.

Ф о р м у л а и з о б р е т е н и я

Иногока»альное устройст:o для ввода аналоговых данных, содержащее

tfe:ðtt«té < чет п«к, »ервый цифроаналоговый преобразователь, блок формирования»риоритет»ого адреса и каналы ввода а ««ало го вых данных, каждьгй из которых содержит второй компаратор, первый и второй триггеры, элемент буферной»амяти, причем выход первого счетчика подключен к входу первого цифроаналогового преобразователя и к входам данных элементов буферной

««амяти, выход первого цифроаналогового преобразователя соединен с вторыми входами вторых компараторов, первые входы которь«х являются аналоговыми входами устройства, выходы элементов буферной памяти являются выходом дашгь«х устройства, а группа выходов блока формирования приоритетного адреса является выходом адреса устройства, о т л и ч а н щ е е с я тем, что, с целью повышения быстродействия устройства за счет совмещения во времени процессов кодирования информации и чтения даннь«х при любом варианте распределения по диапазону входных аналоговых сигнг«:«ов, в него введены второй и третий цифроаналоговые преобразователи, аналоговый сумматор, первый компаратор, первьпг и второй элементы ИЛ11, п ервый блок элементов И и блок управления эталоном, содержащий третий и четвертый тригг е, ры, одновибратор, второй, третий и четвертый элементы И, генератор импульсов, второй счетчик, дешифратор, четвертый и пятый элементы

ИЛИ, регистр последовательных приближений, регистр данн::-«х и второй блок элементов И, а в каждый канал ввода аналоговых данных введены элемент задержки, элемент ЭКВИВАЛЕНТНОСТЬ, первый элел«ент И н третий элемент ИЛИ, причем выход второго компаратора соединен с первым входом элемента ЭКВИ—

ВАЛЕНТН(«СТЬ и с входом элемента задержки, выходы вторых компараторов соединены с входами второго цифроанаJ1oгового преобразователя выход эле« мента задержк» соединен с вторым входом эле мента Э КВИБЛ. 1 . НТ НОСТЬ, выход которого соединен с третьим входом первого элемента 11, второй вход которого подключен ь «п«версноиу выходу гтервого триггера» ь входу разрешения второ го ком»ар;«тора, а первый вход пер ногo:«J«t- ««å«tò;«И соединен с выходом второго э. «t мг «ti à И и с входом генератора им»у«чь»< в, выход первого

19 l 50 элемента И соединен с входами установки первого и второго триггеров и с входом записи элемента буферной памяти, вход чтения которого соединен с первым входом третьего элемента ИЛИ, входы чтения элементов буферной памяти соединены с соответствующими выходами первого блока элементов И, выход третьего элемента ИЛИ ) подключен к входу сброса второго триггера, второй вход третьего элемента

ИЛИ. соединен с входом сброса второго счетчика, с вторым входом четвертого элемента ИЛИ и является входом 1 сброса устройства, вход сброса первого триггера соединен с входами сброса третьего триггера, регистра последовательных приближений, регистра данных, первого счетчика и с выходом четвертого элемента ИЛИ, прямые выходы вторых триггеров соединены с соответствующими входами первого элемента ИЛИ и блока формирования приоритетного адреса, вход установки третьего триггера соединен с первым входом пятого элемента ИЛИ и" является входом запуска устройства, вход данных регистра последовательных приближений соединен с первыми входами третьего и четвертого элементов И и с выходом первоro компаратора, прямой выход третьего триггера соединен с первым входом второго элемента И и с вторым входом второго элемента ИЛИ, выход пятого элемента ИЛИ соединен с входом одновибратора, с синхровходом регистра данных и с синхровходом параллельной записи первого счетчика, выход генератора импульсов соединен со счетными входами первого и второго счетчиков, выход регистра последовательных приближений соединен с вторым входом второго блока элементов И и с информационным входом первого счетчика, выход регистра данных!

025 20 соединен с входом третье ГО цифро як алогового преобразователя, прямой выход четвертого триггера соединен с входом управления р