Вычислительное устройство

Иллюстрации

Показать всеРеферат

Изобретение относится к вычислительной технике и может быть использовано в ЭВМ. ЦЕЛЬ ИЗОБРЕТЕНИЯ - ПОВЫШЕНИЕ БЫСТРОДЕЙСТВИЯ УСТРОЙСТВА. УСТРОЙСТВО СОДЕРЖИТ АРИФМЕТИКО-ЛОГИЧЕСКИЙ БЛОК 1, СДВИГАТЕЛЬ 2, КОММУТАТОР 4, ТРИ БУФЕРНЫХ РЕГИСТРА 3,8 И 9, БЛОК 5 АДРЕСУЕМЫХ РЕГИСТРОВ, РЕГИСТР 6 РЕЗУЛЬТАТА И РЕГИСТР 7 ИНФОРМАЦИИ. НОВЫМ ЯВЛЯЕТСЯ ВВЕДЕНИЕ ТРЕТЬЕГО ИНФОРМАЦИОННОГО ВХОДА И ВТОРОГО УПРАВЛЯЮЩЕГО ВХОДА КОММУТАТОРА 4, ПОЗВОЛЯЮЩИЕ ВЫПОЛНИТЬ КОМАНДУ ПРЕОБРАЗОВАНИЯ В ДОПОЛНИТЕЛЬНЫЙ КОД ЗА ОДИН МАШИННЫЙ ТАКТ. 2 ИЛ.

СОЮЗ СО8ЕТСКИХ

СОЦИАЛИСТИЧЕСКИХ

РЕСПУБЛИК

„.$0„„ИЫ40 (5й 4 С 06 F 7/38

ОПИСАНИЕ ИЗОБРЕТЕНИЯ

К А BTOPCHOMY СВИДЕТЕЛЬСТВУ

ГОСУДАРСТ8ЕННЫЙ КОМИТЕТ

ПО ИЗОБРЕТЕНИЯМ И ОТКРЫТИЯМ

ПРИ ГКНТ СССР

1 (61) 1405047 (21) 4371140/24-24 (22) 04.12.87 (46) 15.08.89. Бюл. № 30 (72) А.Е.Саркисян, P.Ê.ÁýíóíH и В.Н.Газиян (53) 681.325(088.8) (56) Авторское свидетельство СССР по заявке ¹ 4090698/24-24, кл. С 06 Г 7/38, 1986. (54) ВЫЧИСЛИТЕЛЬНОЕ УСТРОЙСТВО (57) Изобретение относится к вычислительной технике н может быть ис2 пользовано в ЭВМ. Цель изобрете ния — повышение быстродействия устройства. Устройство содержит арифметико-логический блок 1, сдвигатель

2, коммутатор 4, три буферных регистра 3,8 и 9, блок 5 адресуемых регистров,регистр 6 результата и регистр

7 информации. Новым является введение третьего информационного входа и второго управляющего входа коммутатора 4, позволяющее выполнить команду преобразования в дополнительный код за один машинный такт. 2 ил. 1

0 4

10 которого объединен с выходом 15 блока 5 адресуемых регистров, с вторым выходом регистра 6 результата, с первым выходом регистра 7 информации и соединен с информационным входом второго буАерного регистра 8, выход третьего буферного регистра соединен с первым информационным входом арифметико-логического блока 1, выход первого буферного регистра 3 соединен с первым информационным входом коммутатора 4,выход которого соединен с вторым информационным входом арифметико-логического блока 1 и с инАормационным входом сдвигателя 2, выход второго буАерного регистра 8 соединен с информационным входом первого буАерного регистра 3 с объединенными вторыми инАормационными входами регистров 6 и 7 результата и информации, с вторым информационным входом коммутатора 4, первый управляющий вход которого соединен с шестым тактовым входом 23 устройства, седьмой и восьмой тактовые входы 24

3 150104

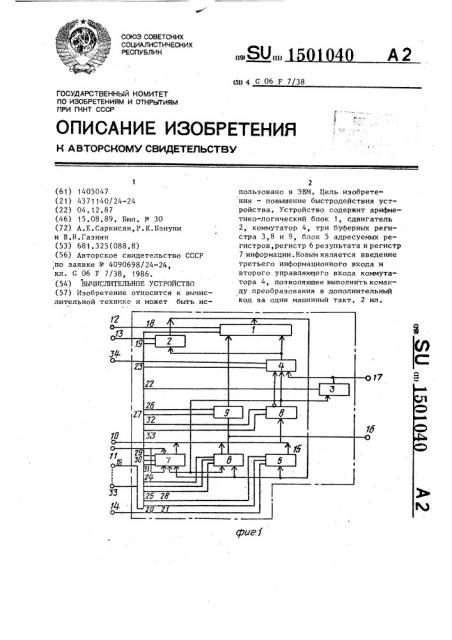

Изобретение относится к области вычислительной техники и может быть использовано в ЭВМ, Целью изобретения является повы5 шенйе быстродействия, На фиг. 1 представлена схема вычислительного устройства; на Аиг.2временная диаграмма поступления тактовых и управляющих сигналов. 1О

Вычислительное устройство (Аиг, 1) содержит ариАметико-логический блок

1, сдвигатель 2, первый буферный ре. гистр 3, коммутатор 4, блок 5 адресуемых регистров, регистр б резуль- 15 тата, регистр 7 информации, второй и третий буферные регистры 8,9 первый и второй инАормационные входы

10, 11 устройства, вход 12 задания ,вида операции устройства, вход 13 20 задания величины сдвига устройства, адресный вход 14 устройства, выход

15 блока 5, выход 16 результата устройства, выход 17 адреса устройства, тактовые с первого по шестнадцатый входы 18-33 устройства, вход

34 признака операции,преобразования в дополнительный код устройства, причем выход арифметико-логического блока 1 объединен с выходом сдвигателя 2 и соединен с информационным входом блока 5 адресуемых регистров, с первым иформационным входом регистра 7 инАормации и с первым информационным входом регистра 6 результата, первый выход которого соединен с информационным входом третьего буферного регистра 9 и является выходом 16 результата устройства„ входы 12 и 13 задания вида операции 40 и величины сдвига которого соединены соответственно с входом вида операции арифметико-логического блока 1 и входом величины сдвига сдвигателя 2, входы разрешения выдачи арифметико — 45 логического блока 1 и сдвигателя 2 соединены соответственно с первым и вторым тактовыми входами 18 и 19 устройства,адресный вход 14 которого соединен с входом адреса блока 5 адресуемых регистров, входы разрешения записи и разрешения выдачи которого соединены соответственно с третьим и четве тым тактовыми вхо ами 20 и 21 устройпервого буферного регистра 3, выход которого является выходом 17 адреса устройства, первый информационный вход и 25 которого соединены соответственно с первым и вторым входами разрешения выдачи регистра 6 результата, второй выход и третий информационный вход регистра 7 и информации объединены и соединены с вторым инАормационным входом 11 устройства, входы разрешения записи и установки в нуль третьего буферного регистра 9 соединены соответственно с девятым и десятым тактовыми входами 26 и 27 устройства, вход направления приема регистра б результата, первый и второй входы разрешения выдачи регистра 7 инАормации, вход направления приема регистра 7 информации, входы разреше- ния записи и установки в нуль второго буферного регистра 8 соединены соотвественно с тактовыми входами 28-33 с одиннадцатого по шестнадцатый устройства, вход 34 признака операции преобразования в дополнительный код которого соединен со вторым управляющим входом коммутатора 4, третий информационный вход которого соеди- . нен с инверсным выходом второго буферного регистра 8. лов приведена в соответствии с синхросигналами Cf и С2, Например, управляющие сигналы К4(68), КОП (34) P д ства пятый тактовый вход 22 которого

1 55

Временная диаграмма (фиг.2) поссоединен с входом разрешения записи тупления основных управляющих сигна501040

С2 кои. н. half.Í . Ф.ю

НОЛЮЯ м р(Ф) ФиР 2

5 1 и т.д. устанавливаются или сбрасываются от переднего фронта С1 для каждой операции. Задним фронтом сигналов ПР.65, ПР.66 и т.д. осуществляется прием информации в соответствующие блоки. На фиг. 2 приняты следующие обозначения: ПР.65 — сигнал приема в .блок 5 адресуемых регистров; ПР.66 — сигнал приема в регистр 6 результата; ПР.67 — сигнал приема в регистр 7 информации;

ПР.68 — сигнал приема в буферный регистр 8; КОН.К вЂ” сигнал конца команды; ЧТ.К вЂ” сигнал чтения команды;

КОП(34) — признак операции преобразования в дополнительный код;

К4(68). — коммутатор 4 настраивается на инверсный выход буферного регистра 8; КШР (61) — коммутатор шины результата настраивается на арифметико-логический блок 1.

Устройство (фиг. 1) работает следующим образом.

При выполнении операции преобразования в дополнительный код находящегося в одном из регистров блока

5., его содержимое поступает в буферный регистр 8 и его инверсное значение (A) через коммутатор 4 передается на второй вход блока 1, так как с помощью признака операции коммутатор 4 настраивается на третий информационный вход. Ввиду того, что с помощью входа 12 вида операции блок 1 был настроен на операцию положительного приращения (+1), на выходе блока 1 появляется результат операции (А+1), который записывается в регистр 6 и в блоке 5 по адресу приемника. Аналогично выполняется операция при нахождении операнда в памяти с учетом того, что операнд заносится на буферный регистр 8 с входа 10 устройства. Остальные операции выполняются в устройстве аналогично прототипу.

20 Формула изобретения

Вычислительное устройство по авт, св. N- 1405047, о т л и ч а ю щ е е— с я тем, что, с целью повьппения бы25 стродействия, инверсный выход второго буферного регистра соединен с третьим информационным входом коммутатора, дополнительный управляющий Вход которого соединен с входом признака операции преобразования в дополнительный код устройства.