Устройство для адресации контролируемого блока памяти

Иллюстрации

Показать всеРеферат

Изобретение относится к вычислительной технике , в частности, к устройствам для контроля запоминающих устройств, и может использоваться в устройствах для формирования испытательной последовательности адресов строк и/или столбцов. Цель изобретения - повышение достоверности контроля. Устройство содержит генератор 1 псевдослучайных сигналов, группы 2 и 3 элементов ИЛИ, счетчики 4 и 5, блоки 6 и 7 памяти, группы 8 и 9 элементов И, группы 10 и 11 элементов суммирования по модулю два и сумматор 12. Устройство позволяет формировать псевдослучайную последовательность адресов как "контрольных", так и "фоновых" ячеек памяти с заданным законом распределения. Это позволяет, в свою очередь, подобрать закон распределения "контрольных" и "фоновых" ячеек таким образом, чтобы наиболее эффективно контролировать запоминающее устройство. Задача формирования испытательной последовательности адресов решается за счет того, что вводятся генератор псевдослучайных сигналов, первая и вторая группы элементов ИЛИ, первый и второй блоки памяти. 1 ил.

СОЮЗ СОВЕТСНИХ.

СОЦИАЛИСТИЧЕСНИХ

РЕСПУБЛИН (51) 4 С 06 F 12/00

ОПИСАНИЕ ИЗОБРЕТЕНИЯ

ГОСУДАРСТВЕННЫЙ КОМИТЕТ

ПО ИЗОБРЕТЕНИЯМ. И ОТКРЫТИЯМ

ПРИ ГКНТ СССР

1 (21) 4328491/24-24 (22) 17,11,87 (46) 15.08,89. Бюл. № 30 (72) С,Л,Скалабан и В.С.Штолик (53) 681,327.6(088.8) (56) Авторское свидетельство СССР № 612287, кл, G 11 С 29/00, 1975.

Патент США № 4442519, кл. G ll .С 29/00, опублик. 1984, (54) УСТРОЙСТВО ДЛЯ АДРЕСАЦИИ КОНТРОЛИРУЕМОГО БЛОКА ПАМЯТИ (57) Изобретение относится к вычислительной технике, в частности к .устройствам для контроля запоминаюших устройств, и может использоваться в устройствах для формирования испытательной последовательности адресов строк и/или столбцов. Цель изобретения — повышение достоверности контроля. Устройство содержит

2 генератор 1 псевдослучайных сигналов, группы 2 и 3 элементов ИЛИ, счетчики

4 и 5, блоки 6 и 7 памяти, группы

8 и 9 элементов И, группы 10 и 11 элементов суммирования по модулю два и сумматор 12. Устройство позволяет формировать псевдослучайную последовательность адресов как "контрольных", так и "фоновых" ячеек памяти с заданным законом распределения.

Это позволяет, в свою очередь, подобрать закон распределения "контрольных" и ".фоновых" ячеек таким образом, чтобы наиболее эффективно контролировать запоминающее устройствб.

Задача формирования испытательной последовательности адресов решается за счет того, что вводятся генератор ,псевдослучайных сигналов, первая и вторая группы элементов ИЛИ, первый и второй блоки. памяти. 1 ил.

3 !501068

Изобретение относится к вычислительной технике, в частности к устройствам для контроля запоминающих устройств, и может быть использовано в этих устройствах для формирования испытательной последовательности адресов строк и/или столбцов.

Цель изобретения — повьппение достоверности контроля. !р

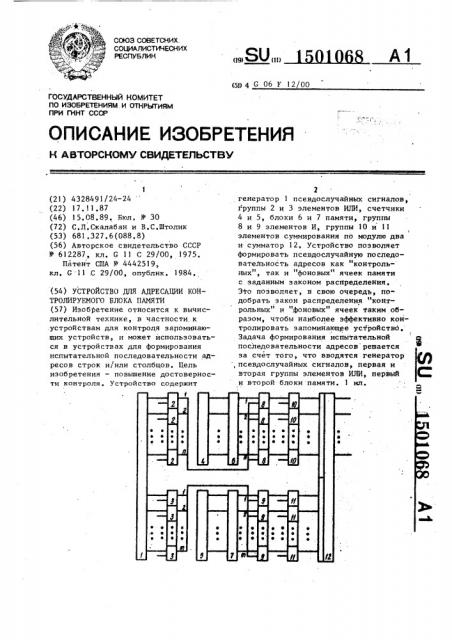

На чертеже представлена структурная схема устройства„

Устройство состоит из генератора

1 псевдослучайных сигналов, первой

2 и второй 3 групп элементов ИЛИ, !5 первого 4 и второго 5 счетчиков, пер-вого 6 и второго 7 блоков памяти, первой 8 и второй 9 групп.. элементов

И, первой 10 и второй 1) групп элементов суммирования по модулю два и 20 сумматора 12, Устройство работает следующим образом, Первоначально производится запись 25 информации в блоки 6 и 7 памяти.

Эта информация определяет характери"

Стики генерируемой последовательности адресов. Кроме того, устанавливаются управляющие сигналы на вторых 30 входах элементов ИЛИ 2 и 3 и элементов 10 и 11 суммирования по модулю два. Элемент ИЛИ 2, счетчик 4, блок б памяти, элемент И 8, элемент 10 суммирования по модулю два определяют последовательность адресов контрольных ячеек. Элемент ИЛИ 3, счетчик

5,блок 7 памяти, элемент И 9, элемент ll суммирования по модулю два определяют смещение фоновых ячеек 40 относительно текущей контрольной ячейки и, таким образом, определяют последовательность адресов фоновых ячеек. Если на вторых входах элементов ИЛИ 2 и 3 устанавливаются уровни "1", то на вторых входах элементов И 8 и 9 также устанавливаются уровни "1", при этом устройство формирует детерминированную последовательность адресов, В этом случае счетчики 4 и 5 вырабатывают сигналы, которые, поступая на адресные входы блоков 6 и 7 памяти, выбирают соответственно адресные последователь-ности КоНТрп.ãï:,Hûõ и фоновых ячеек, которые снимаются с информационных выходов блоков 6 и 7 памяти, проходят ерез элементы И 8 и 9 и элементы

10 и 11 суммир<.павия по модулю дв»

4 (с возможностью поразрядного инвертирования управляющими сигналами, поступающими на вторые входы элементов 10 и II) и поступают соответственно на первую и вторую группы входов сумматора 12. Сумматор 12 вырабатывает результирующую последовательность адресов. Заполнение блоков

6 и 7 определяет такие характеристики. адресной последовательности, как объем проверяемой памяти, убывающий или возрастающий характер последовательности, маскирование адресов, контроль произвольно выбранной области памяти. Если на вторых входах элементов ИЛИ 2 и 3 устанавливаются уровни "0" и возможно уровни "1", то устройство формирует псевдослучайную последовательность адресов с заданным законом распределения.

В этом случае вероятность появления

"1" на выходе одного из элементов

И 8 и 9 определяется как произведение вероятности появления "1" на выходе соответствующего разряда блоков памяти 6 и 7, которая, в свою очередь, зависит от заполнения блоков памяти, и вероятности появления

"1" на выходе соответствующего элемента ИЛИ 2 или 3, которая. равна

0 5 если на- втором входе этого элемента ИЛИ установлен уровень "0", и 1,0, если на втором входе этого элемента ИЛИ установлен уровень "1";

Управляющий сигнал на втором входе соответствующего элемента 10 или 11 суммирования по модулю два определяет-будет ли произведена инверсия сигнала, поступающего на первый вход этого элемента. В случае инверсии вероятность появления "0" на выходе этого элемента равна вероятности появления "1" на первом входе этого элемента. Сумматор 12, как и s случае детерминированной последовательности, вырабатывает, результирующую последовательность адресов.

Формула изобретения

Устройство для адресации контролируемого блока памяти, содержащее первый и второй счетчики, первую и вторую группы элементов суммирования пр модулю два, первую и вторую груп"пы элементов И и сумматор, выходы которого являются адресными выходаСоставитель С.Нустенко

Редактор Л,Пчолинская Техред М.Ходанич Корректор О.Ципле

Заказ 4870/46

Подписное

Тираж 668

ВНИИПИ Государственного комитета по изобретениям и открытиям при ГКНТ СССР

113035, Москва, Ж-35, Раушская наб., д. 4/5

Производственно-издательский комбинат "Патент", r.Ужгород, ул. Гагарина, 101

5 1 ми устройства, о т л и ч а ю щ ее с я тем, что, с целью повышения достоверности контроля, оно содержит генератор псевдослучайных сигналов, первую и вторую группы элементов

ИЛИ, первый и второй блоки памяти, причем выходы генератора псевдослучайных сигналов соединены с первыми входами элементов ИЛИ первой и второй групп, вторые входы элементов

ИЛИ первой и второй групп являются входами задания режима первой группы устройства, выходы первого и второго счетчиков соединены с адресными входами соответственно первого и второго блоков памяти, информацион501068 6 ные выходы которых соединены с первыми входами элементов И соответственно первой и второй групп, выходы

5 элементов ИЛИ первой и второй групп соединены соответственно с вторыми входами элементов И первой и второй групп, выходы которых соединены с первыми входами элементов суммирования, по модулю два соответственно первой и второй групп, вторые входы, которых являются входами задания режима второй группы устройства, выходы элементов суммирования по модулю два первой и второй групп соединены соответственно с входами первой и второй групп сумматора,