Устройство для выделения изображений объектов в бинарном изображении

Иллюстрации

Показать всеРеферат

Изобретение касается распознавания образцов и может быть использовано, например, в устройствах технического зрения. Цель изобретения - повышение быстродействия - достигается введением дополнительной связи в устройство, ускоряющей процесс передачи данных в его смежные ячейки. Устройство содержит N одинаковых ячеек, содержащих элемент И-ИЛИ, четыре элемента И-НЕ и элемент И. В каждой ячейке управляющие входы соединены с выходами элементов И-ИЛИ смежных ячеек. Количество ячеек и их организация в устройство совпадают с количеством элементов разложения и организацией входной бинарной информации. 3 ил.

СОЮЗ СОВЕТСКИХ

СОЦИАЛИСТИЧЕСКИХ

РЕСПУБЛИК (51> 4 G 06 K 9/46

ОПИСАНИЕ ИЗОБРЕТЕНИЯ

К АВТОРСКОМУ СВИДЕТЕЛЬСТВУ

ГОСУДАРСТВЕННЫЙ КОМИТЕТ

ПО ИЗОБРЕТЕНИЯМ И ОТКРЫТИЯМ

ПРИ ГКНТ СССР (21) 4244481/24-24 (22) 18.03.87 (46) 15.08.89. Бюл. Х - 30 (71) Физико-механический институт

АН УССР, Специальное конструкторскотехнологическое бюро Физико-механического института АН УССР и Институт геологии и геохимии горючих ископаемых АН УССР (72) А.Б. Лозинский, Н).В. Ивченко и Б.П. Русин (53) 681.327.12(088.8) (56) Авторское свидетельство СССР

Р 974383, кл. G 06 К 9/00, 198 1.

Авторское свидетельство СССР

Р 1317465, кл. G 06 К 9/46, 1986, Изобретение относится к технике распознавания образов и может быть использовано, например, в устройствах технического зрения.

Цель изобретения — повлппение быстродействия устройства.

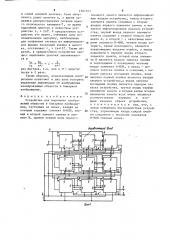

" На фиг. 1 показана функциональная схема устройства; на фиг. 2 — функциональная схема ячейки устройства; на фиг. 3 — последовательность выделения образов.

Устройство для выделения изображений объектов в бинарном изображении (фиг. 1) включает N одинаковых ячеек 1, количество которых и их органи„„SU„„150110? А 1

2 (54) УСТРОЙСТВО ДЛЯ ВЫЦ! .ЛЕН1И ИЗОБРАЖЕНИЙ ОБЪЕКТОВ В БИНАРНОМ ИЗОБРАЖЕНИИ (57) Изобретение касается распознавания образцов и может быть использовано, например, в устройствах технического зрения. Цель изобретения повьппение быстродействия — достигается введением дополнительной связи в устройство, ускоряющей процесс передачи данных в его смежные ячейки.

Устройство содержит Н одинаковых ячеек, содержащих элемент И-ИЛИ, четыре элемента И-HE и элемент И. В каждой ячейке управляющие входы соединены с выходами элементов И-ИЛИ смежных ячеек, Количество ячеек и их организация в устройство совпадают с количеством элементов разложения и организацией входной бинарной информации.

3 ил. зация в устройстве совпадает с количеством элементов разложения и органиэацией входной бинарной информации, причем вход 2 запуска первой ячейки является входом запуска устройства, выход 3 запуска последней ячейки является выходом запуска устройства, информационные входы ячеек являются информационным входом 4 устройства, первые информационные выходы ячеек являются информационным выходом 5 устройства, вторые информационные выходы ячеек соединены с управляющими входами смежных ячеек, первлп и второй вход сброса являются первым 6 и

3 l501 107 вторым 7 входами сброса устройства, выход запуска каждой предьдущей ячейки соединен с входом запуска каждой предыдущей ячейки.

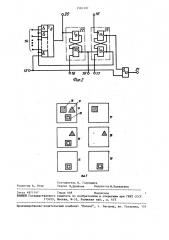

Ячейка (фиг. 2) содержит элемент

И-ИЛИ 8, с первого по четвертый элементы И-НЕ 9-12, элемент И 13, группу управляющих входов 14, вход 15 запуска, информационный вход 16» пер- Ip вый 17 и второй 18 входы сброса, первый 19 и второй 20 информационные выходы, выход 21 запуска, а также второй 22 и первый 23 элементы памяти, Последовательность выделения обра- 15 зов (фиг. 3) содержит бинарное изображение 24 в первых элементах памяти ячеек устройства в начале цикла работы, бинарное иэображение 25 в первых элементах памяти после вьделения пер- 20 ого объекта, бинарное изображение 26 первых элементах памяти после выеления второго объекта, вьделенное инарное изображение 27 первого объекта во вторых элементах памяти, выцеленное бинарное изображение 28 второго объекта во вторых элементах памяти 28, вьщеленное бинарное изобраение 29 третьего объекта во вторых лементах памяти, а также первый, торой и третий выделяемые образы

30-32.

Ячейка работает следующим образом.

Если хотя бы на один из входов !4 (фиг. 2) группы управляющих входов ячейки поступает от смежных ячеек 1 и в первый элемент 23 памяти (фиг.2) записана "1, то на выходе элемента

И-ИЛИ 8 (второй информационный выход ячейки) устанавливается 1", которая 40 записывается во второй элемент 22 памяти, с выхода которого поступает на второй вход первого элемента 23 памяти и устанавливает его в состояние

"0". Если на все управляющие входы 14 45 группы (фиг, 2) ячейки поступают сигналы "0" и первый элемент 23 памяти находится в состоянии "1", то второй элемент 22 памяти устанавливается в состояние "1" при поступлении импуль 50 са "1" на вход 15 запуска ячейки (фиг. 2), прохождение которого на соответствующий выход запрещается элементом И 13. Импульс запуска проходит через ячейку не производя никаких действий при состоянии первого элемента 23 памяти "0".

Устройство работает следующим образом, !!осле очистки первых элементов 23 памяти (фиг. 2) ячеек импульсом, подаваемым на вход 17 их сброса (фиг,.2), производится запись каждого элемента бинарного иэображения в соответствующую ему ячейку. При подаче импульса

"1" на вход запуска первой ячейки (информационный вход 16, фиг. 2) он проходит последовательно через ячейки устройства, в первые элементы памяти которых записан "0", и задерживается ячейкой, в первый момент памяти которой записана "1". На втором информационном выходе этой ячейки появляется "1", поступающая на управляющие входы смежных ячеек устройства (фиг. 1} и переводящая в состояние "1" те из них, в первые элементы памяти которых записана "1". Это приводит к распространению во все стороны от инициированной ячейки волны

"1" через ячейки, хранящие элементы иэображения объекта, вьделению его и запоминанию во вторых элементах памяти, Одновременно происходит стирание информации в первых элементах памяти тех Ячеек, которые перешли в состояние "1", и возвращение ячеек в состояние О . По окончании процесса вьделения информация об изображении объекта считывается из вторых элементов памяти. После подачи импульса на вход сброса вторых элементов памяти ячеек устройства производится вьделение изображения следующего объекта повторной подачей импульса запуска, Прохождение импульса запуска на выход устройства свидетельствует о том, что в изображении невыделенных изображений объектов больше нет. После выделения изображений всех объектов первые элементы памяти всех ячеек оказываются очищенными и могут быть сразу использованы для записи нового изображения.

Изобретение обеспечивает повышение быстродействия всего устройства в два раза, поскольку при прохождении сигнала через ячейку на выход связи он испытывает задержку распространения только на элементе И-ИЛИ, т,е, на одном логическом элементе против двух, как в известном устройстве. Процесс выделения образа можно рассматривать как параллельное выделение цепочек единичных элементов изображения, поэтому время вьделения пропорционально количеству элементов

5 1SO в самой длинной цепочке. Если обозначить длину цепочки n, a нремя задержки распространения сигнала одного логического элемента о, то время вьделения цепочки в известном устройстве tq = 2п с. В предлагаемом устл ройстве это время, учитывая одну дополнительную задержку, необходимую для появления сигнала на информационном выходе последней ячейки в цепоч— ке, составляет t = (и+1) ". Таким образом, н предлагаемом устройстве процесс вьделения цепочки заканчивается в

2п 2

Il+ 1 Il+ 1 раз быстрее, т.е, для и )) 1 практически в 2 раза.

Таким образом, использование изобретения позволяет в два раза ускорить выделение информации об изображении изолированных объектов н бинарном иэображении.

Формула и з о б р е т е н и я

Устройство для выделения изображений объектов н бинарном изображении, состоящее из ячеек, каждая из которых содержит элемент И-ИЛИ, первый и второй элемент памяти и элемент И, причем первый вход первого элемента памяти является информационным входом устройства, выход второго элемента памяти соединен с вторым

5 входом первого элемента памяти и является информационным выходом устройства, первый выход первого элемента памяти соединен с первым входом элемента И, а второй — с нечетными вхо1р дами элемента И-KIH, четные входы которого, кроме последнего, являются управляющими входами ячейки, а выход подключен к первому входу второго элемента памяти, второй нход элемен15 та И является входом запуска ячейки и подсоединен к последнему четному входу элемента И-ИЛИ, а выход — выходом запуска ячейки и соединен с выходом запуска последней ячейки, вход

20 запуска первой ячейки является входом запуска устройства,а выход запуска последней ячейки является выходом запуска устройства, третьи входы первых элементов памяти и вторые входы вторых элементов памяти всех ячеек являются соответственно первыми и вторыми входами сброса устройства, отличающееся тем,что,с целью повыггения быстродействия устрой30 ства, управляющие входы каждой ячейки соединен с выходами элементов

И-ИЛИ смежных ячеек, Увра5лянщий 5ход

l50ll07

Составитель И, Галенищев

Техред Л.Олийнык Корректор М. Васильева

Редактор А. Огар

Заказ 4871/47 Тираж бб8 Подписное

ВНИИПИ Государственного комитета по изобретениям и открытиям при ГКНТ СССР

113035, Москва, Ж-35, Раушская наб., д, 4/5

Производственно-издательский комбинат "Патент", г. Ужгород, ул. Гагарина, 101