Устройство для управления динамической памятью

Иллюстрации

Показать всеРеферат

Изобретение относится к вычислительной технике и может быть использовано в полупроводниковых запоминающих устройствах динамического типа. Целью изобретения является повышение быстродействия устройства. Устройство содержит регистр адреса, мультиплексор, регистр данных, первый и второй генераторы, первый и второй сдвигатели, преобразователь, дешифратор, блок подсинхронизации, арбитр. Цель изобретения достигается более полным использованием для выполнения циклов регенерации пауз между циклами обращения к памяти за счет подсинхронизации запросов на регенерацию сигналам, вырабатываемым при выполнении цикла обращения. При этом, если такая подсинхронизация имеет место, цикл регенерации всегда начинается сразу вслед за циклом обращения, т.е. в паузе между циклами обращения. 10 ил.

СОЮЗ СОВЕТСКИХ

СОЦИАЛИСТИЧЕСНИХ

РЕСПУБЛИН (5П g С 11 С 7/00

ГОСУДАРСТВЕННЫЙ НОМИТЕТ

ПО ИЗОБРЕТЕНИЯМ И ОТНРЫТИЯМ

ПРИ ГКНТ СССР (21) 4321486/24-24 (22) 26. 10.87 (46) 15.08.89. Бюл„ Ь 30 (71) Киевский завод электронных вычислительных и управляющих машин— головное предприятие Киевского производственного объединения "Электронмаш11 им. В.И. Ленина (7?) Е.Я. Белалов, В.К. Бочков, Э„В. Рудаков и С.П. Саламатов (53) 681. 327. 6 (088. 8) (56) Полупроводниковые запоминающие устройства и их применение / Под. ред. А.Ю. Гордонова. И.: Радио и связь, 1981, с. 135, рис. 3.24.

Авторское свидетельство СССР

Р 1256096, кл. G 11 С i 1/00, 1985. (54) УСТРОЙСТВО ДЛЯ УПРАВЛЕНИЯ ДИНАМИЧЕСКОЙ ПАМЯТЬЮ (5?) Изобретение относится к вычис лительной технике и может быть исИзобретение относится к вычислительной технике и может быть исполь зовано в полупроводниковых запоминающих устройствах динамического типа.

Цель изобретения — повьппение быстродействия устройства.

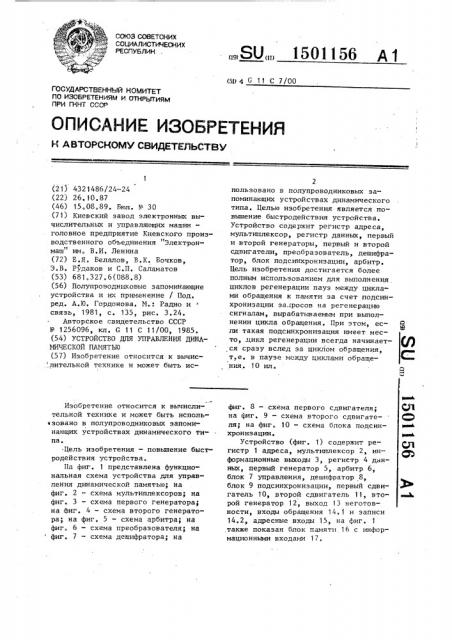

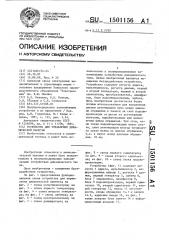

На фиг. 1 представлена функциональная схема устройства для управления динамической памятью; на фиг. 2 — схема мультиплексоров; на фиг. 3 — схема первого генератора; на фиг. 4 — схема второго генератора; на фиг. 5 — схема арбитра; на фиг. б — схема преобразователя; на фиг. 7 — схема дешифратора; на

„„80„„1501156 А 1 пользовано в полупроводниковых запоминающих устройствах динамического типа. Целью изобретения является повышение быстродействия устройства.

Устройство содержит регистр адреса, мультиплексор, регистр данных, первый и второй генераторы, первый и второй сдвигатели, преобразователь, дешифратор, блок подсинхронизации, арбитр.

Цель изобретения достигается более полным использованием для выполнения циклов регенерации пауз между циклами обращения к памяти за счет подсинхронизации за. росов на регенерацию сигналам, вырабатываемым при выполнении цикла обращения. При этом, если такая подсинхронизация имеет место, .цикл регенерации всегда начинается сразу вслед за циклом обращения, т.е. в паузе между циклами обращения. 10 ил. фиг. 8 — схема первого сдвигателя, на фиг, 9 — схема второго сдвигателя; на фиг. 10 — схема блока подсинхронизации.

Устройство (фиг. 1) содержит регистр 1 адреса, мультиплексор 2, информационные выходы 3, регистр 4 данных, первый генератор 5, арбитр 6, блок 7 управления, дешифратор 8, блок 9 подсинхронизации, первый сдвигатель 10, второй сдвигатель 11, второй генератор 12, выход 13 неготовности, входы обращения 14. 1 и записи

14.2, адресные входы 15, на фиг. также показан блок памяти 16 с информационными входами 17, 3 15011

Иультиплексор 2 (фиг. 2) содержит формирователи сигналов 18-23.

Первый генератор 5 (фиг. 3) содержит инверторы 24 и 25, конденсаторы

26 и 27, резонатор 28, резистор 29.

Второй генератор 12 (фиг. 4) содержит триггер шмитта 30, инвертор

31, конденсатор 32, регистр 33.

Арбитр 6 (фиг. 5) содержит элементы И-НЕ 34-37, НЕ 38, 39, И-ИЗИ 40.

Преобразователь (фиг. 6) содержит элементы И 41, НЕ 42, ИЛИ 43 И-НЕ

44, НЕ 45-47.

Дешифратор 8 (фиг. 7) содержит 15 дешифратор 48, формирователи сигналов 49 и 50.

Первый сдвигатель 10 (фиг. 8) содержит регистры 51 и 52.

Блок 9 подсинхронизации (фиг. 10) 20 содержит элементы И-НЕ 53 и 54, НЕ

55 и 56, триггеры 57 и 58.

Блок 16 памяти содержит динамические элементы памяти, требующие выполнения периодической регенерации. Поэтому устройство имеет следующие режимы работы: обмен и регенерация.

В режиме обмена внешний сигнал

"Обращение" поступает на вход 14.1 и далее на первый сдвигатель lO ко- 30 торый выполняет синхронизацию этого сигнала. После этого сигнал синхронного признака обращения с регистра

51 поступает на вход арбитра 6. Арбитр 6.определяет режим работы и выдает сигналы: "Режим обмена" (с элемента 40), "Запуск первого сдвигателя" (с элемента 37), "Занято" (с элемента 36), после чего сдвигатель 10 вырабатывает временную ди- 40 аграмму работы устройства, а преобразователь 7,вырабатывает управля-, ющие сигналы "Строб адреса столбца" (на элементе 43) и "Выбор посылки адреса" (на элементе 44), поступающие на мультиплексор 2, "Код операции" (на элементе 42), поступающий ма блок 16 памяти и "Ответ" (на элементе 41), поступающий на выход 3.

Адрес поступает с входов 15 в регистр 1, а затем на мультиплексор 2.

Дешифратор 8 выдает "Строб адреса строки" на выбранные микросхемы памяти.

Иультиплексор 2 выдает две посылки адреса и Строб адреса столбца" в блок 16 памяти.

56 4

В зависимости от состояния входа

14.2 "Запись" устройства выполняет запись или чтение.

В режиме регенерации устройство работает следующим образом.

Второй генератор 12 вырабатывает короткие отрицательные импульсы с частотой регенерации и выдает их в блок 9 подсинхронизации. Элемент 54 формирует положительный фронт по отрицательному сигналу Занято" на элементе 36, затем триггер 58 выдает сигнал "Запрос регенерации" (низкий уровень) на второй сдвигатель i11 и триггер 57 блока 9. Триггер 57 устанавливается в "0 и предотвращает повторную выдачу запроса на регенерацию с приходом очередного сигнала

"Занято". В конце импульса с генератора 12 триггер 57 устанавливается в "1" по "Б"-входу, возвращаясь таким образом в исходное состояние.

В случае длительного отсутствия обращения к памяти, на выходе 36 высокий уровень, элемент 54 формирует положительный фронт после оконча-.. ния импульса с генератора 12, затем триггер 58 выдает "Запрос регенерации" на второй сдвигатель, а триггер

57 устанавливается в "1" по "S"-входу, подготавливая тем самым прием 1ч очередного сигнала с генератора 12.

Нулевой триггер сдвигателя 11 выпол няет синхронизацию запроса регенерации. Затем арбитр 6 выполняет арбитраж запросов и выдает сигнал "Режим регенерации" на сдвигатель 11, который формирует временную диаграмму цикла регенерации и дает сигнал

"Сброс" на триггер 58 ° Преобразователь выдает сигнал "Выбор посылки" о р (с элемента 44) в мультиплексор 2.

Дешифратор 8 выдает стробы адреса строки с элемента 50 в блок 16 памяти.

Мультиплексор 2 выдает строб адреса столбца (с элемента 20) в блок

16 памяти.

Таким образом, предлагаемое устройство позволяет уменьшить вероятность асинхронного появления запроса регенерации по отношению к сигналам обращения за счет подсинхронизации, что сокращает связанные с этим потери времени и обеспечивает большую прозрачность устройства для обращений со стороны интерфейса.

5 ,15011

Формула изобретения

Устройство для управления динамической памятью, содержащее мультиплексор, выходы которого являются

5 адресными выходами устройства, регистр данных, информационные входы и выходы которого являются соответственно информационными входами и 1р выходами устройства, преобразователь, первый генератор, арбитр, дешифратор, о т л и ч а ю щ е е с я тем, что, с целью повышения быстродействия устройства, в него введены 15 второй генератор, блок подсинхрониэации, первый и второй сдвигатели, регистр адреса, причем первый выход второго сдвигателя .соединен с первым входом арбитра, второй выход второго сдвигателя подключен к старшим разрядам информационных входов первой группы мультиплексора, младшие разряды информационных входов первой и второй групп которого со- 25 единены с выходами первой группы регистра адреса, информационные входы которого являются адресными входами е устройства, а выходы второй группы подключены к информационным входам gp первой группы дешифратора, информационнь1е входы второй группы которого соединены с вторым входом арбитра и с третьим выходом второго сдвигателя, четвеРтый и пятый выхОды кото» 35 рого подключены соответственно к первому входу блока подсинхронизации и к. третьему входу арбитра, входы с четвертого по восьмой которого соединены соответственно с вторым, 40 третьим, четвертым, пятым и седьмым .выходами первого сдвигателя, пятый, 56 6 шестой и седьмой выходы которого подключены соответственно к первому, второму и третьему входам преобразователя, первый и второй выходы которого являются соответственно выходами неготовности и записи устройства, третий выход преобразователя соединен со старшими разрядами информационных входов второй группы мультиплексора, управляющий вход которого подключен к четвертому выходу преобразователя, четвертый и пятый входы которого соединены соответственно с первйм выходом арбитра и первым выходом первого сдвигателя, первый и третий информационные входы которого подключены соответственно к первому и второму выходам арбитра, третий выход которого соединен с установочным входом первого сдвигателя, синхровход которого подключен к выходу первого генератора и к синхро1входу второго сдвигателя, первый и второй информационные входы которого соединены соответственно с выходом блока подсинхрониэации и с четвертым выходом арбитра, первый выход которого подключен к второму входу блока подсинхронизации и к входу выборки дешифратора, выходы которого являются выходами выборки устройства, седьмой выход первого сдвигателя соединен с синхровходом регистра данных, третий вход блока подсинхрониэации подключен к выходу второго генератора, шестой вход преобразователя является входом записи устройства, второй информационный вход первого сдвигателя соединен с синхровходом регистра адреса и является входом обращения устройства.

150115б

14.1

1Ф2

i e

С1

СТ

Фиг. 2

1501156

1501156 и(У4, ХБ еУЖР еа У7И;Фд ю@.3М,И

1501156 иа У438 вам

fcrzs sa ио 68

Фиг /О