Способ контроля повреждения и дешифрирующих устройствах числовой кодовой автоблокировки переменного тока

Иллюстрации

Показать всеРеферат

Подписная группа Л5 83

Д. А. Коган

БЕСКОНТАКТНЫЙ ДЕШИФРАТОР ЧИСЛСВОГО КОДА

АВТОБЛОКИРОВКИ ПЕРЕМЕННОГО ТОКА

Известны бесконтактные дешифраторы числового кода автоблокировки переменного тока, содержащие триггеры контроля первого

Ж и второго 3 импульсов кода, одновибраторы, усилители постоянного тока, схему совпадения на полупроводниковых триодах и магнитные усилители с выходом на сигнальные реле.

Предлагаемый дешифратор отличается от известных тем, что, с целью предупреждения появления более разрешающего показания светофора из-за повреждения элементов и импульсных помех, триггеры, усилители и потенциометрическая схема совпадения выполнены малочувствительными, с непосредственной связью по напряжению. Входы схемы совпадения подключены к триггеру, выполняющему функции путевого реле, непосредственно и через линию задержки на длительность первого импульса цикла. А выходы триггеров Ж и 3 соединены со своими сигнальными реле через магнитные усилители, работающие в импульсном режиме управления и блокируемые повреждением цепей.

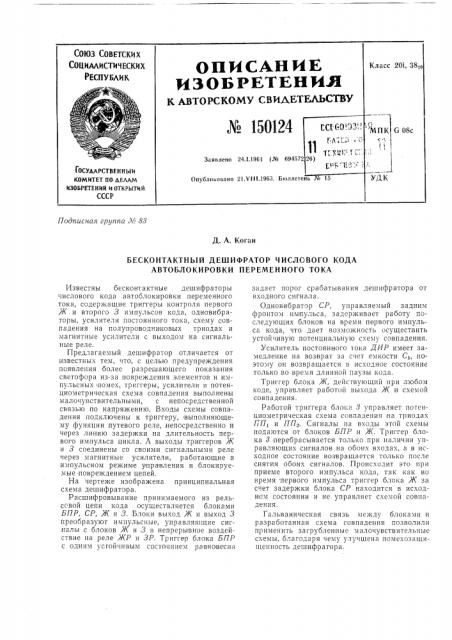

На чертеже изображена принципиальная схема дешифратора.

Расшифровывание принимаемого из рельссвой цепи кода осуществляется блоками

БПР, СР, Ж и 3. Блоки выход Ж и выход 3 преобразуют импульсные, управляющие сиг,нaëû с блоков Ж и 3 в непрерывное воздействие на реле ЖР и ЗР. Триггер блока БЛР с одним устойчивым состоянием равновеси» задает порог срабатывания дешифратора от входного сигнала.

Одновибратор СР, управляемый задним фронтом импульса, задерживает работу последующих блоков на время первого импульс» кода, что дает возможность осуществить устойчивую потенциальную схему совпадения.

Усилитель постоянного тока ДИР имеет замедление на возврат за счет емкости С1, поэтому он возвращается в исходное состояние только во время длинной паузы кода.

Триггер блока Ж, действующий при любом коде, управляет работой вь хода Ж и схемой совпадения.

Работой триггера блока 3 управляет потснциометрическая схема совпадения на триодах

ПП, и ПП>. Сигналы на входы этой схемы подаются от блоков БПР и Ж. Триггер блока 8 перебрасывается только при наличии управляющих сигналов на обоих входах, а в исходное состояние возвращается только после снятия обоих сигналов. Происходит это при приеме второго импульса кода, так как во время первого импульса триггер блока Ж за счет задержки блока СР находится в ис одном состоянии и не управляет схемой совпадения.

Гальваническая связь между блоками и разработанная схема совпадения позволили применить загрубленные малочувствительные схемы, благодаря чему улучшена помехозащищенность дешифратора.