Синтезатор частот

Иллюстрации

Показать всеРеферат

Изобретение относится к радиотехнике. Цель изобретения - повышение спектральной чистоты выходного сигнала. Синтезатор частот содержит опорный г-р 1, фазовый детектор 2, фильтр 3 нижних частот, перестраиваемый г-р 4, накопитель 5 кода, двухканальный распределитель 6 сигналов, мультиплексор 7, ЦАП 8, интегрирующее звено 9 и эл-т разряда 10. Сигнал г-ра 1 поступает на фазовый детектор 2 и синхронизирует работу кольца фазовой автоподстройки г-ра 4. Т.к на входы фазового детектора 2 поступают периодические сигналы, то в режиме синхронизма кольца фазовой автоподстройки на его выходе формируется сигнал, пропорциональный разности фаз сравниваемых сигналов. Далее фильтр 3 осуществляет фильтрацию помех, равных или кратных частоте сравнения. При этом коэффициент ослабления помех не зависит от воздействия таких факторов, как колебания температуры, уход напряжения источников питания, старение эл-тов. 2 ил.

СОЮЗ СОВЕТСКИХ.

СОЦИАЛИСТИЧЕСКИХ

РЕСПУБЛИК.SU 150l2 (5п 4 Н 03 1. 7/18

OllHCAHHE ИЗОБРЕТЕНИЯ

К А ВТОРСКОМY СВИДЕТЕЛЬСТВУ (21) 4326776/? 4-09 (2?) 10. 11.87 (46) 15.08.89. Бюл. Н 30 (72) В.И.Никифоров (53) 621.373.44 (ORR.R) ГОСУДАРСТВЕННЫЙ КОМИТЕТ, flO ИЗОБРЕТЕНИЯМ И ОТКРЫТИЯМ

ПРИ ГКНТ СССР (56) Авторское свидетельство СССР

М - 1312732, кл, Н 03 1 7/18,12,12.85.

Патент Великобритании 1447418, кл. Н 3 А, 25.08.76. (54) СИНТЕЗАТОР ЧАСТОТ (57) Изобретение относится к радиотехнике. Цель изобретения — повышение спектральной частоты выходного сигнала. Синтезатор частот содержит опорный г-р 1, фазовый детектор 2, .фильтр 3 нижних частот, перестраиваемый r-р 4, накопитель 5 кода, двухка2 нальный распределитель 6 сигналов, мультиплексор 7, ЦАП 8, интегрирующее звено 9 и эл-т разряда 10. Сигнал г-ра 1 поступает на фазовый детектор

2 и синхронизирует работу кольца фазовой автоподстройки г-ра 4. Так как на входы фазового детектора 2 по» ступают периодические сигналы, то в режиме синхронизма кольца фаэовой автоподстройки на его выходе формируется сигнал, пропорциональный разности фаз сравниваемых сигналов. Далее фильтр 3 осуществляет фильтрацию помех, равных или кратных частоте сравнения. При этом коэдх чп иент ослабления помех не зависит от воздействия таких факторов, как колебания температуры, уход напряжения источников питания, старение эл-тов. 2 ил.

1501265

Изобретение относится к радиотехнике и может быть использовано для получения сетки стабильных частот в приемопередающей и измерительной аппаратуре.

Целью изобретения является повышение спектральной чистоты выходного

F=FP/А=ЬРР, где А и P — целые положительные числа;

hF = Г /А — шаг сетки частот.

При этом А — величина постоянная при выбранном шаге сетки частот ЬГ, а P — величина переменная, равная требуемому значению модуля накопителя 5.

Выходной сигнал перестраиваемого

1 генератора 4 с периодом Т " — (вреР менная диаграмма а) поступает на

55 сигнала.

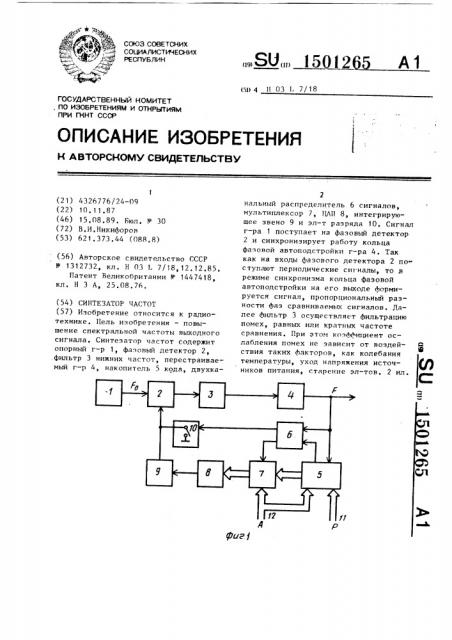

На фиг.1 представлена структурная 10 электрическая схема синтезатора частот; на фиг.2 — временные диаграммы его работы.

Синтезатор частот содержит опорный генератор 1, фазовый детектор 2, 15 фильтр 3 нижних частот, перестраиваемый генератор 4, накопитель 5 кода, двухканальный распределитель 6 сигналов, мультиплексор 7, цифроаналоговый преобразователь (ЦАП) 8, интегрирующее звено 9, элемент разряда 10. На фиг.2 изображено: импульсы с выхода перестраиваемого генератора (фиг.2а), выходной сигнал накопителя кода (фиг.2б), сигнал с выхода

25 переполнения накопителя кода (фиг.2в), сигнал с первого выхода двухканального распределителя импульсов (фиг.2г), сигнал с второго выхода двухканального распределителя сигналов (фиг.2д), .сигнал с выхода мультиплексора (фиг,2е), сигнал на выходе интегрирующего звена (фиг.2a), импульсы опорного генератора (фиг.2з).

Синтезатор частот работает следующим образом.

Выходной сигнал опорного генератора 1 с частотой F поступает на первый вход фазового детектора 2 и синхронизирует работу кольца фазовой

40 автоподстройки. В режиме синхрониэма

"астота F перестраиваемого генератора 4 определяется выражением тактовый вход накопителя 5 и обеспечивает синхронизацию работы накопителя 5. В пределах емкости (модуля) Р накопителя 5 изменение информации а(KT) на его выходе происходит с постоянным приращением А (временная диаграмма б), при этом на выходе переполнения накопителя 5 присутствует уровень "0" (временная диаграмма в).

При значениях текущей информации а(ЕТ), превышающих величину Р, на выходе переноса накопителя 5 формируется уровень "1" а значение остатка R(KT) передается на второй кодовый вход мультиплексора 7. Сигнал переполнения с выхода накопителя 5 поступает на вход однократного запуска двухканального распределителя 6, синхронизация работы которого также осуществляется выходным сигналом перестраиваемого генератора 4.

В обоих каналах двухканального распределителя 6 формирование передних фронтов выходных сигналов синхронно и определяется моментом прихода уровня 1

Длительность выходных сигналов двухканального распределителя 6 отличается на один период Т (временные диаграммы г и д), причем длительность сигнала на выходе первого канала равна t = 1Т, на выходе второго канала с = (1 + 1)Т, где 1 — целое число в пределах 161ф/ф

Выходной сигнал второго канала двухканального распределителя 6 поступает на управляющий вход мультиплексора 7 и осуществляет его коммутацию. При этом в течение времени t мультиплексор пропускает на выход информацию К(КТ) со второго кодового входа, а при отсутствии импульса на выход поступает значение числа А с первого кодового входа мультиплексора 7 (временная диаграмма е). ЦАП 8 преобразует выходной переменный код мультиплексора 7 в последовательность ступенчатого напряжения.

Интегрирование ступенчатого напряжения интегрирующим звеном 9 вызывает линейное нарастание сигнала на его выходе, причем крутизна этого процесса пропорциональна текущему значению кода на выходе мультиплексора 7. Выход интегрирующего звена

9 подключен к элементу разряда 10, 1501265

„кс

v «Г= и мин — мокс

55 который н течение длительно<..ти

< импульса, поступающего на его управляющий вход, обеспечивает разряд интегрирующего звена 9 и его установ5

Kv в исходное состояние. В результате сигнал на выходе интегрирующего звена 9 имеет вид, изображенный на временной диаграмме 17. При этом на первом временном интервале

0

К= целой части отношения / Г/F./ ).

Изменение информации на выходе накопителя 5 происходит в дискретные моменты времени КТ, период последовательности импульсов на выходе .переполнения накопителя 5 изменяется дискретно и не равен периоду Т, частоты опорного генератора (временная диаграмма з). Однако средний период последовательности (в приведен- З0 ном примере эа десять циклов счета) точно соответствует периоду Т .

На втором временном интервале линейный заряд интегрирующего звена

9 происходит со скоростью, пропорциональной текущему значению кода остатка R.L, rye L — коэффициент передачи ЦАП 8 и интегрирующего звена 9. На третьем временном интервале между точками 2 — 0 временной 40 диаграммы ж заряд происходит с постоянной скоростью, пропорциональной коду аргумента, т.е. А 1,, и этот сигнал имеет ясно выраженный периодический характер, причем период фор- 45 мируемого сигнала точно равен периоду

Т выходного сигнал» опорного генератора 1, в области выходных напряжений, ограниченной пунктирными линиями 50 где V„„„= 1.(А — 1), V

= К (1/А — (1 + 1)) 11,скольку на входи фазового детектора 2 поступают периодические сигналы, то т режиме синхронизма кольца фазовой автоподстройки на его выхоле формируется выходной сигнал, пропорциональный разности Лаз сравниваемых сигналов. Фильтр 3 осуществляет фильтрацию помех, равных пли кратных частоте сравнения Fo .

В качестве фазового детектора могут быть использованы различные типы фазовых детекторов, как типа выборказапоминание, так и триггерные фазовые детекторы. В последнем случае в состав фазового детектора 2 должен входить пороговый элемент, обеспечивающий формирование импульсов, необходимых для работы триггера (на фиг.1 не показано). Напряжение порога срабатывания должно удовлетворять приведенному ограничению

Таким образом, весь процесс компенсации дискретных фазовых колебаний сигнала накопителя 5 осуществляется цифровыми методами с последующим преобразованием в аналоговый сигнал, При этом уходы параметров

ЦАП 8 или интегрирующего звена 9 не отражаются на ухудшении эффекта компенсации, поскольку их весовые соотношения на втором и третьем временных интервалах остаются постоянными

А/R(KT) и не зависят от коэффициента

Следовательно, коэффициент ослабления помех синтезатора частот не зависит от воздействия таких факторов как колебания температуры, уход напряжения источников питания, ста— рение элементов °

Дополнительно в синтезаторе может быть достигнуто упрощение, поскольку для формирования сетки частот необязательно применение делителей, сумматоров напряжений и делителя частоты с переменным коэффициентом деления.

Формула и з о б р е т е н и я

Синтезатор частот, содержащий последовательно соединенные опорный генератор, фазовый детектор, фильтр нижних частот и перестраиваемый генератор, а также накопитель кода и цифроаналоговый преобразователь, вход аргумента накопителя кода является первым кодовым нходом синтезатора частот, о т л и ч а ю щ и йс я тем, что, с ill Jlf.í повышения

1501265

Вход первыи кодовый вход н второй код<»»»ь»»» вход которого подкчючены соответственно к второму выходу двухгенератора, а вход управления модулем накопителя кода является вторым кодовым входом синтезатора частот.

1(к71

30

20 6

Р И

4 6

/.Т

2

Ю

С 0 и&т) fq<)t

Составитель Ю.Ковалев

Техред . 1, Ол»»»»<»ь»к

Корректор Т.Палий

Редактор Н.1 орват

Заказ 48<1»1 5 Тираж 884 11одписное

Б<1И11П1! Г ««н< т»з< нного комитета I»o изобретениям и открытиям при ГКНТ СССР

113»)35, Москва, К- 3 <, Раушская наб., д. 4/5

Пронзя < ».»< l« -нз«ательский <»<.< .инат "Патент", г.ужгород, ул. Гагарина,101 спектральной ч»гтоты выходного сигнала, между выходом переполнения накопителя кода и вторым входом фазового детектора включены последова5 тельно соединенные двухканальный распределитель сигналов и элемент разряда, а также введены мультиплексор и интегрирующее звено, выход и вход которого подключены соответственно к второму входу фазового детектора и выходу цифроаналогового преобразователя, вход которого соединен с выходом мультиплексора, управляющий канального распределителя сигналов, к первому кодовому входу синтезатора частот и к кодовому выходу накопителя кодов, тактовый вход которого объединен с тактовым входом двухканального распределителя сигналов и подсоединен к выходу перестраиваемого