Реверсивный преобразователь двоично-десятичного кода в двоичный

Иллюстрации

Показать всеРеферат

Изобретение относится к вычислительной технике и может быть использовано для построения преобразователей больших потоков двоичной и двоично-десятичной информации. Целью изобретения является расширение функциональных возможностей за счет обеспечения преобразования целых чисел и повышение быстродействия. Поставленная цель достигается за счет того, что в реверсивный преобразователь двоично-десятичного кода в двоичный, содержащий группу масштабирующих сумматоров 1, дополнительно введены группа к-разрядных преобразователей 2 и группа коммутаторов 3. 2 ил.

СОЮЗ СОВЕТСКИХ

СОЦИАЛИСТИЧЕСНИХ

РЕСПУБЛИК

„„SU,, 150127

А1 (51) 4 Н 03 М 7/12

ОПИСАНИЕ ИЗОБРЕТЕНИЯ

К А ВТОРСКОМУ СВИДЕТЕЛЬСТВУ

ГОСУДАРСТВЕННЫЙ КОМИТЕТ

{Ю ИЭОБРЕТЕНИЯМ И ОТКРЫТИЯМ

Г1РИ ГКНТ СССР (21) 4360831/24-24 (22) 06".01,88 (46) 15.08.89. Бюл. М 30 (72) А.А.Жалковский, А.А.Шостак и Л.О.Шпаков (53) 681.325(088.8) (56) Красноголовый Б.Н., Шпилевой Б.Н. Преобразователи кодов.

Минск: Иэд-во БГУ, 1983, с. 105.

Авторское свидетельство СССР

М 1378064, кл. Н 03 М 7/12, 1986. (54) РЕВЕРСИВНЫЙ ПРЕОБРАЗОВАТЕЛЬ

ДВОИЧНО-ДЕСЯТИЧНОГО КОДА В ДВОИЧНЫЙ (57) Изобретение относится к вычислительной технике и мохет быть использовано для построения преобразователей больших потоков двоичной и двоично-десятичной информации. Целью изобретения является расширение функциональных возмокностей эа счет обеспечения преобразования целых чисел и повышения быстродействия. Поставленная цель достигается за счет того, что в реверсивный преобразователь двоична-десятичного кода в двоичный, содержащий группу масштабируюп1их сумматоров 1, дополнительно введены группа k-разрядных преобразователей

2 и группа коммутаторов 3. 2 ил.

150 1278

Изобретение относится к вычислительной технике и может быть использовано в универсальных и специализированных 3BN для построения преобразователей больших потоков двоичной и двоично-десятичной информации.

Цель изобретения — расширение функциональных возможностей эа счет обеспечения преобразования целых чисел и повышение быстродействия.

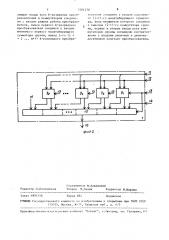

На фиг. 1 приведена блок-схема предлагаемого преобразователя, на фиг. 2 — структурная схема одного из вариантов реализации масштабирующего сумматора.

Реверсивный преобразователь двоично-десятичного кода в двоичный содержит масштабирующие сумматоры 1, 1 k-разрядные преобразователи 2, 2 „ и коммутататоры 3, — 3„„, информационные входы 4, — 4,„+, преобразуемых групп разрядов, вход 5 двоичнодесятичной константы, вход 6 двоичной константы, вход 7 режима работы и выход 8 преобразователя.

Каждый масштабируюший сумматор 1 содержит узлы 9, — 9 умножения, сумматор 10, вход 11 множимого, вход

12 множителя, управляющий вход 13, вход 14 слагаемого и вход 15 логического нуля.

В основу работы преобразователя положен следующий принцип.

При преобразовании двоично-деся гичного кода в двоичный исходный иразрядный код разбивается на группы

no k десятичных цифр в каждой. IIpeобразование происходит по схеме Горнера, т.е. первая, самая старшая, группа разрядов,преобразуется в двоичный код и умножается на двоичную константу, значение которой определяется значением k. Так, например, при k = 1 двоичная константа равна 1010, при k =,2 константа равна 1100100 и т.д. К получившемуся произведении прибавляется двоичное значение соседней, младшей, группы десятичных разрядов. Результат суммирования опять умножается на двоичную константу и суммируется с двоичным значением следующей, более младшей, группы десятичных разрядов и т.д. до тех пор, пока не будет подсуммировано двоичное значение самой младшей группы десятичных разрядов.

Преобразование из двоичного кода в двоично-десятичный происходит

55 аналогичным образом, но все действия выполняются в десятичной системе счисления. Значение двоично-десятичной константы в этом случае также зависит от количества двоичных разрядов в группах р. Так, например, при р = 3 двоично-десятичная константа равна 8, при р = 6 константа равна 64 и т.д.

В каждом иэ масштабирующих сумматоров могут выполняться операции над числами в двоичном и двоичнодесятичном кодах. При преобразовании в двоичный код они настраиваются управляющим потенциалом с входа 7 преобразователя на обработку информации в двоичном коде, а при преобразовании в двоично-десятичный код на обработку информации в двоичнодесятичном коде. На узлах 9 — 9 у умножения образуется в двухрядном коде произведение некоторого промежуточного значения преобразуемого числа, поступающего с входа 11 множимого сумматора 1, на константу, поступающую с его входа 1? множителя. Сумматор 10 осуществляет сворачивание двухрядного кода полученного произведения к однорядному.

При этом через его свободный мпадший вход 14 поступает и суммируется значение соседней, младшей, группы разрядов преобразуемого числа, а через свободный старший вход — значение

"0" с входа 15 преобразователя. Поступающий с входа 13 масштабирующего сумматора управляющий потенциал обеспечивает функционирование узлов

9„ - 9 умножения и сумматора 10 в соответствующем коде.

k-Разрядные преобразователи 2

2,„,1 предназначены для преобразования из двоично-десятичного кода в двоичный и наоборот значений групп разрядов, поступающих с входов 4 .

4 „„, . При 1с 1 и р ь 3 необходимость в преобразователях отпадает.

Управление работой преобразователей 2, — 2,„„ осуществляется потенциалом с входа 7 устройства.

Коммутаторы 3 1 — 3 предназначены для передачи на входы множителя сумматоров 1, — 1 значений либо двоично-десятичных (с входа 5 устройства), либо двоичных констант (с входа 6 устройства). Управление работой коммутаторов 3, — 3,„ осуществляется потенциалом с входа 7 преобразователя.!

501278 на передачу дваично-десятичных констант 64 с входа 5 устройства. На каждый из входов 4, — 4 подается по

5 шесть двоичных разрядов преобразуемого числа (на вход 4, — самые старшие шесть разрядов на вход 4 — сосед1 2 ние, младшие, шесть разрядов и т.д.) .

После срабатывания масштабирующих сумматоров 1, — 1 „ на выходе 8 образуется двоично-десятичный код преобразованного числа.

Ф о р м у л а и з о б р е т е н и я !

Допустим, ч го каждый масштабирующий сумматор выполнен таким образом, что множимое в нем умножается на два десятичных разряда или на восемь двоичных разрядов множителя, а количество масштабирующих сумматоров равно трем. Тогда максимальное количество преобразуемых десятичных разрядов равно 8, а максимальное количество двоичных разрядов — 24 °

Рассмотрим сначала преобразование иэ двоично-десятичного кода в двоичный. Пусть преобразуемое число равно

98356528. Перед началом выполнения операции на входах 4,, 4, 4 и 4 з устанавливаются двоичпо-десятичные значения соответственно 98, 35, 65 и 28. Управляющий потенциал с входа

7 режима работы устройства настраива- 20 ет масштабирующие сумматоры 1, — 1 на обработку двоичных кодов, преобразователи 2, — 2 — на преобразование в двоичный код, а коммутаторы

3 — 3 — на передачу двоичных конс- 25 таит 1100100 с входа 6 двоичных констант преобразователя. В масштабирующем сумматоре 1 преобразованное в преобразователе 2, в двоичный код значение 98 умножается на двоичную 30 константу, одновременно прибавляется двоичное значение числа 35, сформированное на выходе преобразователя

2 . С выхода масштабирующего сумматора 1 первый промежуточный результат преобразования поступает на вход

35 множимого блока 1, где умножается на двоичную константу, к произведению. прибавляется двоичное значение соседней, младшей, пары десятичных цифр 65, образованное на выходе преобразователя 2>. Второй промежу гочный результат в масштабирующем сумматоре 1 умножается на двоичную константу, к произведению прибавляется

45 двоичное значение чис .ла 28, полученное на выходе преобразователя 2, с выхода масштабирующего сумматора 1 считывается окончательный двоичный результат.

При преобразовании из двоичного в двоично-десятичный код на входе 7 преобразователя устанавливается управляющий потенциал, настраивающий масштабирующие сумматоры — на

Обработку двоично-десятичных кодов, преобразователи 2 — 2 — на преобо раэование из двоичного кода в двоично-десятичный, коммутаторы 3 1 — 3 —

Реверсивный преобразователь двоично-десятичного кода в двоичный, содержащий группу масштабирующих сумматоров, выход каждого масштабирую1 цего сумматора выхс диого кода группы, сроме последнего, оединен с входом множимого соседнего старшего масштабирующе го сумматора группы, выход последнего масштабирующего сумматора является информационным выходом преобразователя, вход режима работы которого соединен с управляющими входами всех масштабирующих сумматоров группы, причем каждый масштабирующий сумматор состоит из умножителя И сумматора, первый информационный вход которого соединен с выходом умножителя, второй информационный вход сумматора и вхоц умножителя являются соответственно входами слагаемого и множителя масштабирующего сумматора группы, управляющий вход которого соединен с управляющими входами сумматора и умножителя, о т !I и ч а юш и и с я тем, что, с целью расширения функциональных возможностей за счет обеспечения преобразования целых чисел и повышения бы тродействия, в него введены группы. коммутаторов и группу k-разрядных преобразователей, причем группы масштабирующих сумматоров и коммутаторов содержат по m = J — (— блоков где

У и — число разрядов выходного кода, а k — число разрядов входного кода, обрабатываемых одним масштабирующиь сумматором, а группа k-разрядных преобразователей состоит из (а+11 блоков, информационные входы первого и второго !с-разрядных преобразователей соединены соотнс гственно с информаЦионными входами первой и второй групп преобразователя, а управL

150 1278 фи22

Составитель M.Àðøàâñêèé

Техред М,яндык Корректор М.Шароши

Редактор Л.Пчолинская

Заказ 4891/56

Тираж 884

Подписное

РчИИПИ Государственного комитета по изобретениям и открытиям при ГКНТ СССР

113()35, Москва, Ж-.35, Раушская наб., д. 4/5

Производственно-издательский комбинат Патент, г.ужгород, ул. Гагарина,101 ляющие входы всех k-разрядных преобразователей и коммутаторов соединены с входом режима работы преобразователя, выход первого k-разрядного преобразователя соединен с входом множимого первого масштабирующего сумматора группы, выход i-го (i

2 ... m+1) k-разрядного преобраэователя ="oåöèíåí с входом слагаемого (i-1)-го масштабирующего сумматора, вход множителя которого соединен

5 с выходом (i-1 > -го коммутатора группы, первые и вторые входы всех коммутаторов группы соединены соответственно с входами двоичной и двоичнодес.ятичной констант преобразователя.