Устройство для приема сигналов, закодированных с избыточностью

Иллюстрации

Показать всеРеферат

Изобретение относится к электросвязи. Цель изобретения - повышение помехоустойчивости при изменении коэффициента передачи (КП) канала связи. Устройство содержит блок задержки 1, решающие блоки 2 и 3, детектор 4 качества, формирователь (Ф) 5 гипотетических сигналов, блок управления 6, блоки 7 и 10 ключей, блок свертки 8, блок сравнения 9, интегратор 11, блок памяти 12, Ф 13 пороговых уровней, управляемый делитель 14 напряжения, блок выборки и хранения 15, блок вычитания 16, пороговый блок 17, регистр 18, Ф 19 сигнала и управляемый делитель 20 частоты. На вход устройства поступают искаженные помехами двоичные сигналы, уровень которых в зависимости от КП канала связи изменяется. Если КП изменится, то отличие результатов сверток будет выше установленного порога и на регистр 18 поступит сигнал логической переменной "1", сдвиг в котором производит блок управления 6. На основании числа "1", записанных в регистре 18, Ф 19 определяет коэффициент деления для делителей 14 и 20. В результате, с учетом изменения КП, каждый раз Ф 13 формирует пороговые сигналы для детектора 4, который принимает решение о надежности принятия решения решающим блоком 2 по каждому эл-ту избыточного кодового слова. 1 ил.

СОЮЗ СОВЕТСНИХ

СОЦИАЛИСТИЧЕСКИХ

РЕСПУБЛИК (51) 4 Н 04 Ь 17/16

ОПИСАНИЕ ИЗОБРЕТЕНИЯ

Н А BTOPCKOMY СВИДЕТЕЛЬСТВУ

ГОСУДАРСТВЕННЫЙ КОМИТЕТ

ПО ИЗОБРЕТЕНИЯМ И ОТНРЫТИЯМ

ПРИ ГННТ СССР

1 (21) 4326829/24-09 (22) 10. 11.87 (46) 15.08.89. Бюп. ¹ 30 (72) В. В. Баранов, И. Б.Давыдов и А.В.Товарницкий (53) 62 1.394 .62(088 .8) (56) Авторское свидетельство СССР № 1265827, кл . G 08 С 19/28 1985. (54) УСТРОЙСТВО ДЛЯ ПРИЕМА СИГНАЛОВ, ЗАКОДИРОВАННЫХ С ИЗБЫТОЧНОСТЬЮ (57) Изобретение относится к электросвязи. Цель изобретения — повышение помехоустойчивости при .изменении коэффициента передачи (КП) канала связи. Устр-во содержит блок задержки 1, решающие блоки 2 и 3, детектор

4 качества, формирователь (Ф) 5 гипотетических сигналов, блок управления 6, блоки 7 и 10 ключей, блок свертки 8, блок сравнения 9, интегратор 11, блок памяти 12, Ф 13 пороговых уровней, управляемый делитель

„„Я0„„1501297 А 1

14 наложения, блок выборки и хранения 15, блок вычитания t 6, пороговый блок. 17, регистр 18, Ф 19 сигнала и управляемый делитель 20 частоты. На вход устр-ва поступают искаженные помехами двоичные сигналы, уровень которых в зависимости от КП канала связи изменяется. Если КП изменится, то отличие результатов сверток будет выше установленного порога и на регистр 18 поступит сигнал логической переменной "1", сдвиг в котором производит блок управления 6. На основании числа 111, записанных в регистре

18, Ф 19 определяет коэффициент деления для делителей 14 и 20. В результате, с учетом изменения КП, каждый раз Ф 13 формирует пороговые сигналы для детектора 4, который принимает решение о надежности принятия решения решающим блоком 2 по каждому эл-ту избыточного кодового слова. 1 ил.

1501297

10

Изобретение относится к технике электросвязи и может использоваться для помехоустойчивого приема дискретных сигналов.

Цель изобретения — повышение помехоустойчивости при изменении коэффициента передачи канала связи.

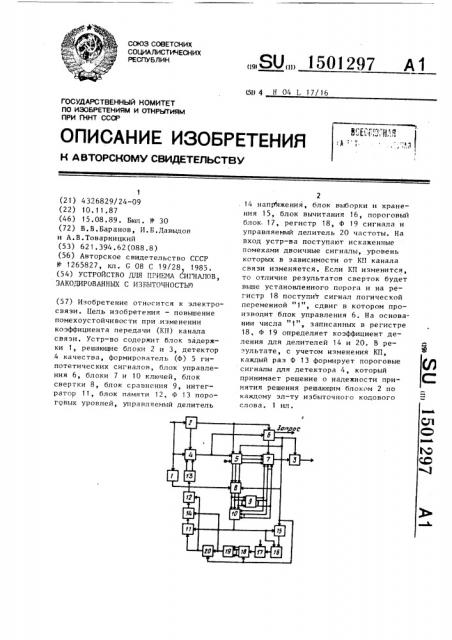

На чертеже представлена структурная электрическая схема предложенного устройства.

Устройство для приема сигналов, закодированных с избыточностью содержит блок 1 задержки, первый и второй решающие блоки 2, 3, детектор 4 качества, формирователь 5 гипотетических сигналов, блок 6 управле>1ия, первый блок 7 ключей, блок 8 1свертки, блок 9 сравнения, второй блок 10 ключей, интегратор 11, блок 12 памяти, формирователь 13 пороговых уровней, управляемый делитель 14 напряжения, блок 15 выборки и хранения, блок 16 вычитания, пороговый блок 17, регистр 18, формирователь 19 сигнала, управляемь>й делитель 20 частоты.

Устройство работает следующим образом.

На вход устройства поступают искаженные помехами двоичные сигналы, уровень которых в зависимости от коэффициента передачи канала связи изменяется. Первый решающий блок 2 принимает решение по каждому элементу с задержкой на один такт рабочей частоты дискретного канала связи и ошибается тем чаще, тем интенсивней помехи в канале связи или чем меньше его кОэффициент передачи.

Одновременно с работой> гервого решающего блока 2 детектор 4 качества принима т решение о надежности принятия р шение первым решающим блоком

2 по ка>щому элементу избыточного кодового слова °

В начальный момент времени блок 6 управления по принятой двоичной последовательности специальной конфигурации с выхода первого решающего блока 2 и сигналам детектора качества определяет границы кодовых слон (цикл), что соответствует появлению на его выходах сигналов, определяющих начало и конец обраба1ываемых слов вторым решающим .блоком 3, формирователем 5 типотетических сиги»лов, первым блоком 7 ключей и бл >ком 8 свертки. При недостаточной на15

55 де>кности принимаемого элемента пер— вым решающим блоком 2 детектор качества выдает сигнал В на вход формирователя 5 гипотетических сигналов, который фо >мирует в виде строк матрицы гипотетические последовательности следующим об>разом, если синхронно с поступлением решения об элементе ("1" или 0 ) сигнал с детектора 4 качества не поступает, то в столбце матрицы памяти формирователя 5 гипотетических сигналов записывается решение, принятое первым решающим блоком 2. Если же сигнал g поступил, элемент, поступающий с первого решающего блока 2, во внимание не принимается, и B столбце

1 матрицы записывается разное количестВо "0" H "1", в верхней половине строк матрицы "0 в tt>!>ríåé половине

>1 11

1, При по туплени;r следующего сигнала g на длине этого же кодового слова в очередном столбце матрицы заполняются в каждой из половинок строк разбитой пополам в верхней части строк "0 . a в нижней "1" и так каждый раз с приходом очередного сигнала "О" на длительности кодового слова до разрешенного числа стираний

К, связанного с минимальным кодов >м расстоянием d ;ц соотношением

K O = d m 1, определяющего разрез матрицы гипотетических последовательностей размера и х 2, с поко мощью модуляторов несущего колебания формирователь 5 приводит сформированные последовательности к виду канальных сигналов — 8 (). имеющих

° 1 место по входу устройства.

Полученн re таким образом гипотез тические сигналы S. (t) с выхода фор1 мирователя 5 гипотетических сигналов одновреме>гно с выходами сигналон

y(t) = „(t) S„ (t) + n(t) блока 1 задержки выступает на блок 8 свертки, где осуществляется их свертка в целом" rra;rarrrre кодовой комбинации. Результаты сверток поступа>от в блок 9 сравнения, где входу с максимальным результатом свертки на выходе в соответствие ставится выход. ной сигнал "1" (а все остальные

"0»), разрешающий считывание с соответствующей строки матрицы формирователя 5 последовательности во второй решающий блок 3.

Выход детектора 4 качества соединен также с выходом блока 6 управ1501297

:гения, к<)т<)рый по;<с гитывает число

cfff.IfH

ntэ

=грГ, +<< J n(t) s (с) 4<, <)с»

О где s, = j s,(t) s (t) dt.

О

Сигналы максимальных ре зультатов свертки с выхода второго блока 10 ключей пос тупают на вход инте гра тора 11, где накапливаюгся на длительности 1 кодовых слов, равной интервалу локальной стационарности каб. нала связи, на которой коэффициент

j4 (f: ) остается неизмегг нь<м. Этот интервал определяется следующим образом.

1 езультат сверток гипотетического и канального сигналов с выхода блока

8 сверток через второй блок 10 ключей поступает одновременно на один из входов блока 16 вычитания и вход блока 15 выборк<) и хранения, где хранится до поступления следующего

Результата сг)ертки гипотетического

If каг<ального сигналов. По сигналу с выхода блока 5 управления результат свертки двух сигна.гов, записанный в блоке 15 выборки и хранения, подается на второй вход блока 16 вычитания а в блок 15 занос итсн результат свертки гипоте гического и канального сигналов следующей ко;говей комбинаllHH. Таким образом на входы блока

l б вьггитапия подаюгся значения сверток, характерHsyf()f

Ес Il; коэффпцпент )<с ре

5 сигнач в виде логической переменной

"1", если не и менился или измегпглся незначительно, то О". Сдвиг регистра 18 происходит по сигналу с выхода блока 6 управления. На основании

10 числа "1", записанного в регистре

18, формирователь 19 сигнала определяет коэффициент деления, который подается на управляющие входы управляемого делителя 20 частоты и управ15 ляемого делителя 14 напряжения. Если изменения fu(1.) часты при приеме различных кодовых комбинаций, то и коэффициент д ления в управляемом делителе 20 частоты больше. Следова20 тельно, и управляющий сигнал с его выхода, xëðàêòåðèýóâùèé длительность интервала локальной стационарности канала связи, будет поступать на вход интегратора 11 и блока 12 памя25 ти чаще. Сигналы максимальных результатов свертки, накопленные в интеграторе 11, по управляющему сигналу с выхода управляемого делителя 20 записываются в блок 12 памяти, причем

3Q записывается не весь результат, а

его среднее значение на длительности одного кодового слова. Деление происходит в управляемом делителе

14 напряжения, на управляющий вход которого поступает сигнал с выхода

35 формирователя 19, который характеризует интервал локальной стационарности канала связи, т.е. число кодовых комбинаций, на длине которых

40 г(С) практически не заменяется. Среднее значение резульгатов сверток хранится в блоке 12 памяти в течение последующего интервала накоггггения в виде

45 (,1 t

)с<

s (t)dtj» << <<

Сигнал с вь<х<) fsf последнего элемента блока 12 поступает на вход формирователя 13 пороговых уровней, который кажлый paз форьп<рует пороговь<е сигналы детектору качества с учетом изменения коз<1«1)гг)«гент» передачи канала связи по энерг ет<гке накопления ,фЕс. Интервал нако)о<ения интегратора

11 и интервал храпеllif

Формул а и з о бр е те н и я

35

Составитель й. Москевич

Редактор О.Спесивых Техред JI Îëèéíûê Корректор M.Шароши

Заказ 4893/57 Тираж 626 Подписное

ВНКИПИ Государственного комитета по изобретениям и открытиям при ГКНТ СССР

113035, Москва, Ж-35, Раушская наб., д. 4/5

Произв дственно-издательский ксмбинат "Патент", r.Óæãoðîä, ул. Гагарина, 101 мяти задается сигналом переполнения управляемого делителя 14 напряжения, появляющегося после обработки каждого 1-го кодового слова.

В случае появления на длине кодового слова числа стираний более чем

N на дополнительном входе блока 6 управления появляется сигнал Запрос" для канала обратной связи.

Устройство для приема сигналов, закодированных с избыточностью, содержащее интегратор, блок задержки, последовательно соединенные первый решающий блок, блок .управления, к второму входу которого подключен выход детектора качества, первый блок ключей и второй решающий блок, второй вход которого соединен с вторым выходом блока управления, с управляющим входом формирователя гипотетических сИгналов, к первому сигнальному входу которого подключен первый выход первого решающего блока, и с управляющим входом блока свертки, к одним входам которого подключены одни выходы формирователя гипотетических сигналов, второй сигнальный вход и другие выходы которого соединены соответственно с выходом детектора качества, к первому входу которого подключен второй выход первого решающего блока, и с одними сигнальными входами первого блока ключей, другие сигнальные входы которого соединены с сигнальными входами второт о блока ключей и с выходами блока сравнения, входы которого соединены с выходами блока свертки, к другому входу которого подключен выход блока задержки, и с управляющими входами второго блока ключей, выход которого подключен к сигнальному входу интегратора, и последовательно соединенные блок памяти и формирователь пороговых уровней, выходы которого подключены к пороговым входам детектора качества, второй вход которого соединен с входом первого решающего блока, который является входом устройства, и с входом блока задержки, о т л и ч а ю щ е ес я тем, что, с целью повышения помехоустойчивости при изменении коэффициента передачи канала связи, введены последовательно соединенные формирователь сигнала и управляемый делитель частоты, выход которого подключен к управляющим входам блока памяти и интегратора, управляемый делитель напряжения и последовательно соединенные блок выборки и хранения, блок вычитания, пороговый блок и регистр, управляющий вход и выходы которого соединены соответственно с вторым выходом блока управления, который подключен к управляющему входу блока выборки и хранения, и с входами формирователя сигнала, выход которого подключен к управляющему входу управляемого делителя напряжения, сигнальный вход и выход которого соединены соответственно с выходом интегратора и с сигнальным входом блока памяти, при этом выход второго блока ключей соединен с сигнальным входом блока выборки и хранения и с вторым входом блока вычитания, а второй выход блока управления подключен к управляющему входу управляемого делителя частоты.