Устройство предсказания оценки качества канала связи

Иллюстрации

Показать всеРеферат

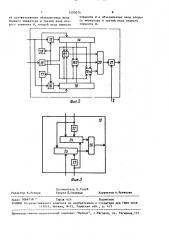

Изобретение относится к радиотехнике и позволяет сократить время предсказания оценки качества канала связи. Устройство содержит счетчик 1 ошибок, формирователь 2 циклов отсчета, элементы ИЛИ 3 и 9, регистр 4 сдвига, сумматор 5 по модулю два, элементы И 6 и 7, элемент ИЛИ-НЕ 8, блок 10 определения приращений частости ошибок и индикатор 11. Благодаря введению, в устройство элемента ИЛИ 9 и блока 10 определения обеспечивается определение тенденции к нарастанию частости ошибок. 2 з.п. ф-лы, 3 ил.

СОЮЗ СОВЕТСКИХ

СОЦИАЛИСТИЧЕСКИХ

РЕСПУБЛИК (19) (11) ОПИСАНИЕ ИЗОБРЕТЕНИЯ

К А ВТОРСКОМУ СВИДЕТЕЛЬСТВУ

ГОСУДАРСТВЕННЫЙ КОМИТЕТ

ПО ИЗОБРЕТЕНИЯМ И OTHPblTHRM

ПРИ ГКНТ СССР

1 (21) 4335061/24-09 (22) 09. 10. 87 (46) 23. 08. 89. Бюл. Р 31 (72) Ю.Н.Юркин (53) 621. 395. 664 (088 ° 8) (56) Авторское свидетельство СССР

У 1040613, кл. Н 04 В. 3/46, 1982.

Авторское свидетельство СССР

В 951742, кл. H 04 L 11/08, 1981. (54) УСТРОЙСТВО ПРЕДСКАЗАНИЯ ОЦЕНКИ

КАЧЕСТВА КАНАЛА СВЯЗИ (57) Изобретение относится к радиотехнике.и позволяет сократить время (51) 4 H 04 L 1 1 / 08/ / Н 04 В 3 / 4 6

2 предсказания оценки качества канала связи. Устройство содер)кит счетчик

1 ошибок, формирователь 2 циклов отсчета, элементы ИЛИ 3 и 9, регистр

4 сдвига, сумматор 5 по модулю два, элементы И 6 и 7, элемент ИЛИ-НЕ 8 ° блок 10 определения прирашений час-тости ошибок и индикатор 11. Благодаря введению в устройство элемента

HJIH 9 и блока 10 определения обеспечивается определение тенденции к нарастанию частости ошибок. 2 s.ï. ф-лы, 3 ил.

1 ><11(>! 4

Bol о н втс рого рязрндпн jlpãисгря сдв ига, которые также че ре.-> первый элемент И 6 подаются пя Входы flpp вого элемента ИЛИ 3 и элемента 11ЛИНЕ 8, На первый, второй и третий вхо5 ды индикатора 11 подаются соответственно сигналы с выходов первого элемента ИЛИ 3, элемента ИЛИ-HE 8 и сумматора 5 по модулю два.

По второму и третьему входам в логические элементы 19.1 — 19,п поступают сигналы на входы первого инвертора

22 и первого элемента И 24, с выходов которых сигналы подакттся на входы 15 элемента ИЛИ 26.

20

Зр импульсов, с первым Входом второго элемента И и с трегьимп входами всех с выходами первого и второго элементов И и первым входом индикатора, второй вход которого соединен с flffходом сумматора по модулю два, э.7е—

35 мент ИЛИ-HE первый и второй входы и выход которого соединены соответственно с выходами сумматора по модулю два и первого элемента И и с третьим входом индикатора, вьгход вто- 4р рого разряда регистра сдвига подключен к второму входу первого элемента

И, последовательно соединенные формирователь циклов отсчета и счетчик

ОшибОК HTQpOH ВХОД КОтОрОГО яВЛЯет 45 ся входом устройства, о т 7 и ч а ю— щ е е с я тем, что, с целью сокращения времени предсказания оценки качества канала связи за счет определения тенденции к нарястянию частости ошибок, введены второй элемент

ИЛИ, первый и Второй входы и Выход которого соединены соответственно с первым и вторым выходами счетчика ошибок и входом регистра сдвига блок

1 55 определения прирякге н ий часто сти ош ибок, первый„ второй и третий Входы которого соединень; соответственно с выходом формировятеля циклов отФормула изобретения

1. Устройство предсказания оценки качества канала связи, содержащее регистр сдвига, сумматор по модулю два, первый и второй входы которого соединены соответственно с выходами первого и второго разрядов регистра сдвига, первый и второй элементы И, первые входы которых соединены с выходом первого разряда регистра сдвига, индикатор, первый элемент

ИЛИ, первый и второй входы и выход которого соединены соответственно гнетя, Выходом первого разряда регистра сдвига и вторым Входом счетчика ошибок, а выход блока определенияя приращений часто сти ошибок подключен к второму входу второго элемента И.

2. Устройство по п. 1, о т л и— ч а ю щ е е с я тем, что блок oflределения приращений частости ошибок содержит триггер,два формирователя импульсов, три элемента И, элемент ИЛИ, два регистра сдвига и и логических элементов, выходы которых соединены с соответствующими вхоДами элемента Иг1И, выход которого подключен к первому входу третьего элемента

И, первый выход триггера соединен с входом первого формирователя импульсов, первым входом первого элемента

И и первыми входами всех и логических элеме нтов, в торые входы которых с соответствующими выходами первого регистра сдвига, вход и вход "Сброс" которого соединены соответственно с выходом первого элемента И и с выходом первого формирователя им- . пульсов, второй выход триггера соединен с входом Второго формирователя и логических элементов, четвертъге входы которых соединены с соответствующими выходами второго регистра сдвига, вход и Вход Сброс" которого соединены соответственно с выходом второго элемента И и с выходом второго формирователя импульсов, вход триггера является первым входом блока определения прпрящений частости ошибок, вторым и третьим входами и выходом которого являются соответственно второй вход третьего элемента И, объединенные вторые входы первого и второго элементов И и выход третьего элемента И.

3. Устройство по п.2, о т л и ч а ю щ е е с я тем, что логический элемент содержит лва инвертора, элемент ИЛИ и двя элемента И, первые входы и выходы которых соединены соответственно с выходами первого и второго инверторов и с Входямп элемента ИЛИ,выход которого является выходом логнческого элемента, первым входом которого является второй Вход Второго элемента И, а вторым, третьим и четвертым входами ло гиче ско го э темента яв:тяют1503074

Фиа У

Составитель E. Голуб

Техред Л,Олийнык Корректор О. Кравцова

Редактор Н. Тупица

Заказ 5086 /58 Тирах 626 Подписное

ВЧИИПИ Государственного комитета по изобретениям и открытиям при ГКНТ СССР

113035, Москва, Ж-35, Рауйская наб., д. 4/5

Производственно-нэцательский комбинат "Патент", г.ужгород, ул. Гагарина,101 ся соответственно объединенные вход первого инвертора и третий вход второго элемента И, второй вход первого

I элемента И и объединенные вход второго инвертора и третий вход первого элемента И.