Устройство для организации очереди

Иллюстрации

Показать всеРеферат

Изобретение относится к области автоматики и вычислительной техники и может быть использовано в устройствах управления очередностью обслуживания. Целью изобретения является повышение достоверности работы устройства за счет исключения потери запросов с длительностью, меньшей длительности цикла чтения устройства. Устройство для организации очереди содержит два регистра хранения информации и сдвиговый регистр, две группы элементов И, группу элементов задержки, распределитель импульсов, триггер, элемент ИЛИ, формирователь импульсов, счетчик и коммутатор. В устройстве благодаря использованию сдвигового регистра для управления коммутатором осуществляется выдача на выходы устройства требуемого кода приоритета со счетчика, а применение группы элементов задержки и соединение синхровходов триггеров с входами устройства позволяет обрабатывать запросы любой длительности, причем исключено срабатывание устройства от кратковременных единичных помех. 1 ил.

СОЮЗ СОВЕТСКИХ

СОЦИАЛИСТИЧЕСКИХ

РЕСПУБЛИК

„„SU,» 150465 (51) 4 G 06 F 9/46

ОПИСАНИЕ ИЗОБРЕТЕНИЯ!

КЕОЮ оИ0 . :- i :л 1403

E.ь ь ." .. л <

"I Ъ| iI Ml (,. ° ".

ГОСУДАРСТВЕННЫЙ КОМИТЕТ

IlO ИЗОБРЕТЕНИЯМ И ОТКРЫТИЯМ

ПРИ 1КНТ ССОР

К АВТОРСКОМУ СВИДЕТЕЛЬСТВУ

1 (21) 4364328/2.4-24 (22) 18.01.88 (46) 30.08,89. Бюл. У 32 (72) А.Н. Бучнев; В.P. .Горовой, Е,И, Карпунин, В.А. Корнеев и В.И. Песоченко (53) 681.325(088.8). (56) Авторское свидетельство СССР

Р 851409, кл. G 06 F 9/46, 1979, Авторское свидетельство СССР

В 1128255, кл. G 06 F 9 /46, 1983. (54) УСТР011СТВО ДЛЯ ОР ГАНИЗАЦИИ

ОЧЕРЕДИ (57) Изобретение относится к автоматике и вычислительной технике и может быть использовано в устройствах управления очередностью обслуживания,.

Целью изобретения является повышение достоверности работы устройства за счет исключения потери запросов

Изобретение относится к автоматике и вычислительной технике и может быть использовано в устройствах удравления очередностью обслуживания.

Цель изобретения - повышение достоверности работы устройства за счет исключения потери запросов с длительностью, меньшей длительности цикла чтения устройства.

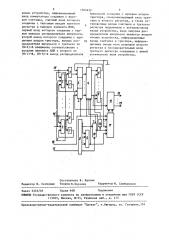

На чертеже представлена схема устройства.

Устройство содержит первый регистр 1,с триггерами 2, второй и треТий регистры 3 и 4, первую группу элементов И 5, вторую группу элементов И 6, элементы задержки 7, распре2 с длительностью, меньшей длительности цикла чтения устройства. Устройство для органиэации очереди содержит два регистра хранения информации и сдвиговый регистр, две группы элементов И, группу элементов задержки, распределитель импульсов, триггер, элемент ИЛИ, формирователь импульсов, счетчик и коммутатор. В устройстве благодаря использованию сдвигового регистра для управления коммутатором осуществляется выдача на выходы устройства требуемого кода приоритета со счетчика, а применение группы элементов задержки и соединение синхровходов триггеров с входами устройства позволяет обрабатывать запросы любой длительности, причем исключено срабатывание устройства от кратковременных единичных помех..

1 ил. делитель импульсов 8, элемент ИПИ 9, Ф триггер 10, счетчик 11, коммутатор

12, формирователь импульсов 13, группу запросных входов 14 устройства, группу информационных выходов

15 устройства, установочный вход 16 устройства и вход 17 чтения устройства, Устройство работает следующим образом.

В исходном состоянии регистры 3 и

4, триггер 10 и счетчик .11 обнулены, Обнуление производится единичным импульсом о входу 16 устройства, Разряды регистра 1 обнуляются автоматически через элементы задержки 7, За3 .150465 просы на обслуживание поступают по входам 14 устройства, фиксируются в триггерах 2 регистра 1 и через элементы И 5 устанавливают в единицу

5 соответствующие разряды регистра 3.

Приоритет запросов возрастает с возрастанием порядкового номера запроса. Элементы И 5 предотвращают срабатывание регистра 3 при появлении на входах 14 кратковременной единичной помехи ° Помехой считается сигнал, длительность Которого меньше времени срабатывания триггера 2. Помеха установит в единицу один из триггеров (5

2, но через время, определяющееся величиной элемента задержки, триггер 2 возвратится в исходное состояние.

Так как триггер 10 обнулен, то регистр 4 и счетчик ll находятся в ре- 20 жиме ожидания параллельного приема информации, заданном единицей с инверсного выхода триггера 10. По тактовому входу 17 устройства поступают импульсы чтения. Рассмотрим один такт чтения устройства. По переднему фронту импульса чтения запускается распределитель импульсов 8. Импульс с его первого выхода через элемент

ИЛИ 9 поступает на тактовые входы 30 регистра 4 и счетчика 11. По переднему фронту этого импульса содержимое регистра 3 переписывается в регистр 4, а в счетчик 11 заносится нулевое значение. Если в регистр 4 записался запрос наивысшего приоритета, то единица с N-го выхода регистра 4 открывает коммутатор 12 и на выходы 15 устройства из счетчика 11 выдается код наивысшего приоритета. . 40

Затем импульсом со второго выхода распределителя импульсов 8 устанавливается в единицу триггер 10, сигнал с инверсного выхода которого переводит регистр 4 в режим сдвига инфор-41 мации, а счетчик 11 — в режим счета.

Кроме того, формирователь 13 выраба-.. тывает единичный импульс, который проходит через элементы И 6 и сбрасывает только те разряды регистра 3, из которых в регистр 4 переписалась единица, Следующие N импульсов, поступающие через элемент ИЛИ 9 с вы,.ходов распределителя импульсов 8, последовательно сдвигают информаций в регистре 4 и прибавляют единицу, к содержимому счетчика 11. Если в

i-м разряде регистра 4 была единица, то на выходы 15 устройства из счетчи2

4 ка 11 через коммутатор 12 будет выдан код i-го запроса. Регистр 4 после окончания каждого цикла чтения будет обнулен. (N+3)-м импульсом с выхода распределителя импульсов 8 триггер 10 устанавливается в нуль.

Следующие циклы чтения происходят аналогично, Формула и з о б р е т е н и я

Устройство для организации очереди, содержащее первый регистр, первую группу из N элементов И (где

N — - число запросных входов устройства, первый элемент задержки, распределитель импульсов, элемент ИЛИ и счетчик, причем первый вход каждого

i-го элемента И первой группы (i=

=1,N) соединен с i-м запросным входом устройства, второй вход 1-го элемента И первой группы соединен с выходом i-го разряда первого регистра, о т л и ч а ю щ е е с я тем, что, с целью повьппения достоверности работы устройства за счет исключения потери запросов с длительностью, меньшей длительности цикла чтения.устройства, в него введены N-1 элементов задержки, второй и третий регистры, вторая группа из И элементов И, триггер,.формирователь импульсов и коммутатор, причем i-й синхронизирующий вход первого регистра соединен с i-м запросным входом устройства, i-й информационный вход первого регистра соединен с ыиной питания устройства, i-й нулевой вход через i-й элемент задержки подключен к выходу

i-го разряда первого регистра, выход

i-го элемента И первой группы соединен с единичным входом i-го разряда второго регистра, нулевой вход i-го разряда которого соединен с выходом

i-го элемента И второй группы, выход

i-ro разряда второго регистра соединен с i-м информационным входом третьего регистра, выход i-го разряда которого соединен с первым входом

i-го элемента И второй группы, выход

Й-ro разряда третьего регистра соединен с управляющим входом коммутатора, вторые входы всех элементов И второй группы объединены и соединены с выходом формирователя импульсов, вход которого соединен с инверсным выходом триггера и входами управления записью третьего регистра и счетчика, выход коммутатора является вы15046

Составитель В. Красюк

Техред M. Ходанич

Редактор И. Сегляник

Корректор М. Самборская

Заказ 5253/49 Тираж 668 Подписное

ВЯИИПИ Государственного комитета по изобретениям и открытиям при ГКНТ СССР

113035, Москва, Ж-35, Раушская наб., д. 4/5

Производственно-издательский комбинат "Патент", г.ужгород, ул. Гагарина,101 ходом устройства, информационный вход коммутатора соединен с выходом счетчика, счетный вход которого соединен с тактовым входом третьего

5 регистра и выходом элемента ИЛИ, первый вход которого соединен с первым выходом распределителя импульсов, второй выход которого соединен с единичным входом триггера, выхода ðàñ- 10 пределителя импульсов с третьего по (N+2)-й соединены соответственно с входами элемента ИЛИ с второго по (N+ 1)-й (0+3)-й выход распределителя

52 6 импульсов соединен с нулевым входом триггера, синхронизирующий вход триггера и второго регистра, а также установочные входы счетчика и третьего регистра подключены к установочному входу устройства, вход запуска распределителя импульсов является входом чтения устройства, информационные входы счетчика и триггера, информационные входы всех разрядов второго регистра и последовательный вход третьего регистра соединены с шиной

-логического нуля устройства,