Блок памяти для трансформаторного пзу

Иллюстрации

Показать всеРеферат

Изобретение относится к вычислительной технике и автоматике и предназначено для использования в устройствах и системах, где требуется постоянное запоминающее устройство. Цель изобретения - расширение функциональных возможностей устройства за счет осуществления считывания в параллельном и последовательном кодах. Поставленная цель достигается за счет введения схем 5 сравнения, источника 6 опорного напряжения, дифференцирующих цепочек 7, элемента ИЛИ 8. 3 ил.

СОЮЗ СОВЕТСНИХ

СОЦИАЛИСТИЧЕСКИХ

РЕСПУБЛИК

ОПИСАНИЕ ИЗОБРЕТЕНИЯ

К А ВТОРСКОМ,Ф СВИДЕТЕЛЬСТВУ

ГОСУДАРСТВЕННЫЙ КОМИТЕТ

ПО ИЗОБРЕТЕНИЯМ И ОТКРЫТИЯМ

ПРИ ГКНТ СССР (21) 4258178/24-24 (22) 08. 06. 87 (46) 07.09. 89. Бюп. и 33 (71) Куйбышевский политехнический институт им. В. В. Куйбышева (72) Ф.М. Медников, А.В. Малинин, И.Д. Лапидус и М.Л. Нечаевский (53) 681. 327. 66 (088. 8) (56) Авторское свидетельство СССР

Н 469141, кл. G 11 С 17/00, 1974.

Шигин А.Г., Дерюгин А.А. Цифровые вычислительные машины. — М.:

Энергия, 1976, с. 280, рис. 10 13, „,SU„„ 1484 А! (1) С 11 С 17/00

2 (54) БЛОК ПАМЯТИ ДЛЯ ТРАНСФОРМАТОРНОГО ПЗУ (57) Изобретение относится к вычислительной технике и автоматике и предназначено для использования в устройствах и системах, где требуется постоянное запоминающее устройство.

Цель изобретения - расширение функциональных возможностей устройства за счет осуществления считывания в параллельном и последовательном кодах. Поставленная цель достигается за счет введения схем 5 сравнения, источника 6 опорного напряжения, дифференцирующих цепочек 7, элемента

ИПИ 8. 3 ил.

3 1506484 4

Изобретение относится к вычисли- Rö тельной технике и автоматике и предназначено для использования в устройg ствах и системах, где требуется постоянное запоминающее устройство.

Цель изобретения — рас ширение функциональных возможностей за счет осуществления считывания н параллельном и последовательном кодах.

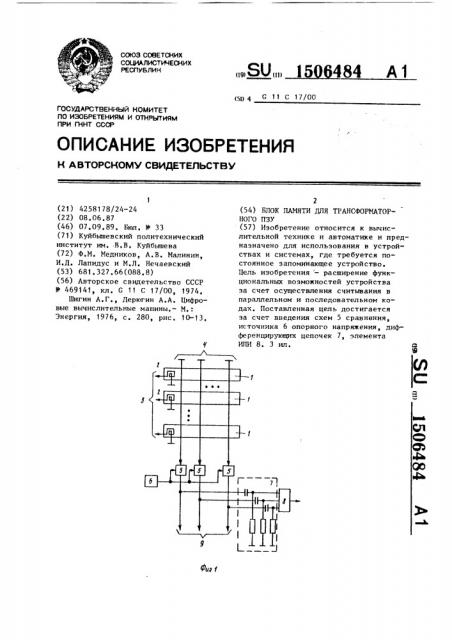

На фиг. 1 представлена схема предлагаемого блока памяти; на фиг. 2 — распределение магнитного мет нид. потока в магнитной линии; на фиг.3 временные диаграммы работы блока. 15

Блок памяти содержит П-образные согласованные магнитные линии 1 с обмотками 2 возбуждения, подключенными к адресным шинам 3, шины 4 считывания, схемы 5 сравнения, источиик

6 опорного напряжения, дифференцирующий блок 7, выполненный иа дифференцирующих цепочках, элемент ИЛИ 8, выходные разрядные шины 9.

П вЂ образн магнитная линия выполняется из электротехнической стали

Э350 при реализации блока используются интегральные компараторы

521 A3, на которых ныпслняются сравнивающие устройства, схема ИЛИ— микросхема ерии К500ЛМ109. Обмотки возбуждь.ния выполняются в виде плоских контурон, оптимальное число котс— рых должно состанлять порядка 10. ,Разрядные шины для параллельного счи- 35 Этот поток индуцирует в

T тынания информации соединены непосред- тывания напряжения стненно с выходами схем сравнения (интегральньгс компараторов). а шина последовательн .I о вывода информации подключена к вьгходу элемента ИЛИ. Шины 4 считывания при записи единицы

P. прошивают магнитные линии 1, а при записи нуля их огибают.

Блок памяти работает следующим образом.

При нь боре одной из адресных шин

3 на обмотку 2 возбуждения соответствующей магнитной линии 1 подается импульс напряжения, в результате чего в ней возникает магнитный поток, определяемьп из соотношения

+ х

g(X) = Ае + Be (1) магнитное сопротивление; проводимость рассеяния между сердечниками линии.

У(Х) = Р, (2) (л

1 )ма с (1 — е ), (3) шинах 4 счи40 где Х вЂ” координата i-й ! вания. шины считыс", = с, (1п — — Х, ) = Ь П„

55 (6) где координата Х отсчитывается от обмотки возбуждения (фиг. 2); — -„t gR — постоянная распространения магнитной линии

Для согласования магнитной линии (нагруженной на волновое сопротивле10 RI4 ние R> = - — ) соотношение (1) при g где 1 — значение потока при Х = 0 ° о

При скачкообразном подключении обмотки 2 возбуждения к источнику питания поток в обмотке возбуждения нарастает по закону где с = L/R — постоянная времени обЬ мотки возбуждения.

Таким образом, изменение магнитного потока по длине линии и во времени описывается в силу (2) и (3) выражением

КХ 1/сЪ

7(X1) = х „° е (1 — е ) (4) йФ(Х t) - » - ь и, = -ь, ---- .--= -11@ /q e e щ„„, 1г иа»с Ъ .. » (5) Напряжения U»,», ñ вьмодов шин 4 считывания подаются на иннертирующие

45 входы схем 5 сравнения, на неинвертирующий вход которых подается постоянное опорное напряжение П

При достижении равенства Пьь,„ (фиг, 3) на выходе схем 5 формируются импульсы напряжения (фиг.3б, в, r) длительность которых определяется из соотношения

Из (6) следует, что длительность импульсов, формируемых на выходе схем 5, линейно связана с коорлинатой Х.

5 15

Отрицательный перепад напряжения с выходов схем 5 используется для считывания инАормации, записанной в блоке памяти, в параллельном коде через выходные разрядные шины 9.

Импульсы с выходов схем 5 дифференцируются с помощью дифференцирующих цепочек блока 7, причем импульсы положительной полярности, возникающие эа счет дифференцирования задних фронтов сигналов с выходов схем 5, воздействуют на входы элемента ИЛИ.

На ее выходе при этом образуется последовательность импульсов (фиг.Зд) причем наличие импульса в определенный момент времени (относительно отрицательного перепада напряжения с выходов сравнивающих схем 5) характеризует считывание единицы из соответствующего разряда выбранного слова, а его отсутствие — считывание нуля, Таким образом, предлагаемый блок памяти обладает более широкими функциональными возможностями, так как обеспечивает возможность считывания информации как в параллельном, так и в последовательном коде.

Обмотки возбуждения и шины считывания могут выполняться печатным методом, а магнитные линии — методом напыления магнитных пленок на непроводящую основу. Это позволяет изготавливать блок памяти по интегральной технологии на одной подложке с электронными элементами, обеспечивающими функционирование ПЗУ (сравнива;ющие устройства, диффренцирующие цепочки, схема ИПИ).

Согласование магнитной линии осуществляется с помощью ферромагнитного якоря, расположенного в торце магнит06484 6 ной линии. В этом случае, как следует из соотношения (6), обеспечивается линейная связь между длительностями формируемых временных интервалов и координатой шин считывания относительно обмотки возбуждения. Это существенно облегчает синхронизацию приема информации с ПЗУ в последовательip ном коде.

Формул а изобретения

Блок памяти для трансформаторного ,15 ПЗУ, содержащий накопитель на сердечниках из магнитного материала с непрямоугольной петлей гистерезиса, адресные и разрядные шины, о т л ичающий с я тем, что, с целью

20 расширения функциональных возможностей за счет осуществления считывания в параллельном и последовательном кодах, он содержит схемы сравнения, источник опорного напряжения, диф25 ференцирующие цепочки, элемент ИЛИ, выход которого является выходом последовательного вывода информации блока памяти, входы элемента ИПИ соединены с выходами дифференцирующего

30 блока, входы которого подключены к выходам соответствующих схем сравнения, первые входы которых подключены к источнику опорного напряжения, а вторые входы схем сравнения подключены к шинам считывания накопителя, причем сердечники накопителя выполнены в виде П-образных согласованных магнитных линЫт, по торцам которых расположены обмотки возбуждения, под40 ключенные к адресным шинам накопителя, выходы схем сравнения являются выходами параллельного вывода информации блока памяти.

1506484

Составитель Л. Амусьева

Редактор Н. Тупица Техред A.Êðàâ÷óê Корректор О. Кравцова

Заказ 5443/52 Тираж 558 Подписное

ВНИИПИ Государственного комитета по изобретениям и открытиям при ГКНТ СССР

113035, Москва, Ж-35, Раушская наб., д. 4/5

Производственно-издательский комбинат Патент", г. Умг род, ул. Гагарина, 1П!