Умножитель частоты

Иллюстрации

Показать всеРеферат

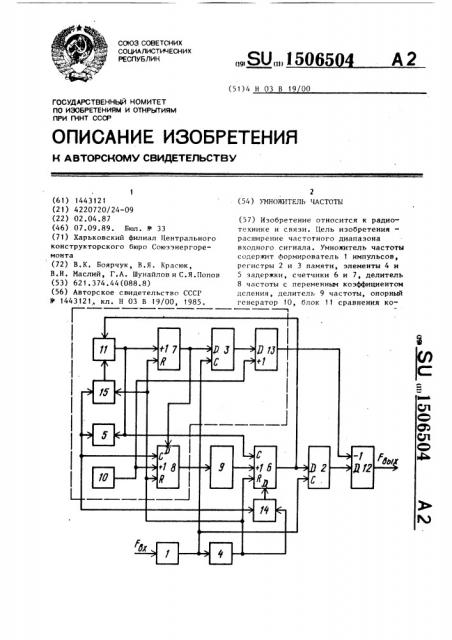

Изобретение относится к радиотехнике и связи. Цель изобретения - расширение частотного диапазона входного сигнала. Умножитель частоты содержит формирователь 1 импульсов, регистры 2 и 3 памяти, элементы 4 и 5 задержки, счетчики 6 и 7, делитель 8 частоты с переменным коэффициентом деления, делитель 9 частоты, опорный генератор 10, блок 11 сравнения кодов, управляемые делители 12 и 13 частоты и блоки задания кодов (БЗК) 14 и 15. Введение БЗК 14 и 15 позволяет реализовать высокие коэффициенты деления управляемых делителей 12 и 13 без снижения быстродействия. Это приводит к расширению диапазона частот входного сигнала. 1 ил.

СОЮЗ СОВЕТСНИХ

СОЦИАЛИСТИЧЕСКИХ

РЕСПУБЛИК

А2

„„$0„„15065 (51)4 Н 03 В 19 00

ОПИСАНИЕ ИЗОБРЕТЕНИЯ

2 (54) Умножиткль члстоты

Яч

CO

Cb

СЛ

CO кф

ГОСУДАРСТВЕННЬЙ КОМИТЕТ

ПО ИЗОБРЕТЕНИЯМ И ОТКРЫТИЯМ

ПРИ ГКНТ СССР

К А BTOPCHOMY СВИДЕТЕЛЬСТВУ

1 (61) 1443121 (21) 4220720/24-09 (22) 02.04.87 (46) 07.09.89. Бюл. У 33 (71) Харьковский филиал Центрального конструкторского бюро Союззнергоремонта (72) В.К. Боярчук, В.Я. Красюк, В.Н. Маслий, Г.А. Шунайлов и С.Я.Попов (53) 621.374.44(088.8) (56) Авторское свидетельство СССР

11 1443121, кл. Н 03 В 19/00, 1985. (57) Изобретение относится к радиотехнике и связи. Цель изобретения— расширение частотного диапазона входного сигнала. Умножитель частоты содержит формирователь 1 импульсов, регистры 2 и 3 памяти, элементы 4 и

5 задержки, счетчики 6 и 7, делитель

8 частоты с переменным коэффициентом деления, делитель 9 частоты, опорный генератор 10, блок 11 сравнения ко3 1506504 4 дов, управляемые делители 12 и 13 деления управляемых делителей 12 и 13 частоты и блоки задания кодов (БЗК) беэ снижения быстродействия. Это при14 и 15. Введение БЗК 14 и 15 лозво- водит к расширению диапазона частот ляет реализовать высокие коэффициенты входного сигнала. 1 ил.

Изобретение относится к радиотехнике и связи, может использоваться 10 в измерительной технике и является усовершенствованием умножителя частоты по авт.св. !! 1443121.

For

К!Кт где K — коэффициент деления делителя 9;

F " частота следования импульсов на выходе опорного генератора 10. Импульс с опорного генератора 10 поступает на счетный вход первого счетчика 6. Начальное значение кода на выходе первого блока 14 задания кодов N „ = 2" — 1. Начальное значение кода на выходе второго блока 15

55 Цель изобретения - расширение час- !5 тотного диапазона входного сигнала.

На чертеже представлена структурная электрическая схема умножителя частоты.

Умножитель частоты содержит форми- 2р рователь 1 импульсов, первый 2 и второй 3 регистры памяти, первый 4 и второй 5 элементы задержки, первый 6 и второй 7 счетчики, делитель 8 частоты с переменным коэффициентом деле- 25 ния, делитель 9 частоты, опорный генератор 10, блок 11 сравнения кодов, первый 12 и второй 13 управляемые делители частоты, первый блок 14 задания кодов и второй блок 15 задания 3р кодов.

Умножитель частоты работает следующим образом.

В начале каждого периода входного сигнала формирователь формирует ко роткий импульс, который поступает на входы записи первого 2 и второго 3 регистров и на вход первого элемента

4. Задержанный импульс поступает на вход начальной установки первого 6 и 40 ,второго 7 счетчиков и первого 14 и второго 15 блоков задания кодов и де-лителя 8, коэффициент деления которого К1 устанавливается равным единице.

Периодическая последовательность импульсов может быть с частотой задания кодов N > 2" — 2, В момент совпадения текущего значения двоичного кода на выходе первого счетчика

6 с двоичным кодом на выходе второго блока 15 задания кодов на выходе блока 11 формируется импульс, который поступает на установочный вход первого счетчика 6, на счетный вход второго счетчика 7 и на счетные входы первого 14 и второго 15 блоков задания кодов. При этом первый счетчик 6 устанавливается в состояние N

1о значение двоичного кода на выходе второго счетчика 7 удваивается (начальное состояние второго счетчика 7 соответствует единице), на выходе первого 14 и второго 15 блоков задания кодов устанавлираются значения

P соответственно й, 2 " — 1 N 2 -2, где р — количество импульсов с выхода блока 11 за период измерения.

Сформированный на выходе блока 11 импульс через второй элемент 5 поступает на вход записи делителя 8, коэффициент деления которого К1,увеличивается в два раза. Таким образом, коэффициент деления делителя 8 и значение двоичного кода на выходе второго счетчика 7 совпадают, а количество импульсов на выходе опорного гегератора 10 эа один период входного сигнала К К К К, где К з - значе" ние двоичного кода на выходе первого счетчика 6. !

С приходом очередного импульса с выхода формИрователя 1 текущие значения Е и К двоичных кодов с выходов первого 6 и второго 7 счетчиков переписываются соответственно в первый 2 и второй 3 регистр1ы, а первый

6 и второй 7 счетчики, первый 14 и второй 15 блоки задания кодов и делитель 8 устанавливаются в начальное состояние, с которого начинается измерение очередного периода входного сигнала. Коэффициент деления первого управляемого делителя 12 принимает значение К>, а коэффициент деления второго управляемого делителя 13 "

К,. Частота сигнала на выходе икно5

1506504

6 жителя частоты может быть представ- вия, что приводит к расширению диапалена в виде Р зона частот входного сигнала. лена в виде Р„=, частота входЬйх КК

For ного сигнала F „", тогда изобретения

Формула

Указанная особенность позволяет реализовать высокие коэффициенты деления первого и второго управляемых делителей без снижения быстродейст20

Составитель Ю. Максимов

Техред М. Дидык Корректор М.Шароши

Редактор Н. Тупица

Заказ 5444/53 Тираж 884 Подписное

ВНИИПИ Государственного комитета по изобретениям и открытиям при ГКНТ СССР

113035, Москва, Ж-35, Раушская наб., д. 4/5

Производственно-издательский комбинат "Патент", г.ужгород, ул. Гагарина, 101

РвсК

ы(К К Вх 2

1 S

Коэффициент деления второго управляемого делителя 13 принимает значения К, * 1,2,4,...,2, а максималь-10 ный коэффициент деления первого управляемого делителя 12 К z = 2" -1, тогда

Умножитель частоты по авт.св.

Н - 1443121, отличающийся тем, что, с целью расширения частотного диапазона входного сигнала,введены первый и второй блоки задания кодов, первые входы которых соединены с выходом первого элемента задержки, а вторые входы первого и второго блоков задания кодов соединены с выходом второго элемента задержки,выход первого блока задания кодов соединен с информационным входом первого счетчика, выход второго блока задания кодов соединен с вторым входом блока сравнения кодов.