Устройство для коррекции шкалы времени

Иллюстрации

Показать всеРеферат

Изобретение относится к радиотехнике и приборостроению. Цель изобретения - повышение точности коррекции. Для достижения цели в устройство введены Д-триггер, два дополнительных RST-триггера 15, 17, формирователь 16 одиночных импульсов, генератор 18 пачки импульсов, два элемента ИЛИ 19, 20, элемент ИЛИ-НЕ 21 и мультиплексор 22. В результате единого цикла коррекции, т.е. при однократной коррекции, состоящей из грубой и точной частей, шкала времени, формируемая делителем 3, сдвигается на величину ΔТ=±(N<SB POS="POST">1</SB>K<SB POS="POST">1</SB> + N<SB POS="POST">2</SB>T), ГДЕ N<SB POS="POST">1</SB> И N<SB POS="POST">2</SB> - ВЕЛИЧИНЫ ГРУБОЙ И ТОЧНОЙ КОРРЕКЦИИ СООТВЕТСТВЕННО, K<SB POS="POST">1</SB> - КОЭФ.ДЕЛЕНИЯ ДЕЛИТЕЛЯ 3 ОТ ВХОДА ДО ВЫХОДА, СОЕДИНЕННОГО СО ВТОРЫМ ВХОДОМ МУЛЬТИПЛЕКСОРА 22, Т-ПЕРИОД ПОВТОРЕНИЯ ИМПУЛЬСОВ Г-РА 1, ОБЕСПЕЧИВАЯ ТЕМ САМЫМ В УСЛОВИЯХ РАСШИРЕНИЯ ДИАПАЗОНА КОРРЕКЦИИ СОХРАНЕНИЕ ВЫСОКОЙ ТОЧНОСТИ. 5 ИЛ.

СОЮЗ СОВЕТСНИХ

СОЦИАЛИСТИЧЕСНИХ

РЕСПУБЛИК

А1 (19) (11) (51)4" 04 1. 7 02 С 04 С 11 02

ОПИСАНИЕ ИЗОБРЕТЕНИЯ

К А ВТОРСНОМУ СВИДЕТЕЛЬСТВУ

ГОСУДАРСТВЕННЫЙ НОМИТЕТ

ПО ИЗОБРЕТЕНИЯМ И ОТНРЫТИЯМ

ПРИ fHHT СССР

1 (21) 4336904/24-09 (22) 30.11.87 (46) 07,09,89, Бюл, У 33 (72) А.Н.Судаков и А.E.Òþëÿêîâ (53) 621.394.662 (088.8) (56) Авторское свидетельство СССР

Ф 1095431, кл. Н 04 L 7/02, G 04 С 11/02, 1984.

Авторское свидетельство СССР

9 1247828, кл. Н 04 L 7/02, G 04 С 11/02, 1986.

Авторское свидетельство СССР

11- 1277413, кл, Н 04 L, 7/02, G 04 С 11/02, 1 986. (54) УСТРОЙСТВО ДЛЯ КОРРЕКЦИИ ШКАЛЫ

ВРЕМЕНИ (57) Изобретение относится к радиотехнике и приборостроению. Цель изобретения — повьппение точности коррек2 ции. Для достижения цели в устр во введены D-триггер, два дополнительных

RST-триггера 15 и 17, формирователь

16 одиночных импульсов, г-р 18 пачки импульсов, два элемента ИЛИ 19 и 20, элемент ИЛИ-HF. 21 и мультиплексор 22, В результате единого цикла коррекции, т.е. при однократной коррекции, состоящей из грубой и точной частей, шкала времени, формируемая делителем

3, сдвигается на величину Дй -(И,К,4.

+N )T, где N4 и N - величины грубой и точной коррекции соответственно, К, — коэф. деления делителя 3 от входа до выхода, соединенного с вторым входом мультиплексора 22, T - период повторения импульсов г-ра 1, обеспе- Э чивая тем самым в условиях расширения диапазона коррекции сохранение высокой точности. 5 ил, C:

3 150657

Изобретение относится к радиотехнике и приборостроению и может быть использовано в синхрониэирующих системах для коррекции шкалы времени.

Цель изобретения — повышение точ5 ности коррекции.

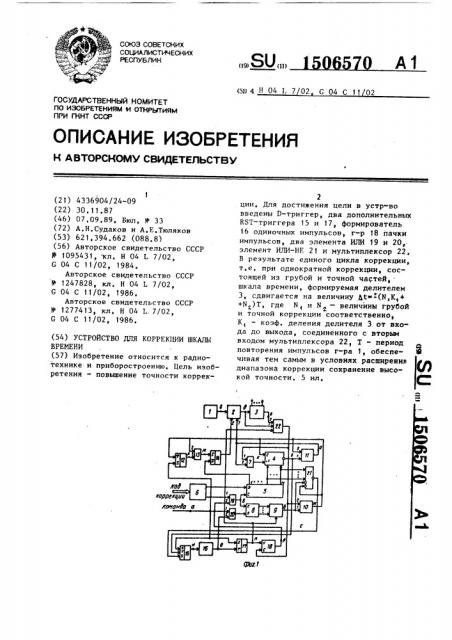

На фиг. 1 представлена структурная схема устройства для коррекции шкалы времени; на фиг,2 — схема дешифратора; на фиг.3,1,3,2 и 4 — временные диаграммы, поясняющие работу устройства, Устройство для коррекции шкалы времени содержит генератор 1, фаэосдвигающий блок 2, делитель 3 часто- ты, реверсивный счетчик 4, регистр 5 сдвига, преобразователь 6 кода коррекции, первый элемент И 7, счетчик

8, дешифратор 9, первый формирователь

10 одиночных импульсов, формирователь

11 сигнала управления, RST-триггер

12, второй элемент И 13, D-триггер

14, первый дополнительный RST-триггер

15, второй формирователь 16 одиночных импульсов, второй дополнительный

RST-триггер 17, генератор 18 пачки импульсов, первый 19 и второй 20 элементы ИЛИ, элемент ИЛИ-НЕ 21, мультиплексор 22.

Дешифратор 9 (фиг,2) содержит первый 23, второй 24 и третий 25 элементы И, инвертор 26 и элемент ИЛИ 27.

Устройство для коррекции шкалы времени работает следующим образом.

Генератор 1 является источником 35 импульсов с периодом повторения T (фиг.3.1г, 3.2г, 4г) для запуска фаэосдвигающего блока 2, который представляет собой делитель частоты с переменным коэффициентом деления, В 40 исходном состоянии коэффициент деления равен К (например K=5), что определяется наличием на первом управляющем входе фаэосдвигающего блока 2 уровня логического "0" (фиг,3.1и), 45

С выхода фаэосдвигающего блока 2 импульсы с периодом построения КТ (фиг.3.1д, 4д) поступают на счетный вход делителя 3 частоты.

Делитель 3 частоты проводит дальнейшее деление частоты импульсов с выхода фазосдвигающего блока 2 и счет времени (секунд, минут, часов).

Таким образом, делитель 3 осуществляет формирование и хранение шкалы вре- 55 мени, С одного из выходов делителя 3 импульсы .с периодом повторения К К,T (фиг.3. 1е„ 3.2е и 4е), определяющие масштаб грубой коррекции, подаются

0 4 на второй информационный вход мультиплексора 22, на первый информационный вход которого подаются импульсы с выхода фаэосдвигающего блока 2, определяющие масштаб точной коррекции.

В процессе работы устройства иэ-эа отличия частоты генератЬра 1 от номинального значения .(например, в результате "старения" кварцевого резонатора) происходит смещение хранимой шкалы времени относительно шкалы времени эталонных частот. Это требует проведения коррекции. Необходимость коррекцйи возникает также при первоначальном включении устройства, а- также при сбоях делителя 3 частоты.

Для коррекции шкалы времени на командную шину устройства подается импульс (фиг.3. 1а, 3.2а), который устанавливает триггер 12 в единичное состояние (фиг,3.1л), сбрасывает RSTтриггеры 15 и 17 (фиг,3. 1н п) и, пройдя через элемент ИЛИ 20, сбрасывает счетчик 8. При этом на выходе дешифратора 9 появляется логический

"0" (фиг.3, 1б). Логический "0" с выхода RST-триггера 17 подается на управляющий вход мультиплексора 22, при этом на выходе мультиплексора 22 проходят импульсы с выхода делителя

3 с периодом повторения КК,Т. Логический "0" с выхода RST-триггера -17 поступает также на управляющий вход дешифратора 9, т,е. на второй вход элемента И 23 и на вход инвертора 24 (фиг.2). При этом дешифратор 9 настроен на число М, т.е. на выходе дешифратора 9 появляется логическая

"1" только при подаче на его входы двоичного кода числа М (например, М=23).

На информационный вход устройства, т.е, на вход преобразователя 6 подается M-разрядный последователвньгй биимпульсный код коррекции по двум линиям в виде кода единиц и кода нулей, Код коррекции имеет следующую структуру: младший разряд — знак, следующие (М-1)/2 разрядов - код точной коррекции, старшие (М-1)/2 разрядов — код грубой коррекции. На информационном выходе преобразователя 6 формируется прямой код коррекции, разряды которого поочередно подаются на информационный вход регистра 5 сдвига. На тактовом выходе преобразователя 6 формируются тактовые импульсы сдвига, которые через элемент ИЛИ

19 подаются на тактовый вход регистра

5 1506570 6

5 сдвига и на счетный нхо вход счетчика 8 отличного от нуля, на его выходе по(фиг,З.lв).

° ° является логическая "1" (фиг.3.1з, Под воздействием тактовых импуль- 4з) которая подае ся сон сдвига разряды ко а ко да коррекции по- вход формирователя 11, разрешая его очередно записываются в егист 5 работу, СигнаЛ управления в виде лосдвига. Одновременно счетчик 8 под- гической "1" (фиг, 3. 1и, 4и) появляетсчитывает тактовые имп льсы с ся на выходе формирователя 11 по срет.е. число раэ я ов ко а к р р д ода коррекции, зу импульса, поступающего с выхода записанных в регистр 5 сдвига . При !р формирователя !О. записи в регистр 5 сдвига всего М- Сигнал управления (фиг.3.1и) посраэрядного ко а ко д оррекции на выходе тупает на первый управляющий вход дешифратора 9 наст оен р нного на число фазосдвигающего блока 2 и изменяет

M поянляется логическая "1" его коэффициент деления на К + (фиг.3.16), которая по ается н дает а пер- !5 в зависимости от знака (на фиг.3.1, вый вход формирователя 10 и на второй 3.2 и 4, например, с К =5 íà K=4) вход элемента ИЛИ-НЕ 21. Фо ми ов ормирова- что приводит к сдвигу шкалы времени, тель 10 выделяет второй после п явр, ле появ- формируемой делителем 3. Однонременно ления логической "1" на пе вом рвом входе, сигнал управления открывает элемент импульс (фиг,З. 1ж) нэ после овател до а ь- И 7, разрешая прохождение импульсов ности импульсов (фиг.З. 1е) п с ф . . ), поступаю- с выхода мультиплексора 22 с периодом щих с выхода делителя 3 через муль- понторения (К i !) К, Т на вход нычитатиплексор на erо вт типле о второй вход, ния реверсивного счетчика 4 (фиг.З. 1ê, Импульс с выхода формирователя 10 4к) . Код грубой коррекции N,,запи(фиг.3,1ж) поступает на пе вь" рвыи вход >5 санный в счетчик 4, начинает считыии », запиэлемента ИЛИ-НЕ 21, на втором входе которого присутствует логическая "1" Как только во всех разрядах счетс выхода дешифратора 9 (фиг.3.16) а

Ф чика 4 появляется логический "0" на на остальные нходы подается код груб и его выходе появляется логический "0 о коррекции с выходов старших раз- (ф . . ) ко рядов регистра 5 сдвига Если ко фиг,З.!з) ко сдвига ° сли код мирователь 1l в исходное сбстояние. грубой коррекции не равен нулю то

Логический "0" и с выхода формироватесостояние выхода элемента ИЛИ-НЕ 21 ля 11 (фиг. 3. 1и) восстанавливает исне изменяется (логический "0") (о ческии 0 ходный коэффициент деления блока 2

Импульс с выхода формирователя 10 и запрещает прохождение импульсов через элемент И 13, открытый сигналом 35 через элемент И 7, логическои "1" с выхода RST-т игге Таким образом, в течение времени

12 (фиг.З. 1л 4л) п охо ит

), р одит на вход считывания информации, записанной синхронизации D-тригге а 14 (фиг 3 1

4м).

P (фиг.З. 1м, в реверсивный счетчик 4 импульсами с периодом повторения (К + 1) К,Т

При этом знак ко ек ии с рр ц ныхода

40 коэффициент деления фазосдвигающего младшего разряда регистра 5 сдвига блока 2 отличается на + 1 от исходэаписывается в П-т игге 14 р р 1, с выхода ного, что приводит к сдвигу шкалы которого подается на второй управляю- времени на величину щий вход фазосдвигающего блока 2, По срезу импульса с выхо а фо ми да формиро- 45 где N» — величина грубой коррекции; вателя 10 переворачивается R-S-T- К, — коэффициент деления делитетригге 12. Логи с

p . че кий 0 с его вы- ля 3 от входа до выхода, хода (фиг. 3. 1л) зап е ает п ох р щ р ождение соединенного с вторым входом

° е Му сигналов через элемент И 13 (фиг.3.1м мультиплексора 22;

3 .2м) . Т вЂ” период повторения импульсов

Импульс с выхода формирователя 10 поступает также на вхо и е д редваритель- Перепад напряжения на выходе рер р ого счетчика 4 ной записи еве сивн версивного счетчика 4 из логической и на второй вход формирователя 11, По фронту этого импульса код грубой 55 ворачивает RST-триггер 15, на выкоррекции с выходов (И-1)/2 ст

)/ старших ходе которого появляется логическая разрядов регистра 5 сдвига переписы- "1" (фиг.3.!н). Этот сигнал эапускает формирователь 16 одиночного имзаписи в реверсивный счетчик 4 числа, пульса. Импульс с выхода формирова1506570

55 теля 16 (фиг,3.lo, 3.2о) проходит через элемент ИЛИ 20 и сбрасывает счетчик 8. На выходе дешифратора 9 появляется логический "0" (фиг.3.1б), который подготавливает формирователь

10 к работе. Этот же импульс переворачивает RST-триггер 17 ° Логичесвыхода RST-триггера 17 (фиг.3.1п, 3.2п) поступает на управляющие входы мультиплексора 22 и дешифратора 9. При этом на выход мультиплексора 22 начинают проходить импульсы с выхода фазосдвигающего блока

2 с периодом повторения КТ, Логическая "1" на управляющем входе дешифратора 9 изменяет его настройку на

l I-- 1 число

Логическая " 1" с выхода RST-триггера 17 (фиг.3.1п) поступает также на вход, запуска генератора 18 пачки импульсов, На тактовый вход генератора 18 через мультиплексор 22 поступают импульсы с выхода фазосдвигающего блока 2 (фиг,3,1д, 3,2д), под воздействием которых на выходе геНератора 18 формируется пачка из (М-1)/

/2 импульсов (фиг.3.1р, 3.2р) ° Пачка импульсов через элемент ИЛИ 19 поступает 1 а тактовый вход регистра 5 сдвига и на счетный вход счетчика 8 (фиг.3,1в, 3.2в). Информация, записанная в регистр сдвига, сдвигается на (M-1)/2 разрядов, при этом в старших (М-1)/2 разрядах, соединенных с входами записи реверсивного счетчика 4, оказывается записанным код точной коррекции. Счетчик 8 подсчитывает число импульсов в пачке, После окончания сдвига информации в регистре 5 сдвига на выходе дешифратора 9, настроенного на число (I!-1)/

/2, появляется логическая " 1" (фиг.3.26), которая запускает формирователь 10, Второй после поступления логической "1" на первый вход формирователя

10 импульс из последовательности импульсов на выходе мультиплексора 22 выделяется формирователем 10 (фиг.3.2ж). По срезу этого импульса переворачивается RST-триггер 12 (фиг,3,2л). По фронту импульса, поступающего с выхода формирователя 10, происходит запись кода точной коррекции из старших (М-1)/2 разрядов регистра 5 сдвига в реверсивный счетчик

4. На выходе реверсивного счетчика появляется логическая "1" (фиг ° 3.2з), 5

1О

50 которая поступает на первый вход формирователя 11. Ilb срезу импульса, поступающего с выхода формирователя

10 на второй вход формирователя 11, на выходе формирователя 11 формируется сигнал управления.

Сигнал управления изменяет коэффициент деления фазосдвигающего блока 2 на К + 1 (фиг.3,2д) и разрешает прохождение импульсов с выхода мультиплексора 22 с периодом повторения (К + 1)Т через элемент И 7 на вход вычитания реверсивного счетчика 4 (фиг.3.2 к).

Изменение коэффициента деления фазосдвигающего блока 2 приводит к сдвигу шкалы времени, формируемой делителем 3, в течение времени считывания кода точной коррекции реверсивным счетчиком 4.

После окончания считывания кода точной коррекции на выходе реверсив-. ного счетчика 4 появляется логический

"0" (фиг,3.2э), который возвращает формирователь 11 в исходное состояние, Логический "0" с выхода формирователя 11 (фиг,3,2и) восстанавливает исходный коэффициент деления фазосдвигающего блока 2 и запрещает прохождение импульсов через элемент И 7.

В результате точной коррекции шкала времени сдвигается на велиггину

htz = Ф ИТ, где К вЂ” величина точной коррекции.

Перепад напряжения из логической

"1" в логический "0" на выходе счетчика 4 (фиг,3.2з) переворачивает

RST-триггер 15, на выходе которого появляется логический "0" (фиг.3.2н), На этом коррекция шкалы времени заканчивается, Таким образом, в результате еди-. ного цикла коррекции, т,е. прн однократной коррекции, содержащей грубую и точную части, шкала времени, форми- руемая делителем 3, сдвигается на величину и =и i+ t,= (И,К, +N ) Т, обеспечивая тем самым в условиях увеличения диапазона коррекции сохранение высокой точности, В случае равенства нулю величины грубой коррекции, что имеет место при расхождении хранимой и эталонной шкал времени в пределах диапазона точной коррекции,при записи в pesep« сивный счетчик 4 нулевого кода грубо!: коррекции, состояние выхода реверсив1506570

10 ного счетчика 4 не изменяется (логический "О").

Для того, чтобы обеспечить коррекцию в эти условиях, предназначен элемент ИЛИ-НЕ 21, первый (инверсный) вход которого подключен к выходу формирователя 10, второй (инверсный) вход подключен к выходу дешифратора

9, а остальные входы подключены к старшим (М-1)/2 разрядам регистра 5 сдвига, После подачи команды (фиг.4а) и установки триггеров 17 (фиг.4п), 12 (фиг.4л), 15 (фиг.4н), счетчика 8 (фиг.4в), а также переключения мультиплексора 22, после записи кода коррекции в регистр 5 сдвига (фиг,4в) аналогично рассмотренному случаю на выходе дешифратора 9 появляется логическая "1" (фиг,4б), которая поступает на второй (инверсный) вход элемента ИЛИ-НЕ 21, а также запускает формирователь !О. На выходе формирователя 10 появляется импульс (фиг.4ж), который подается на первый (инверсный) вход элемента ИЛИ-HE 21, На остальные входы элемента ИЛИ-НЕ 21 подается код грубой коррекции с выходов старших (М-1)/2 разрядов регистра 5 сдвига, так как код грубой коррекции равен нулю, импульс, формирующийся на выходе формирователя 10 (фиг,4ж), проходит через элемент HJIH-НЕ 21 (фиг,4с) на S-вход RST-триггера 15.

Логическая "1" с выхода RST-триггера

15 (фиг.4н) запускает формирователь З5

16, с выхода которого импульс (фиг,4о) сбрасывает счетчик 8 (фиг.4б) и переворачивает RST-триггер 17 (фиг.4п). Логическая "1" С выхода

Мт- риггера 17 переключает мульти- 40 плексор 22 и изменяет настройку дешифратора 9, а также запускает генератор 18 (фиг.4р). Затем производится,сдвиг содержимого регистра 5 сдвига и сдвиг шкалы времени на величину 45 точной коррекции аналогично работе устройства при точной коррекции.

Таким образом, точность однократной коррекции в предлагаемом устройстве в В раз вьппе, чем в известном.

При этом диапазон однократной коррекции не меньше диапазона однократной коррекции прототипа при максимальном множителе (B=10 ), Возможность проведения с высокой точностью одноступенчатой коррекции в расширенном диапазоне позволяет уменьшить затраты оператора на подготовку данных для коррекции, упростить работу оператора с предлагаемым устройством и снизить вероятность возникновения ошибочных действий оператора.

Формула и э обре т е н и я

Устройство для коррекции шкалы времени, содержащее последовательно соединенные генератор импульсов, фазосдвигающий блок и делитель частоты, а также реверсивный счетчик, регистр сдвига, преобразователь кода коррекции, первый элемент И, последовательно соединенные счетчик, дешифратор и формирователь одиночных импульсов, а также формирователь сигнала управления, RST-триггер и второй элемент И, причем первый вход первого элемента И соединен с вторым входом формирователя одиночных импульсов, информационный выход преобразователя кода коррекции — с информационным входоМ регистра сдвига, тактовый вход которого соединен со счетным входом счетчика, командный вход устройства соединен с входом установки RST-триггера, выход которого соединен с первым входом второго элемента И, входы записи реверсивного счетчика подключены к соответствующим выходам старших разрядов регистра сдвига, при этом выход реверсивного счетчика через формирователь сигнала управления соединен с первым управляющим входом фазосдвигающего блока и с вторым входом первого элемента И, выход которого подключен к входу вычитания реверсивного счетчика, выход формирователя одиночных импульсов подключен к второму входу формирователя сигнала управления, к входу предварительной записи реверсивного счетчика и к счетному входу

RST-триггера, вход преобразователя кода коррекции является информационным входом устройства, о т л и ч а— ю щ е е с я тем, что, с целью повышения точности коррекции, введены

D-триггер, последовательно соединенные первый дополнительный RST-триггер, дополнительный формирователь одиночных импульсов, второй дополнительный RST-триггер и генератор пачки импульсов, а также два элемента ИЛИ, элемент ИЛИ-HE и мультиплексор, к первому входу которого подключен выход фазосцвигающего блока, а выход мультиплексора подключен к второму входу формирователя одиночных импуль150

6570 сон тактоный вход регистра сдвига подключен к тактовому выходу преобразователя кода коррекции через первый элемент ИЛИ, установочный вход счетчика подключен к командному входу устройства через второй элемент ИЛИ, выход младшего разряда регистра сднига соединен с информационным входом D-триггера, к входу синхронизации которого подключен выход второго элемента И, а выход D-триггера соединен с вторым упранляющим входом фазосдвигающего блока, второй вход второго элемента И подключен к выходу формирователя одиночных импульсов, входы установки в "0" первого и второго дополнительных RST-триггеров соединены с командным входом устройства, вход установки в "1" перного дополнительного RST-триггера подключен к выходу элемента ИЛИ-НЕ, первый

12 вход которого подключен к выходу формирователя одиночныМ импульсов, второй вход соединен с выходом дешифратора, а остальные входы подключены к входам записи .реверсивного счетчика, второй вход второго элемента ИЛИ подключен к выходу дополнительного формирователя одиночных импульсов, 10 выход второго дополнительного RST-, триггера соединен с управляющими входами дешифратора и мультиплексора, второй информационный вход которого . соединен с выходом делителя частоты, тактовый вход генератора пачки импульсов подключен к выходу мультиплексора, а выход генератора пачки импульсов соединен с вторым входом первого элемента ИЛИ, счетный вход пер20 ного дополнительного RST-триггера подключен к выходу реверсивного счетчика.

1506570

1506570 щук

Составитель E.Åðåìèí

Р .дактор А.Козориз Техред М.Ходанич

Корректор Н,Борисова

Заказ 5448/56 Тираж 626 Подписное

ВНИИПИ Государственного комитета по изобретениям и открытиям при ГКНТ СССР

113035, Москва, Ж-35, Раушская наб., д. 4/5

Производственно-издательский комбинат "Патент", г. Ужгород, ул. Гагарина, 101