Устройство для коммутации сигналов сообщений

Иллюстрации

Показать всеРеферат

Изобретение относится к электросвязи. Цель изобретения - повышение пропускной способности путем исключения возможности столкновения и наложения сигналов сообщений. Устройство для коммутации сигналов сообщений содержит блок 1 динамический памяти, блок 2 фазовой селекции, блок 3 приоритетной селекции, блок 4 формирования приоритета коммутации, формирователь 5 импульса окончания сообщения и блоки 6 и 7 коммутации. При высокой интенсивности и одновременном поступлении сообщений на входы устройства последовательно коммутируются сообщения каждого из входов в соответствии с циклической процедурой обслуживания. Вход, по которому сообщение пришло первым, коммутируется первым. Поскольку в блоке 3 приоритетной селекции всегда выбирается только один вход, невозможны наложение сообщений, поступающих одновременно в разных линиях, и сбои коммутации. Изменяя порядок формирования приоритета коммутации в блоке 4, можно реализовать любую процедуру обслуживания. Устройство по пп. 2, 3 и 4 ф-лы отличается выполнением блока 2 фазовой селекции, блока 3 приоритетной селекции и блока 4, даны их ил. 3 з.п. ф-лы, 5 ил.

СОЮЗ СОВЕТСКИХ.

СОЦИАЛИСТИЧЕСКИХ

РЕСПУБЛИК (51) 4 Н 04 L 11/20

ОПИСАНИЕ ИЗОБРЕТЕНИ

Сл

ГОСУДАРСТВЕННЫЙ КОМИТЕТ

ПО ИЗОБРНЕНИЯМ И ОТКРЫТИЯМ

ПРИ ГКНТ СССР

К А ВТОРСКОМУ СВИ4ЕТЕЛЬСТВУ

1 (21) 4232841/24-09 (22) 20.04.87 (46) 07.09.89, Бюл, Ф- 33 (71) Институт электроники и вычислительной техники АН ЛатвССР (72) В.Я.Загурский и Г.И.Готлиб (53) 621.391 (088.8) (56) Патент EP У 0110390, кл. Н 04 1 11/20, 1984. (54) УСТРОЙСТВО ДЛЯ КОММУТАЦИИ СИГНАЛОВ СООБЩЕНИЙ (57) Изобретение относится к электросвязи. Цель изобретения — повышение пропускной способности путем исключения возможности столкновения и наложения сигналов сообщений. Устройство для коммутации сигналов сообщений содержит блок 1 динамической памяти, блок 2 фазовой селекции, блок 3 призритетной селекции, блок 4 формирова. ния приоритета коммутации, формироÄÄSUÄÄ 1506573 A 1

2 ватель 5 импульса окончания сообщения и блоки 6 и 7 коммутации. При высокой интенсивности и одновременном поступлении сообщений на входы устройства последовательно коммути-. руются сообщения каждого иэ входов в соответствии с циклической процедурой обслуживания. Вход, по которому сообщение пришло первым, коммутируется первым. Поскольку в блоке

3 приоритетной селекции всегда выбирается только один вход, невозможны наложение сообщений, поступающих одновременно в разных линиях, и сбои коммутации. Изменяя порядок формирования приоритета коммутации в блоке

4, можно реализовать любую процедуру обслуживания. Устройство по пп. 2, 3 и 4 ф-лы отличается выполнением блока 2 фазовой селекции, блока 3 приоритетной селекции и блока 4, даны их ил. 3 з.п.ф-лы, 5 ил.

3 506573

Изобретение относ ится к з tet тросвязи и может бь»ть использовано в каналах связи информационно-выч»»с лительных систем и сетей передачи дан5

»»р ио рите т»»ой» селекции и на входах ус т »1о Й с т В

"3;," (фиг. 5,6) запомненного сообщения поступает на вход блока 2 фазовой селекции » вход блока 3 приоритетной селекции, В блоке 2 фазовой селекции производится фазовая селекция спг»»ала

"3:" (фиг. 5,6), запомненного первым, в результате чего строб-импульсом (фиг. 5,д), соответствующим фронту сигнала "3»" (фиг. 5,6) в момент t с первого выхода строб-импульсов блока 2 фазовой селекции проных °

Цель изобретения — tto»t»ttttettt»e пропускной способности путем исключения возможности столкновения и»»апожен»»я сигналов сообщений, 10

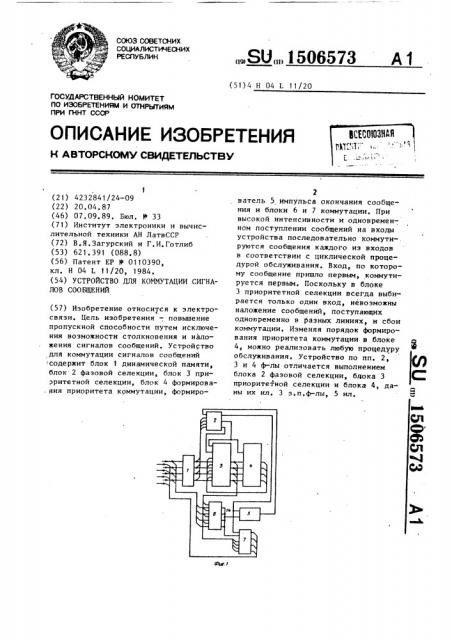

На фиг. 1 изображена структурная электрическая схема предлагаемого устройства; на фиг. 2 — структурная электрическая схема блока фазовой селекции; на фиг. 3 — структурная электрическая схема блока приоритет— ной селекции; на фиг ° 4 - структурная электрическая схема блока формирования приоритета коммутации; на фиг. 5 — временная диаграмма. 20

Устройство содержит блок динамической памяти, блок 2 фазовой селекции, блок 3 приоритетной селекции, блок 4 формирования приоритетов коммутации, формирователь 5 импульса окончания сообще»»ия и первый 6 и второй 7 блоки коммутации.

Блок фазовой селекции содержит первый 8, второй 9, третий 10 и чет- 30 вертьл» 11 элементы ИЛИ, элемент И !2, первый 13, второй 14 и третий 15 резисторы, первьп» 16, второй 17 и третий 18 ко»»де»»сатор»».

Блок приоритетной селекции содер — 35 жит инвертор 19, а в каждом канале

D-.òðèããåð 20 и первый 21 и второй 22 элементы ИЛИ-HF..

Блок формирования приоритета ком— мутации содержит инвертор 23, а в 40 каждом канале Р-триггер 24 и элемент

ИЛИ 25.

Устройство работает следующим образом.

В исходном состоянии на входах и 45 выходах устройства сообщения отсутствуют, На выходах блока 1 динамической памяти — логические 0 ° Ha всех выходах строб-импульсов блока 2 фазовой селекции отсутствуют импульсы стробирования, так что блок 3 приоритетной селекции и блок 4 формирования приоритетов коммутации, формирователь импульсов окончания сообщения и блок 7 коммутации заблокированы.

Поэтому на управляющем входе блока

2 фазовой селекции и выходах б:»ока

7 коммутации сигналы отсутствуют при любых состояниях на выходах блока 3 изводится стробирование блока 3 приоритетной селекции. В последнем происходит селекция сигнала "2," (фиг, 5,6) в соответствии с с »гналом 1 " (фиг. 5,6) приоритета, который будет среди других сигналов "2" (фиг. 5,а †) сообщений, эафиксированный на входах устройства в моМ» НТ

При этом в данном граничном случае фактически происходит выбор одного сообщения по результатам только фазовой селекции, т.е. первого поступившего сообщения, опережающего все остальные по фазе поступления.

На втором выходе блока 3 приоритетной селекции через время переходных процессов приоритетной селекции появляется сигнал логической "1", соответствующий сигналу "5 z" (фиг.5, б), который поступает на второй управляющий вход первого 6 и второго

7 блоков коммутации сообщений, Этим сигналом производится управление коммутацией сообщения "2 " (фиг. 5,6) с второго входа устройства.

Скоммутированное в блоке 6 коммутации сообщение поступает с его выхода на информационные входы формироll;1т(чя > импульсл (>f(<»f 1лния сообщения и нл вход второго б.»окл 7 к(ммутлции. С третьего ньгходл 6.»окл 2 фаЗОВОй Се".PÊftf»f» С ЗадЕржКОй ОТНОСИтельно момента t, на время »ереход5 ных процессов в блоке 3 приоритетной селекции поступает строб-импульс, разблокирующий формирователь 5 и блок

7 коммутации. В результате сигнал сообщения коммутируется во все выходы устройства за исключением второго, соответствующего сигналу "1" с второго выхода блока 3 приоритетной селекции ° 15

В момент t (фиг. 5, б) при окончании сигнала "2 " сообще1»ия, по его концевику, срабатывает формирователь

5 и выдает импульс окончания сообщения, которы»» поступает на управляю- 20 щий вход блока 2 фазовой селекции, На втором выходе блока 2 фазовой селекции появляется импульс стробировлния, соответствующий срезу сигна- ла фазовой селекции (ф1»г. 5,д). В 25 результате стробирования блока 3 приоритетной селекции и блока 4 формирования приоритета >:(>tlìóòàöèè прекращается приоритетная селекция в блоке

3 и формируются нов»»е сигналы приори- 3р тета в блоке 4 формирования приоритетов коммутации. Форм>»рдвлние их в блоке 4 формирования приоритетов коммутации производится по отношени»д к логической "1" (сигнал "5 ", фи». 5, б), поступающей на вход блока 4 с вы35 .хода блока 3, т. е. соответствующему номеру входа приема сообщения, которое было скоммутировлно, На третьем выходе блока 2 фазовой 4р селекции в опреде тенный момент прекращается импульс стробирования (фиг. 5,д), в результате чего формирователь 5 и блок 7 коммутации выключаются и коммутация заканч1»вается. 4

С момента t> работа устройства повторяется. Однако, в отличие от момента t „ в блоке 3 приоритетной селекции производится выбор входа приема сообщений с макс»»вуальным приоритетом 5р среди всех входов устройства, поскольку сигналы сообщений приходят по ним одновременно. В этом граничном случае происходит выбор сообщения исключительно по значению сформиро55 ванного максимальн(г(> приоритета, поскольку фазы все» поступивших сообщений одинаковы, В момент t коммутация сигнала c(>(>1 fife f»f»>f с третьего

1>х(>, (л пр lfP!f » з;lк 111>lи>(л(1 T(Я и fl б. 1оке

4 ф(рмируf(>T(.я новые 1»рио >lfте fhf комму тлцlflt В м(ме 1»т t нлч>11»ле т(я и(>вый цикл комму T(fffèf», н pp .»ó.fb Tàòå которого будет скоммутировано сооб111ен1»е нл четвертоь» входе устройства.

Таким образом,при высокой интенсивности и однонременном поступлении сообщений» и л входы устройства последовательно коммутируются сообщения каждого из входов в соответствии с пиклической процедурой обслуживания °

Вход, по которому сообщение пришло первым, коммутируется первь»м. Поскольку в блоке 3 приоритетной селекции всегда выГ>ирлется только один вход, невозможно нлложение сообщен»п», поступающих одновременно в разных линиях, и сбои коммугации, Изменяя порядок формирования приоритета коммутации в блоке 4 формирования приоритетов коммутации можно в общем случае реализовать любую процедуру обслуживания.

Формула изобретения

1. Устройство для коммутации сигналов сообщений, содержащее первь»»» блок коммутации, информационные входы которого подключены к информационным входам блока динамической памяти, выходы которого соединены с соответствующими входами блока фазовой селекции, при этом информацио»»ные входы блока динамической памяти являются информационными входами устройства, о т л и ч а ю щ ° е е с я тем, что, с целью повышения йропускной способности путем исключения возможности столкновения и наложения сигналов сообщений введены второй блок коммутации, формирователь импульса окончания сообщения, блок формирования приоритетов коммутации и блок приоритетной селекции, выходы которого соединены с управляющими входами первого и второго блоков коммутации и с управляющими входами блока формирования приоритетов коммутации, выходы которого соединены с вторыми управляющими входами блока приоритетной селекции, первый вход стробирования которого подключен к, первому выходу блока фазовой селекции, второй выход которого соединен с вторым входом строгирования блока приоритетной селекции и с входом!

50657 стробиронания блока формирования приоритетов коммутации, выход формирова,теля импульса окончания сообщения соединен с управляющим входом блока

5 фазоной селекции, третий выход которого соединен с входами стробирования формирователя импульса окончания сообщения и второго блока коммутации, вход управления которого подключен к объединенным выходам блока коммутации, и с входом управления формирователя импульса окончания сообщения, при этом выходы блока динамической памяти подключены к первым управляющим входам блока приоритетной селекции, а выходы второго блока коммутации являются выходами устройства.

2. Устройство по п. 1, о т л и — 2p ч а ю щ е е с я тем, что блок фазовой селекции содержит четыре элемента ИЛИ, три резистора, три конденсатора и элемент И, единичный выход которого соединен с первыми входами 25 второго и третьего элементов KIH u с первым выводом первого резистора, второй вывод которого соединен с вторым входом второго элемента ИЛИ и с первым выводом первого конден- gp сатора, второй вывод которого соединен с выходом второго элемента ИЛИ, выход первого элемента KIH подключен к первому входу элемента И, инверсный выход которого соединен с первым выводом второго резистора, с первым входом четвертого элемента KIH и с первым выводом третьего резистора, второй вывод которого подключен к первому выводу третьего конденсатора и к второму входу четвертого элемента ИЛИ, выход которого соединен с вторым выводом третьего конденсатора, второй вывод второго резистора соединен с вторым входом третьего элемента ИЛИ и с первым выводом второго конденсатора, второй вывод которого подключен к выходу третьего элемента ИЛИ и является вторым выходом блока фазовой селекции, перным и третьим выходами которого являют50 ся соответственно выходы четвертого и второго элементов KIH нходы первого элемента ИЛИ являются соответствующими входами блока фазовой селекции, управляющим входом которого ян55 ляется второй вход элемента И.

3. Устр йстно по и. 1, о т л и ч а ю щ е е с я тем, что биок приоритетной c елекции содержит иннертор, а н каждом канале — первый и второй элементы ИЛИ-НЕ и D-триггер, выход которого соединен с первым входом первого элемента ИЛИ-HF., выход которого соединен с вторым входом второго элемента ИЛИ-НЕ, R-вход D-триггера соединен с вторым входом первого элемента HtIH-HF., выход инИертора — с перными входами вторых элементов

ИЛИ-HE каждого канала, при этом Rвход D-триггера предыдущего канала соединен с выходом второго элемента

ИЛИ-HE последующего канала, а ныход второго элемента KIH-HF. первого канала соединен с R-входом D-триггера последнего канала, С-входы D-триггеров всех каналов объединены и являются первым входом стробирования блока приоритетной селекции, вторым входом стробиронания которого является вход инвертора, D-входы D-триггеров каждого канала являются первыми управляющими входами блока прио-. ритетной селекции, вторыми управляющими входами которого являются третьи входы вторых элементов ИЛИ-HE каждого канала, выходы D — триггеров каждого канала являются выходами блока приоритетной селекции.

4. Устройство по и. 1, о т л и— ч а ю щ е е с я тем, что блок формирования приоритета коммутации содержит инвертор, а в каждом канале— элемент ИЛИ и D-триггер, выход которого соединен с первым входом элемента KIH второй вход которого подключен к R-входу D-триггера, выход элемента KIH первого канала подключен к нходу инвертора, выход которого соединен с R-входом D-триггера последнего канала, R-вход D-триггера предыдущего канала подключен к выходу элемента ИЛИ последующего канала, С-входы D-триггеров каналов объединены и являются входом стробирования блока формирования приоритетов коммутации, управляющими входами которого являются D-входы D †òðèã-, геров, выходы которых являются выходами блока формирования приоритетов коммутации.

150 > 73

Фиг,2

1506573

Фиг.4

Составитель О. Геллер

Техред М. Хода нич Корректор О.Ципле

Редактор И. Горная

Заказ 5449/57 Тирах 626 Подписное

ВНИИПИ Государственного комитета по изобретениям и открытиям при ГКНТ СССР

113035, Москва, Ж-35, Раушская наб., д. 4/5

Производственно-издательский комбинат "Патент", г. Ужгород, ул. Гагарина, 101