Двоичный шифратор

Иллюстрации

Показать всеРеферат

Изобретение относится к автоматике и вычислительной технике и может быть использовано в системах обработки информации при реализации цифровых вычислительных машин и элементов дискретной автоматики. Целью изобретения является упрощение устройства. Поставленная цель достигается тем, что в двоичный шифратор, содержащий группу 9 полных 2<SP POS="POST">к</SP>-входовых шифраторов 4,5 и первый неполный шифратор 2, дополнительно введены L-1 неполный шифратор 1 и полный 2<SP POS="POST">к</SP> - входовой шифратор 3. 1 п. 1 ил.

СОЮЗ СОВЕТСКИХ.

СОЦИАЛИСТИЧЕСКИХ

РЕСПУБЛИК (51) 4 С 06 Р 5/00

ОПИСАНИЕ ИЗОБРЕТЕНИЯ

К АВТОРСКОМУ СВИДЕТЕЛЬСТВУ

ГОСУДАРСТВЕННЫЙ КОМИТЕТ

ПО ИЗОБРЕТЕНИЯМ И ОТКРЫТИЯМ

ПРИ ГКНТ СССР (21) 4366400/24-24 (22) 20, 01, 88 (46) 15.09.89. Вюл, N - 34 (71) Вычислительный центр СО АН СССР (72) П А,Ким, К.С.Алсынбаев, В,А,Забелин и Н.А.Осипов (53) 681.325(088,8) (56) Авторское свидетельство СССР

N- 857972, кл. С 06 Р 5/00, 1979, Авторское свидетельство СССР

Ф 574715, кл. G 06 F 5/00, 1976, „„SU„„1508203 А 1

2 (54) ДВОИЧНЫЙ ШИФРАТОР (57) Изобретение относится к автоматике и вычислительной технике и может быть использовано в системах обработки информации при реализации цифровых вычислительных машин и элементов дискретной автоматики, Целью изобретения является. упрощение устройства. Поставленная цель достигается тем что в двоичный шифратор, содержаФ

k щий группу 9 полных 2 — входовых шифраторов 4, 5 и первый неполный шифратор 2, дополнительно зведены 1-1 неk полный шифратор 1 и полный 2 -входовой шифратор 3, 1 п,, 1 ил, ветствующий вход каждого из полных шифраторов 5 и 6, вследствие чего на выходах полного шифратора 5 появляют-. ся сигналы, соответствующие младшим разрядам кода, Сигналы, поступившие на входы полного шифратора 6, подаются на соответствующий вход каждого из полных шифраторов 3 и 4, вследствие чего появляются сигналы на выходах шифраторов 3 и 4, а следовательно и на выходе полного шифратора 6,. которые соответствуют старшим разрядам кода.

Формула изобретения Составитель М.Аршавский

Редактор А,Огар Техред Л.Олийнык Корректор Н. Борисова

Заказ 5541/50 Тираж 668 Подписное

ВНИИПИ Государственного комитета по изобретениям и открытиям при ГКНТ СССР

113035, Москва, Ж-35, Раушская наб., д. 4/5

Производственно-издательский комбинат "Патент", r.Óæãîðîä, ул. Гагарина,101

3 1508203

Изобретение относится к автоматике и вычислительной технике и может быть использовано в системах обработки информации при реализации цифро5 вых вычислительных машин и элементов диск ретной ав томат ики, Цель изобретения — упрощение шифратора.

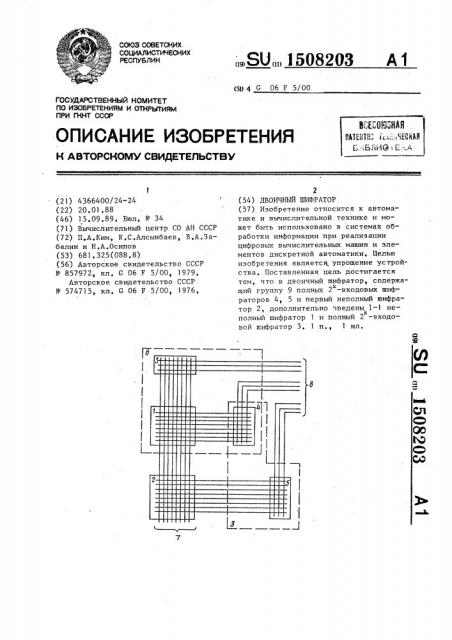

На чертеже показана функциональ- 10 ная схема двоичного.шифратора, В качестве примера рассмотрен шифратор при m=512.

Шифратор содержит неполные шифраторы 1 и 2.и полные 2 -входовые шиф- 15 раторы 3-5,.при этом неполный шифратор 1 и два полных шифратора 3 и 4 образуют полный шестиразрядный шифратор 6, входы неполного шифратора 2 являются входами 7 устройства а вы- 20

1с

У ходы 2 -входового полного шифратора

2k

5 и 2 -входового полного шифратора

6 образуют выходы 8 устройства, Полные 2 -входовые шифраторы 4 и 5 в

k совокупности образуют группу 9 полных 2 -входовых шифраторов, В рассматриваемом примере k--3 неполный шифратор 1 имеет 64 входа, Выходы полного шифратора 5 являются младшими выходами. полного девятиразрядного шифратора, а выходы полных шифраторов 3 и 4 образущт выходы полного шетиразрядного шифратора 6, которые, в свою очередь, являются старшими выходами полного девятиразрядно" 35 го шифратора.

Устройство работает покаскадно, при этом первым срабатывает каскад, образованный шифраторами 5, 6 и 2, а затем каскад образованный шифратора- 40 ми 3, 4 и 1, При поступлении сигнала на один из входов полного девятиразрядного шифратора он подается на соотДвоичный шифратор, содержащий первый неполный шифратор и группу полk ных 2 -входовых шифраторов, о т л ич а ю шийся тем, что, с целью упрощения устройства, он дополнительно содержит 1-1 неполный шифратор

1ояam (1 = — — — I), где m — число входов двоичного шифратора, полный 2 -входовый шифратор, а группа 2 -входовых полных шифраторов состоит из 1 2 -входовых полных шифраторов, причем входы первого неполного шифратора являются входами двоичного шифратора, выходы которого являются выходами всех полk ных 2 -вхадовых шифраторов, входы

i-ro неполного шифратора (i=2-1) соединены.с первыми выходами (i-1)-ro неполного шифратора, вторые выходы . которого соединены с входами (i-1)-го

k полного 2 -входового шифратора группы, первые выходы 1-го неполного шифратора соединены с входами полного

2 -входового шифратора, а вторые вхоk ды соединены с входами 1-ro полного шифратора группы.