Арифметическое счетное устройство

Иллюстрации

Показать всеРеферат

Изобретение относится к вычислительной технике и может быть использовано в устройствах цифровой обработки информации в двоично-десятичной системе счисления. Цель изобретения - повышение быстродействия арифметических операций. Арифметическое счетное устройство содержит распределитель 1 тактовых импульсов и N декад, каждая из которых включает в себя программируемый счетчик 2, двоично-десятичный реверсивный счетчик 3, блок 4 пропускания импульсов, элемент И 5 и элемент И 6, соединенные между собой функционально. Подекадное выполнение арифметических операций с учетом значений сигналов переноса из предыдущих декад позволяет существенно повысить быстродействие арифметического счетного устройства. 4 ил.

СОЮЗ СОВЕТСНИХ

СОЦИАЛИСТИЧЕСКИХ

РЕСПУБЛИК (19) (П) (51) 4 С 06 F 7/62

ОПИСАНИЕ ИЗОБРЕТЕНИЯ

Н ABTOPCHGMY СВИДЕТЕЛЬСТВУ 7с-1

I

Tj I I Ф 1 д)иР/ т, ГОСУДАРСТВЕННЫЙ КОМИТЕТ

ПО ИЗОБРЕТЕНИЯМ И ОТКРЫТИЯМ

ПРИ ГКНТ СССР

1 (21) 4369528/24-24 (22) 26,01,88 (46) 15,09,89, Бюл. Ж 34 (72) А.В.Библиев, И.Б.Андронников и И.Г.Кудзин (53) 681.325(088,8) (56) Титце У,, Шенк К. Полупроводниковая схемотехника, М.: Мир, 198?, с, 334, Ланцов А.Л. и др. Цифровые устройства на комплементарных МДП интегральных микросхемах М.: Радио и связь, 1983, с. 223-224, рис.7.20, (54) АРИФМЕТИЧЕСКОЕ СЧЕТНОЕ УСТРОЙСТВО (57) Изобретение относится к вычислительной технике и может быть ис2 польэовано в vcTpoAr.òBàõ цифровой обработки информации в двоично-десятичной системе счисления, Цель изобретения — повьппение быстродействия арифметических операций. Арифметическое счетное устройство содержит распределитель 1 тактовых импульсов и и декад, каждая из которых включает в себя программируемый счетчик 2, двоично-десятичный реверсивный счетчик 3, блок 4 пропускания импульсов, элемент И 5 и элемент И

6, соединенные между собой функционально. Подекадное выполнение арифметических операций с учетом значений сигналов переноса из предыдущих ,декад позволяет существенно повысить быстродействие арифметического счетного устройства. 4 ил.

3 1508210

Изобретение относится к вычислительной технике и может быть использовано в устройствах цифровой обработки информации в двоично-десятичной системе счисления.

Цель изобретения — повьппение быстродействия арифметических операций.

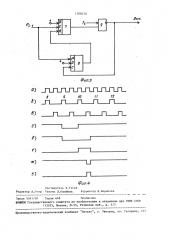

На фиг.1 представлена функциональная схема арифметического счетного 10 устройства; на фиг.2 — временные диаграммы его работы; на фиг.3 — функциональная схема блока пропускания импульсов; на фиг,4 — временные диаграммы работы блока пропускания им- 15 пульсов.

Арифметическое счетное устройство содержит распределитель l тактовых импульсов и и декад, каждая из которых включает в себя программируемый 20 счетчик 2, двоично-десятичный реверсивный счетчик 3, блок 4 пропускания импульсов, элемент И 5 и элемент

ИЛИ 6, соединенные между собой функционально.

Блок 4 пропускания импульсов образуют первый и второй триггеры 7, и 8 и элемент И-НЕ 9, соединенные межмежду собой функционально, Арифметическое счетное устройство. 30 работает следующим образом.

Перед началом выполнения арифметической операции по стартовому сигналу (не показан) происходит запись ко- 3g да одной декады первого слагаемого Х; в программируемый счетчик 2, запись кода одной декады второго слагаемого

У; в двоично-десятичный реверсивный счетчик 3, а также начальная установка 40 программируемого счетчика 2, необходи" мая для его работы в однократном режиме.

Импульсы Т1 (фиг, 26, фиг, 46) с первого выхода распределителя 1 импульсов одновременно поступают на счетный вход программируемого счетчика 2 и через открытый элемент И 5 и элемент ИЛИ 6 .на счетный вход двоично-десятичного реверсивного счетчика

3. После прохождения числа импульсов, численно равного коду одной декады первого слагаемого Х, на выходе программируемого счетчика 2 формируется сигнал P (фиг.2г), под действием кото 5 рого элемент Vi 5 закрывается и прохождение импульсов Т1 на счетный вход двоично-десятичного реверсивного счетчика 3 прекращается (фиг.2д). При этом этом на выходе двоично-десятичного счетчика 3 оказывается сформированным результат выполненной арифметической . операции Б;У,+Х; (в зависимости от выбранной арифметической функции

"Сложение/вычитание"), Блок 4 пропускания импульсов отслеживает появление сигнала переноса

Р;, (фиг.2е, фиг.4г) из предыдущей декады арифметического счетного устройства и при его наличии из последовательности импульсов Т2 (фиг.2в, фиг,4в) формирует импульс (фиг, 2ж, фиг.4з), поступающий через элемент

ИЛИ 6 на счетный вход двоично-десятичного реверсивного счетчика 3 (фиг,2з), который осуществляет сложение (вычитание) его с ранее вычисленным результатом.

Таким образом, двоично-десятичный реверсивный счетчик 3 осуществляет сложение (вычитание) ранее записанного в него кода Y одной декады второ1 го слагаемого с числом импульсов (фиг.2з), поступающих на его счетный вход и численно равных сумме сигналов, соответствующих коду Х одной декады

1 первого слагаемого (фиг.2д),и сигнала переноса F; из предшествующей декады (фиг,2ж, фиг.4з), т.е. на выходе двоично-десятичного реверсивного счетчика 3 оказывается сформированным результат одной декады выполненной ариф( метической операции S =У +Х.+Р.

1 -1- 1 — 1-1

Блок 4 пропускания импульсов (фиг.31 работает следующим образом, По сигналу переноса Р„ (фиг,2е, фиг.4г) из предыдущей декады арифметического счетного устройства происходит обнуление триггера 8 (фиг.4д), выходной сигнал которого разрешает работу триггера 7. -Далее по положительному перепаду уровня напряжения

Р (фиг.2е, фиг.4г) происходит установка в "1" триггера 7.

Элемент И-НЕ 9 при совпадении сигнала Т2 (фиг.2в, фиг.4в) и сигнала с выхода триггера 7 формирует выходной сигнал блока 4 пропускания импульсов.

По срезу этого сигнала триггер 8 устанавливается в единичное состояние, блокируя триггер 7, По поступлении на вход блока 4 пропускания импульсов очередного сигнала переноса Р;, из предыдущей декады устройства его работа повторяется.

5 150821

Таким образом, введение в арифметическое счетное устройство блока пропускания одиночных импульсов, блока сложения и распределителя импульсов позволяет проводить подекадное

5 выполнение арифметических операций в дв оично-десятичной системе счисления с учетом значений сигналов переноса из предыдущих декад, что при числе двоично-десятичных декад более трех дает воэможность существенно повысить быстродействие арифметического счетного устройства, работающего в двоично-десятичной системе счисле- 15 ния.

Формула изобретения

1, Арифметическое счетное устрой- 20 ство, содержащее вход тактовой частоты и п декад; где n — число декад входной информации, каждая из которых состоит из программируемого счетчика, установочные входы которого соеди- 25 иены соответственно с информационными входами 1-й декады первого слагаемого устройства, где i=1,2,3,...,n, выход переноса программируемого счет-. чика соединен с первым входом эле- 30 мента И, второй вход которого соединен с счетным входом программируемого счетчика, и двоично-десятичного реверсивного счетчика, установочные входы которого соединены соответст35 венно с информационными входами i-й декады второго слагаемого устройства, а разрядные выходы двоично-десятичного реверсивного счетчика являются информационными входами -й декады 40 устройства, о т л и ч а ю щ е е с я

0 6 тем, что, с целью повынения быстродействия выполнения арифметических операций, в устройство введен распределитель тактовых импульсов, а в каждую из и декад устройства введены блок пропускания импульсов и элемент .

ИЛИ, причем выходы блока пропускания импульсов и элемента И соединены с . входами элемента ИЛИ, выход которого соединен со: счетным входом двоично- десятичного реверсивного счетчика, управляющий вход блока пропускания и импульсов -й декады соединен с выходом переноса двоично-десятичного реверсивного счетчика (i-1)-й декады, вход тактовых импульсов устройства соединен с входом распределителя импульсов, первый выход которого соединен с вторыми входами элементов И> а второй выход распределителя импульсов соединен с информационными входами блоков пропускания импульсов в каждой из и декад .устройства.

2. Устройство по п, 1, о т л и— ч а ю щ е е с я тем, что блок пропускания импульсов содержит первый и второй триггеры и элемент Vi — НЕ, причем тактовый вход первого триггера соединен с входом установки в "0" второго триггера и является управляющим входом блока, выход первого триггера соединен с первым входом элеэлемента И-НЕ, второй вход которого является информационным входом блока, выход элемента И вЂ” НЕ соединен с выходом блока,и с тактовым входом второго триггера, выход которого соединен с входом установки в "0 i первого триггера, фиг.2

10 г) е)

Составитель В,Гусев

Редактор А.Огар Техред JI. ÎëèHíûê Корректор Н. Борисова

Заказ 5541/50 Тираж 668 Подписное

ВНИИПИ Государственного комитета по изобретениям и открытиям при ГКНТ СССР

113035, Москва, Ж-35, Раушская наб., д. 4/5

Производственно-издательский комбинат "Патент", r. Ужгород, ул. Гагарина, 101