Устройство микропрограммного управления с контролем

Иллюстрации

Показать всеРеферат

Изобретение относится к вычислительной технике и может быть использовано при построении устройств микропрограммного управления с обнаружением ошибок. Целью изобретения является сокращение оборудования устройства микропрограммного управления. Устройство содержит первый элемент ИЛИ 1, счетчик адреса 2, первый элемент И 3, блок памяти микрокоманд 4, второй элемент ИЛИ 5, блок контроля 6, третий элемент ИЛИ 8, первый триггер 9, второй элемент И 10 и второй триггер 11. Цель достигается введением первого, второго и третьего элементов ИЛИ, первого и второго элементов И, что позволяет контролировать и исправлять ошибки, вызванные физическим отказом блока памяти микрокоманд 4, с меньшим объемом оборудования. 2 ил.

СОЮЭ СОВЕТСНИХ.

СОЦИАЛИСТИЧЕСНИХ

РЕСПУБЛИН,(50 4 G 06 Р 9/22. 11/00

ОПИСАНИЕ ИЗОБРЕТЕНИЯ

1Z

f7

ГОСУДАРСТВЕННЫЙ НОМИТЕТ

ПО И305РЕТЕНИЯМ И ОТКРЫТИЯМ

ПРИ ГННТ СССР (21) 4338508/24-24 (22) 07.12,87 (46) 15,09,89. Бюл, Р 34 (71) Тбилисский научно-исследовательский институт приборостроения

„и средств автоматизации Научно-ис следовательского объединения "Элва" (72) А,P.×à÷àíàøâèëè, Г.С.Хуршудова и Е.В.Давыдова (53) 681. 32(088. 8) (56) Авторское свидетельство СССР

Р 1267415, кл, G 06 Р 9/22, 1985.

Авторское свидетельство. СССР

II - 1309024, кл. G 06 P 9/22, 1985, (54) УСТРОЙСТВО МИКРОПРОГРАММНОГО

УПРАВЛЕНИЯ С КОНТРОЛЕМ (57) Изобретение относится к вычислительной технике и может быть ис„.SU„„1508211 . А1

2 пользовано при построении устройств микропрограммного управления с обнаружением ошибок. Целью изобретения является сокращение оборудования устройства микропрограммного управления, Устройство содержит первый элемент

ИЛИ 1, счетчик адреса 2, первый элемент И 3, блок памяти микрокоманд 4, второй элемент ИЛИ 5, блок контроля

6, третий элемент ViJIH 8, первый триггер 9, второй элемент И 10 и второй триггер 11. Цель достигается введением первого, второго и третьего элементов ИЛИ, первого и второго элементов И, что позволяет контролировать и исправлять ошибки, вызванные физическим отказом блока памяти микрокоманд 4, с меньшим объемом оборудования. 2 ил.

1508211

Изобретение относится к вычислительной технике и может быть использовано при построении надежных устройств микропрограммного управле5 ния °

Цель изобретения - сокращение оборудования.

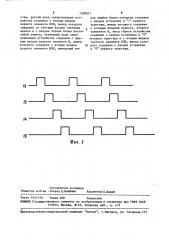

На фиг.1 приведена функциональная скема устройства микропрограммного управления.с коррекцией дефектных микрокоманд; на фиг.,2 — диаграммы управляющих сигналов.

Устройство (фиг.1) содержит пер-. вый элемент ИЛИ I,.счетчик 2 адреса, первый элемент И 3, блок 4 памяти микрокоманд,, второй элемент ИЛИ

5, блок 6 контроля, выход 7 микроопераций, третий элемент ИЛИ 8, первый триггер 9, второй элемент И 10, 20 второй триггер 11, с первого по четвертый входы 12-15 синхронизации уст. ройства, выход 16 пробирования микро. операций устройства, выход 17 ошибки устройства и вход 18 сброса устройства.

Рассмотрим работу устройства для случая коррекции ошибок, вызванных отказом блока. 4, Каждая микрокоманда записывается в,3О блок 4 в два последующих адреса..

Первым тактовым импульсом с входа 12 через элемент ИЛИ 1 из блока 4 по адресу а считывается макрокоманда, поступающая на выход микроопераций устройства и вход блока 6 контроля, который проверяет считанную с блоком информацию на четность или по коду

Хемминга Перепадом с - 1" .на "0" импульса с входа 12 в счетчике 2 форми- 4О руетсй адрес a+I., При верной микро.команде импульс. с входа 13 через элемент ИЛИ 5 в блоке контроля 6 на выходе а формирует сигнал, поступающий на выход 16,(для разрешения прие- 45 ма микрокоманды) и через элемент ИЛИ .

8 на вход установки нулевого состояния триггера.9. Импульсом с входа

14 через элемент ИЛИ 1 из блока 4 по. адресу . а+1 считывается микрокоманда того же содержания, а в счетчике 2 адреса 4 устанавливается адрес а+2.

Нулевое состояние триггера 9 блокирует в элементе И 3 импульс с входа 15.

Таким образом может быть блокирована повторная выдача микрокоманды с выхода 7. Если микрокоманда с блока 4 считана с ошибкой» то на инверсном выходе ошибки Ь блока 6 контроля им.. пульсом с выхода 13 формируется сигт. нал, устанавливающий триггер 9 в единичное состояние, Считанная из блока..

4 по адресу а+1 повторая микрокоманда поступает на выход 7 и на вход блока

6 контроля.

Если повторная микрокоманда верна, то на прямом выходе ошибки а блока 6 контроля формируется сигнал, разрешающий прием микрокоманды с выхода 7 и устанавливающий в нулевое состояние триггер 9. Если микрокоманда опять считана с ошибкой, то единичное состояние триггера 9 подтверждается. Импульс с входа 12 следующего такта через элемент И 10 устанавливает триггер 11 в единичное состояние, После установки триггера 11 в единичное состояние формируется сигнал Ошибки на выходе 17 и одновременно блокирует» ся формирование сигналов на выходе блока 6 контроля. Сигналом с входа 18 сброса устройства, можно сбрасывать триггеры 9 и 11 в нулевое .состояние. формула изобретения

Устройстве микропрограммного управления с контролем, содержащее счетм чик адреса, блок памяти микрокомайд» блОк кОнтрОля, первый и ВтОРОй триггеры, причем выход счетчика адреса соединен с. адресным входом блока памяти микрокоманд, выход которого соединен с информационным входом блока контроля и выходом микроопераций устройства, о т л и ч а ющ е е с я тем, что, с целью сокращения оборудования, оно содержит с первого по третий элементы ИЛИ, первый и второй элементы Vi, причем первый вход синхронизации устройства соединен с первым входом первого элемента ИЛИ и второго элемента И, выход которого соединен с входом. установки в "1" второго триггера, выход которого соединен с первым стробирующим входом блока контроля и с выходом ошибки устройства, вто рой вход синхронизации устройства соединен с первым входом второго элемента ИЛИ, выход котррого соеди» нен с вторым стробирующим входом блока контроля, прямой выход ошибки которого соединен с первым входом третьего элемента ИЛИ и с выходом стробирования микроопераций устройf5

Составитель А.Сошкин

Редактор А.Огар .Техред Л.Олийнык Корректор,Т. Палий

Заказ 5541/50 Тираж 668 Подписное

ВНИИПИ Государственного комитета по изобретениям и открытиям при ГКНТ СССР

113035, Иоскйа, Ж-35, Раушская наб., д. 4/5 о

Производственно-издательский комбинат "Патент", r.Óàãîðîä, ул. Гагарина,!01

6 15082 ства, третий вход синхронизации устройства соединен с вторым входом первого элемента ИЛИ, выход которого соединен со счетным входом счетчика адреса и с входом чтения блока посто янной памяти, четвертый вход синхронизации устройства соединен с первым входом первого элемента И, выход которого соединен с вторым входом 10 второго элемента .ИЛИ, инверсный выход ошибки блока контроля соединен с входом установки в "1" первого триггера, выход которого соединен с вторыми входами первого, второго элементов И, вход сброса устройства соединен с входом установки в "0" второго .триггера и с вторым вкодом третьего элемента ИЛИ, выход кото-. рого соединен с входом установки в "0" первого триггера,