Импульсно-цифровой вычислительный узел

Иллюстрации

Показать всеРеферат

Импульсно-цифровой вычислительный узел, содержащий блок синхронизации, реверсивный счетчик, выход которого является выходом узла, первый регистр, выход которого соединен с информационным входом первого преобразователя кода в частоту, выход которого подключен к первому входу первого элемента И, второй регистр, выход которого соединен с информационным входом второго преобразователя кода в частоту, выход которого подключен к первому входу: второго элемента И, первый и второй выходы блока синхронизации соединены с тактовыми входами соответственно первого и второго преобразователя кода в частоту, отличающийся тем, что, с целью повышения точности, в него введены третий и четвертый элементы и, первый и второй элементы ИЛИ и преобразователь кода в длительность импульса, установочный вход которого соединен с третьим выходом блока синхронизации, четвертый выход которого подключен к тактовому входу преобразователя кода в длительность импульса, информационный вход которого соединен с выходом реверсивного счетчика, суммирующий и вычитающий входы которого соединены с выходами соответственно первого и второго элементов ИЛИ, первые входы которых подключены соответственно к пятому и шестому выходам блока синхронизации, выход первого преобразователя кода в частоту соединен с первым входом третьего элемента И, выход второго преобразователя кода в частоту подключен к первому входу четвертого элемента И, прямой выход преобразователя кода в длительность импульса соединен со вторыми входами третьего и четвертого элементов И, инверсный выход преобразователя подключен к вторым входам первого и второго элементов И, выходы которых соединены соответственно с вторым и третьим входами первого элемента ИЛИ, седьмой и восьмой выходы блока синхронизации подключены к третьим входам соответственно первого и второго элементов И, девятый и десятый выходы блока синхронизации соединены с третьими входами соответственно третьего и четвертого элементов И, выходы которого подключены соответственно к второму и третьему входам второго элемента ИЛИ.

СОЮЗ СОВЕТСНИХ

СОЦИАЛИСТИЧЕСКИХ

РЕСПУБЛИН

09) (И),А1 (5D 4 06 F 15 32

ГОСУДАРСТВЕННЫЙ КОМИТЕТ

ПО ИЗОБРЕТЕНИЯМ И ОТНРЫТИЯМ

MPH ГКНТ,СССР

1 (21) 3825410/24-24 (22) 1).)2.84 (46) 15.09.89. Бюл. М-" 34 (71) Одесский политехнический институт (72) В.Е, Прокофьев и А.В. Фрид (53) 681 .333 (088. 8) (56) Авторское свидетельство СССР

N- 798859, кл. G 06 Р 15/32, 1979.

Время-импульсные вычислительные устройства/Под ред.В.Б.Смолова, E.Ï.ÓãðþìîBà.-N.: Радио и связь.

1983, с.222-229. (54) (57) ИМПУЛЬСНО-ЦИФРОВОЙ ВЫЧИСЛИТЕЛЪНЫЙ УЗЕЛ, содержащий блок синхронизации, реверсивный счетчик, выход которого является выходом узла, первый регистр, выход которого соединен с информационным входом первого преобразователя кода в частоту, выход которого подключен к первому входу первого элемента И, второй регистр, выход которого соединен с информационным входом второго преобразователя кода в частоту, выход которого подключен к первому входу: второго элемента И, первый и второй выходы блока синхронизации соединены с тактовыми входами соответствен.но первого и второго преобразователя кода в частоту, о т л и ч а ю— шийся тем, что, с целью повьппения точности, в него введены третий и четвертый элементы И, первый и второй элементы ИЛИ и преобразователь кода в длительность импульса, уста2 новочный вход которого соединен с третьим выходом блока синхронизации, четвертый выход которого подключен к тактовому входу преобразователя кода в длительность импульса, информационный вход которого соединен с выходом реверсивного счетчика, суммирующий и вычитающий входы которого соединены с выходами соответственно первого и второго элементов ИЛИ, первые входы которых подключены соответственно к пятому и шестому выходам блока синхронизации, выход первого преобразователя кода в частоту соединен с первым входом третьего элемента И, выход второго преобразователя кода в частоту подключен к первому входу четвертого элемента И, прямой выход преобразователя кода в длительность импульса соединен.со вторыми входами третьего и четвертого элементов И, инверсньпл выход преобразователя подключен к вторым входам первого и второго элементов И, выходы которых соединены соответственно с вторым и третьим входами первого элемента ИЛИ, седьмой и восьмой выходы блока синхронизации подключены к третьим входам соответственно первого и второго элементов И, девятый и десятый выходы блока синхронизации соединены с третьими входами соответственно третьего и четвертого элементов И, выходы которых подключены соответственно к второму и третьему входам второго элемента ИЛИ.

8232

F a

О, .л т(,э j л л если о, т(,. >

QN = 5N — 0

3 150

Изобретение относится к цифровой вычислительной технике и может быть использовано при построении цифровых сеток для решения уравнений в частных производных.

Цель изобретения — повышение точности, расширение функциональных возможностей и упрощение вычислительного узла.

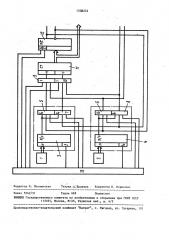

На чертеже изображена схема устройства.

Устройство содержит регистры 1 и

2, преобразователи 3 и 4 кода в частоту,элементы И 5-8, элементы ИЛИ

9 и 10, реверсивный счетчик 11, преобразователь 12 кода в длительность импульса и блок 13 синхронизации.

Предлагаемое устройство работает следующим образом.

Работа импульсно-цифрового вычислительного .узла основана на принципе автоматической частотной компенсации задаваемых и вырабатываемых сигналов.

В соответствии с указанным принципом условие выхода реверсивного счетчика 11 в установившийся режим имеет вид где Ы (ЬИ ) — число импульсов, приходящих на суммирующий (вычитающий) вход счетчика 11 за период повторения сигналов на широтно-импульсных седьмом и восьмом выходах блока 13 и на прямом инверсном .выходах преобразователя 12. Величина этого периода задается импульсами установки преобразователя 12, поданными с третьего выхода блока 13 синхронизации. Поскольку элементы ИЛИ 9 и 10 обеспе" .,чивают сложение частот входных сигналов (не совпадающих по фазе),то можно записать Ь N+ = (F> + Рб +

+Р (,)Т (,+ и АN = (Рт + Г8+

+ F6(,э )Т>(„ ° Отсюда получим в установившемся режиме

4 частотных пятом и шестом выходах блока 13, соответственно. )

Любой элемент И пропускает на вы-, ход импульсную последовательность, поступающую на его первый вход только тогда, когда на втором и третьем входах одновременно имеется сигнал

"1". При этом частоты выходных сиг 0 налов первого элемента И 5 определяе.тся как:

) /л Т л

Э(7(1Э <2 ) (,Эюесли с (<, л. л л

"7(О ЗИЭ ec H "7(< л /л о7(13 H 12 — длительности импульсов на седьмом выходе блока 13 и

25 прямом выходе пребразователя 12 соответственно, Р Э = Fy(1(" 11 M) — частота импульсов на выходе счетчика 3

30 Р„ „ — частота импульсов на входе первого выхода блока

13, Ю, — код на выходе регистрами

M = 2 т — коэффициент пропорциональности1

m — число разрядов входного кода. Из полученных выше выражений для частот F и F следует, что при лю40 бом соотношении между длительностял л ми ь („и <2, справедливо — Уй л г „(„Э (ь,2 — 7()Тэ(,Э

45 (2)

Аналогично найдем разность выход-, ных частот второго 6 и четвертого 8 элементов И.

Ф л.

Р -Fg = 2 Я2 Р.г(Э (" m @1,) ЛЭ/и (3)

611Э (Ъ ( где Р, Р<, РВ частоты следования импульсов на выходах соответствующих элементов И; частоты импульсных последовательностей на

Длительно сть импульсов на прямом выходе преобразователя 12 зависит от

55 частоты счетных импульcoB Р4/ э ступающих с четвертого выхода блока

13 и выходного кода узла N по закону

И 4/1Э

5 1508232 6

Подставляя выражения (2) и (4) в .— цифрового узла в установившемся формулу (1 ), получим уравнением свя- режиме с параметрами входных сигна зывающее выходной код импульсно-, лов л

0 = М 7 1 (Н У з < 7/ з ) Ngtg/1 (N 4((з "3/1>

N — 2 T 3 „У, „(,1„, — I< ) (5) Т Nа са+ И "5

N +N а B

1 (6) Предлагаемый узел может быть использован (аналогично прототипу) в качестве импульсно-цифрового эквивалента рвзистивного делителя напряжения. Например, пусть на первом, втором и четвертом выходах блока 13 поступают не совпадающие во времени импульсные последовательности частоты f, а на третьем выходе блока о

13 - импульсная последовательность частоты f1 = 2 f (указанные со И отношения между частотами управляющих сигналов обеспечивают одинаковую точность работы преобразователей 3, 4 и 12). Пусть также с выходов регистров 1 и 2 поданы коды N и N, на седьмом и восьмом выходах блока 13 — импульсы частоты f дли1 тельностью и ь,, на девятом и десятом выходах блока 13 — инверсии импульсов на седьмом и восьмом выходах блока 13 соответственно а пятый и шестой выходы блока 13 не используются (F -,з = 7< )/ = О) . Torpa Hs уравнения (5) находим N = f: (Н „с +

+ Nq ьз)/(Н,„+ Б > ), откуда, соглас но (4) Выражение (6) эквивалентно выраже15 нию, описывающему резистивный делитель при условии, что длительности входных и выходного импульсов соответствуют входным и выходному напряжениям делителя,а коды Ю, Б -про20 водимостям резисторов делителя.

Предлагаемый узел может быть также использован(в отличие от прототипа) при построении многоузловых сеточных устройств для решения урав25 нений в частных производных.

Таким образом, введение новых элементов и связей между ними позволяет использовать предлагаемый узел

3р в сеточных устройствах для решения дифференциальных уравнений в част— ных производных т.е. функциональные возможности узла по сравнению с прототипом расширяются. Кроме того, обеспечивается уменьшение объема оборудования †узел упрощается.

1508232

Техред .А. Кравчук, Корректор Н. Борисова

Редактор Л, Пчолинская

Заказ 5542/51 Тираж 668 Подписное

BHHHIIH Государственного комитета по изобретениям и открытиям при ГКНТ СССР

113035, Москва, Ж-35, Раушская наб., д. 4/5

Производственно-издательский комбинат "Патент", г. Ужгород, ул. Гагарина, 101