Запоминающая система для выборочного замещения ячеек блока памяти

Иллюстрации

Показать всеРеферат

Изобретение относится к вычислительной технике и может быть использовано для выборочного замещения ячеек блока памяти ячейками запоминающего устройства с электрической перезаписью и без разрушения информации. Целью изобретения является повышение надежности системы. Это достигается за счет того, что система содержит перепрограммируемый блок памяти управления коммутатором, адресные входы первой и второй групп которого соединены соответственно с адресными входами первой и второй групп электрически перепрограммируемого блока памяти замещения ячеек, а выход соединен с входом управления коммутацией информационных входов коммутатора. 2 ил.

СОЮЗ СОВЕТСНИХ

СОЦИАЛИСТИЧЕСКИХ

РЕСПУБЛИК (192 (112 (512 4 С 11 С 1) 40

ОПИСАНИЕ ИЗОБРЕТЕНИЯ

К А BTOPCHOIVIV СВИДЕТЕЛЬСТВУ

»»

»»

° °

ГОСУДАРСТВЕННЫЙ. КОМИТЕТ

ПО ИЗОБРЕТЕНИЯМ И ОТКРЫТИЯМ

ПРИ ГКНТ СССР

1 (21) 4271281/24-24 (22) 30.06.87 (46) 15,09.89. Бюл. 34 (72) Т.К.Цогоев, E,Н.Иванов, А.Е.Соловьев, И.Б.Беневич и А.Т.Новиков (53) 681.327.66 (088.8) (56) Патент США ¹ 3585607, кл. 340-179, опублик. 1971.

Авторское свидетельство. СССР № 489107, кл. G 06 F 11/00, 1972. (54) ЗАПОМИНАЮЩАЯ СИСТЕМА ДЛЯ ВЫБОРОЧНОГО ЗАМЕЩЕНИЯ ЯЧЕЕК БЛОКА ПАМЯТИ (57) Изобретение относится к вычислительной технике и может быть использовано для выборочного замещения

Изобретение относится к вычислительной технике и может быть использовано для выборочного замещения ячеек блока памяти ячейками запоминающего устройства с электрической перезаписью и без разрушения информации.

Целью изобретения является повышение надежности системы.

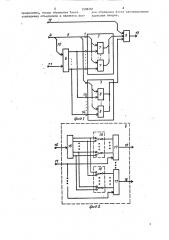

На фиг.1 приведена схема, поясняющая структуру и принцип действия системы, на фиг.2 — распределение адресных входов

В состав системы входят первая группа 1 адресных входов, электрически перепрограммируемый блок 2 па мяти замещения ячеек, электрически перепрограммируемый блок 3 памяти управления, группа 4 входов адреса системы, первая группа 5 адресных

Входов блока 2 памяти, блок 6 распределения адресных входов старших

2 ячеек блока памяти ячейками запоминающего устройства с электрической перезаписью и без разрушения информации. Целью изобретения является повышение надежности системы. Это достигается за счет того, что система содержит перепрограммируемый блок памяти управления коммутатором, адресные входы первой и второй групп которого соединены соответственно с адресными входами первой и второй групп электрически перепрограммируемого блока памяти замещения ячеек, а выход соединен с входом управления коммутацией информационных входов коммутатора, 2 ил. разрядов, блок 7 запоминающего устройства блока памяти замещения ячеек, блок 8 запоминающего устройства блока памяти управления, коммутатор 9, группа адресных входов

10 блока 6 распределения, вход 11

:обращения к блоку памяти . замещения ячеек, информационные входы 12 систе:мы, информационные выходы 13 систе мы, вторая группа 14 адресных вхо- дов блока памяти управления, пре" образователь 15 кода адреса, блок

16 бистабильных переключателей, блок

- 17 совпадения, адресный выход 18 блока совпадения,.

Для того, чтобы система, обеспечи" вала. замещение требуемых ячеек блока памяти ЭВМ, необходимо подключить адресные входы системы к адресным шинам ЭВМ, соединить вход обращения системы с входом сигнала обращения к блоку памяти ЭВМ, информационные

150828) 3 шины блока памяти ЭВМ отсоединить от информационных входов ЭВМ и сое-. динить с информаицонными входами системы информационные выходы сисФ

5 темы соединить с информационными входами 3BM; установить группу 16 бистабильных переключателей в положения, соответствующие кодам адресов участков блока памяти ЭВМ, в пределах которых расположены ячейки памяти, требующие замещения; записать в блоки 7, 8 по адресам (в пределах участков) корректируемых ячеек памяти; в блоки 7 — откорректированную информацию, в блоки 8 — код информации, разрешающий передачу информации в случае необходимости замещения ячейки и не разрешающий передачу информации. 20

Запоминающая система функциони- . рует следующим образом.

Во время работы ЭВМ при каждом обращении к ее блокам памяти часть 25 кода адреса (например, младшие разряды адреса) поступают на первую группу адресных входов блока 2 памяти замещения ячеек и блока 3 памяти управления, где подготавливают инфор- 30 мацию к считыванию. Другая часть адреса системы, например старшие разряды, поступают на адресные входы преобразователя 15 кода распределителя 6 и через группы бистабильных переключателей на вход блока совпадения 17. На один из входов каждого из этих блоков поступает сигнал обращения.

Если поступивший код адреса соответствует коду,. установленному на одной из групп блока 16 переключателей, та в момент поступления сигнала обращения на входе одной из 45 схем блока 17, соединенной с этой группой блока 16 переключателей,— имеет место совпадение сигналов. В результате этого на выходе блока

l7 вырабатывается сигнал совпадения, который поступает на вторую группу адресных входов блоков 2 памяти замещения и блоков 3 памяти. управления, вызы- вая считывание необходимой информации из блока 2 памяти замещения, а с выхода блока 8 — кода информации,.

55 разрешающего передачу информации через коммутатор 9 на информационную. шину ЭВМ, 4

Преимущества системы заключаются в повышении надежности и в удобстве эк с плуа та ции .

Формула изобретения

1, Запоминающая система для выборочного замещения ячеек блока памяти, содержащая электрически перепрограммируемый блок памяти замещения ячеек, первая группа адресных входов которого является группой входов младших разрядов адреса системы, коммутатор, первая группа информационных входов которого является группой информационных входов системы, вторая группа информационных входов коммутатора соединена с информационными выходами электрически перепрограммируемого блока памяти, блок распределения адресных входов старших разрядов системы, информационные входы которого являются входами адреса старших разрядов системы, а вход обращения к электрически перепрограммируемому блоку памяти замещения ячеек блока распределения является входом обращения системы, адресные выходы блока распределения соединены с адресными входами второй группы блока памяти замещения ячеек, отличающаяся тем, что, с целью повышения надежности системы, она содержит электрически перепрограммируемый блок памяти управления коммутатором, первая и вторая группы адресных входов которого соединены соответственно с адресными входами первой и второй групп электрически перепрограммируемого блока памяти замещения ячеек, а выход соединен с входом управления коммутацией.ииформационныж входов коммутатора, 2. Система по п.1, о т л и ч а ю— щ а я с я тем, что блок распределения адресных входов состоит из преобразователя кода адреса, адресные входы которого являются адресными входами блока распределения, блоков бистабильных переключателей, адресные входы которых соединены с адресными входами преобразователя кода адреса,.блоков совпадения, адресные входы которых соединены с адресными выходами, блоков бистабильных переключателей, а адресные выходы являются адресными выходами блока рас5 1508281 6 пределения, входы обращения блока дом обращения блока распределения совпадения объединены и являются вхо- адресных входов.

12