Устройство для вычисления систем булевых функций

Иллюстрации

Показать всеРеферат

Изобретение относится к автоматике и вычислительной технике и предназначено для вычисления систем булевых функций. Цель изобретения - увеличение производительности устройства. Устройство содержит N+1 сдвиговый регистр 2<SB POS="POST">1</SB>-2<SB POS="POST">N+1</SB>, N+1 блок постоянной памяти 3<SB POS="POST">1</SB>-3<SB POS="POST">N+1</SB>, N+1 регистр команд 4<SB POS="POST">1</SB>-4<SB POS="POST">N+1</SB>, N+1 регистр 5<SB POS="POST">1</SB>-5<SB POS="POST">N+1</SB>, N элементов И 6<SB POS="POST">1</SB>-6<SB POS="POST">N</SB>, элемент ИЛИ 7 и блок управления 8. В первых N обрабатывающих блоках устройства обеспечивается вычисление подфункций заданной системы булевых функций, конечный результат которой вычислится в (N+1)-м обрабатывающем блоке. 2 ил.

СОЮЗ СОВЕТСКИХ

СОЦИАЛИСТИЧЕСКИХ

РЕСПУБЛИК (51) 4 G 06 F 7/00

ОПИСАНИЕ ИЗОБРЕТЕНИЯ

Н АВТОРСКОМУ СВИДЕТЕЛЬСТВУ

ГОСУДАРСТВЕННЫЙ НОМИТЕТ

ПО ИЗОБРЕТЕНИЯМ И ОТКРЫТИЯМ

ПРИ ГННТ СССР

1 (21) 4343293/24-24 (22) 19. 11. 87 (46) 23. 09.89. Бюп. Р 35 (71) Филиал "Восход" Московского ациационного института им. Серго Орджоникидзе (72) С.Л. Беляков (53) 681;3(088.8) (56) Информационные системы. Таб личная обработка информации./Под. ред. Е.П. Балашова и В.Б. Смолова.—

Л.: Энергоатомиздат, 1985, с. 74.

Авторское свидетельство СССР и 1424005, кл. G 06 F 7/00, 1986. (54) УСТРОЙСТВО ДЛЯ ВЫЧИСЛЕНИЯ СИСTEYi БУЛЕВЫХ ФУНКЦИЙ

„„SU„„3 509865 А1

2 (57) Изобретение относится к автоматике и вычислительной технике и предназначено для вычисления систем булевых функций. Цель изобретения— увеличение производительности устройства. Устройство содержит N+1 сдвиговый регистр 2,-2 „, И+1 блок постоянной памяти 3,-3 „, N+1 регистр команд 4,-4 „„, N+1 регистр

5, — 5 ... N элементов И 6,-6, элемент ИЛИ 7 и блок управления 8. В первых N обрабатывающих блоках устройства обеспечивается вычисление подфункций заданной системы булевых функций, конечный результат которой вычислится в (N+1) -м обрабатывающем блоке. 2 ил.

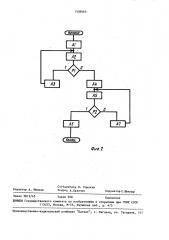

А2 — запись информации в регистр э0 команд 4, из блока 3, постоянной памяти 3;;

АЗ вЂ” запись в регистр 5;, сдвиг информации на сдвиговом регистре 2;;

А4 - обнуление регистра 5 ... начальная установка регистра команд 4 ... запись информации o сдoиговый регистр 2 „, 3 150

Изобретение относится к автоматике и вычислительной технике и предназначено для вычисления системы булевых функций.

Цель изобретения — сокращение времени, повьппение производительности устройства.

На фиг. 1 представлена схема устройства для вычисления систем булевых функций; на фиг. 2 — блоксхема алгоритма работы устройства.

Устройство для вычисления систем булевых функций содержит N групп входов 1,-1 „ аргументов устройства (где N — количество обрабатываемых групп переменных), 0+1 сдвиговый регистр 2,-2,„,, N+1 блок 3,-3 „„, постоянной памяти, N+1 регистр команд

4,-4 „„, N+1 регистр 5,-5 „, N элементов И 6„-6» элемент ИЛИ 7, блок 8 управления, вход 9 запуска устройства, вход 10 признака готовности результата блока управления, вход 11 признака готовности частичного результата блока управления, выход 12 признака конца операций устройства, пять выходов 13-17 разрешения записи блока управления, выход 18 начальной установки блока управления, выход 19 признака блокировки записи блока управления, два выхода 20 и 21 управления сбросом, блока управления, два выхода 22 и 23 управления сдвигом блока управления, выход 24 устройства.

Блок-схема алгоритма работы устройства (фиг. 2) содержит следующие обозначения условий и микроопераций:

А1 — значение признака готовности результата 10 блока управления равна нулю, обнуление регистра 5К (К = 1, N+1), начальная установка регистра команд 4К, запись информации в сдвиговый регистр 2 .(i — 1, N);

9865 4

A5 — запись информации в регистр команд 4„„из блока 3„„ постоянной памяти;

А6 — значение признака готовности результата 10 блока управления равно единице;

А7 — запись в регистр 5 щ„, сдвиг информации на сдвиговом ре-!

О гистре 2

Р1 — значение на входе 11 признака готовности частичного результата блока управления;

Р2 — значение на входе 10 призна15 ка готовности результата блока управления.

Устройство работает следующим образом.

В исходном состоянии на входы 1„20 1 аргументов устройства поданы значения исходных логических переменных. Работа устройства начинается с подачи импульса на вход 9 запуска устройства, после чего блок 8 управления начинает отработку алгоритма (фиг. 2) . Каждый i-й обрабатывающий блок реализует вычисление подфункций по соответствующим программам. В момент получения результата i-м обраба30 тывающим блоком в старшем разряде регистра 4, команд, и соответственно на выходе элемента И 6;, формируется значение лог. "0", блокирующее дальнейшую запись в регистр команд

4,. После вычисления частичного результата в первых N обрабатывающих блоках (условие Р1=0) выполняется вычисление в (N+1) обрабатым вающем блоке.

После вычисления результата (признак Р2-.1) блок 8 управления переходит в свое конечное состояние, результат вычисления передает— ся на выход 24 устройства.

Работу устройства рассмотрим на примере вычисления системы булевых функций (7,, Y2, У, Y„1от. 12 переменных, представленную в виде композиции подфункций:

1 1 39

У =Е,ЧЕ

74 =Е1, где Е, = Х7 Х Ч Х ;

z1 Х ХЗ

Е = Х11ЧХ Хь Х„;

Е = Хе(Х ЧХ„);

Е = Х„ЧХьч Х, .

6 динен с входом признака готовности частичного результата блока управления, вход запуска и выход признака конца операции которого соединены соответственно с входом запуска устройства и выходом признака конца операции устройства, о т л и ч а ю— щ е е с я тем, что, с целью повышения производительности устройства, оно содержит N сдвиговых регистров, (N+1) é регистр, (N+1)-й блок постоянной памяти и (N+1)-й регистр команд, причем второй выход разрешения записи и первый выход управления сдвигом блока управления соединены соответственно с входом управления записью и входом управления сдвига i-ro сдвигового регистра, информационный вход которого соединен с входами аргументов i-й группы устройства, выход i-ro сдвигового регистра соединен с входом старшего разряда адреса i-го блока постоянной памяти, входы остальных разрядов адреса которого соединены с выходом

i-го регистра, i-й информационный вход (N+1) ro сдвигового регистра соединен с выходом i-го регистра команд, вход управления сдвигом и вход разрешения записи (N+1)-ro сдвигового регистра соединены соответственно с вторым выходом управления сдвига и третьим выходом разрешения записи блока управления, второй выход управления сбросом и четвертый выход разрешения записи которого соединены соответственно с входом разрешения сброса и входом разрешения записи (N+1)-ro регистра, информационный вход которого соединен с выходом (N+1)-го регистра команд и выходом устройства, выход (N+1)-го блока постоянной памяти соединен с информационным входом (N+1)-го регист30

Формула изобретения

Устройство для вычисления систем булевых функций, содержащее сдвиговый регистр N блоков постоянной памяти, N регистров команд, N регистров, N элементов И (N — количество обрабатываемых групп переменных), блок управления и элемент ИЛИ, причем выход старшего разряда i-го регистра команд (i=1,N) соединен с i-м входом элемен40 та ИЛИ и первым входом i-го элемента И, второй вход которого соединен с выходом признака блокировки записи блока управления, информационный вход i-го регистра соединен с выходом 1-ro регистра команд, информационный вход которого соединен с выходом i-ro блока постоянной памяти, первый вход управления сбросом и первый выход разрешения записи бло- 50 ка управления соединены соответственно с входом разрешения сброса и входом управления записью i-го регистра, выход начальной установки блока управления соединен с входом установ1! 11 ки в 1 старшего разряда i-ro регистра команд, вход разрешения записи которого соединен с выходом i-го элемента И, выход элемента ИЛИ сое15098

Устройство имеет N--3 обрабатывающих блока для вычисления подфункций. В первый блок подаются переменные Х,, Х, Х, Х,, и вычисляются подфункции Z u Z во второй переменные

Х,, Х,. Х, Х, и вычисляется Z з в третий — переменные Х>, Хз, Х „, Х, и вычисляются Z и Z . Подфункции в первых М обрабатывающих блоках вычисляются за время Т 4 4Т„, где

҄— время обработки одной переменной (микрооперации А3 и А2) . Исходные функции в (N+1) обрабатывающем блоке вычисляются за время, не превьппающее

5Tх °

Эффект от применения устройства поясним на рассмотренном вьппе примере.

Если в прототипе требуется для вычисления системы булевых функций время

Т,= 12Т „ (так как переменных 12), то предлагаемое устройство вычисляет ту же систему функций за время Т = 4Т„+

+ 5T „ = 9Т . Эффект повышения производительности устройства будет тем 25 больше,чем меньше число подфункций будет вычисляться в устройстве и чем меньше переменных будет обрабатываться в каждом обрабатывающем блоке. ра -команд, выход старшего разряда которого соединен с входом признака готовности результата блока управления, пятый выход разрешения записи и выход начальной установки которого соединены соответственно с входом разрешения записи и входом установки в "1" старшего разряда (N+1)-го регистра команд, выход (И+1)-го сдвигового регистра соединен с входом старшего разряда адреса (N+1)-ro блока постоянной памяти, входы остальных разрядов адреса которого соединены с выходом (N+1)-го регистра.

Составитель В. Сорокин

Техред А.Кравчук.

Редактор А. Шандор

Корректор С. Шекмар

Заказ 5812/45 Тираж 668 Подписное

ЦНИИПИ Государственного комитета по изобретениям и открытиям при ГКНТ СССР

113035, Москва, Ж-35, Раушская наб., д. 4/5

Производственно-издательский комбинат "Патент", г. Ужгород, ул. Гагарина, 101