Вычислительное устройство

Иллюстрации

Показать всеРеферат

Изобретение относится к цифровой вычислительной технике и может быть использовано при разработке высокопроизводительных устройств обработки потоков дискретной информации. Цель изобретения - упрощение устройства. Вычислительное устройство содержит матрицу вычислительных ячеек 1 размерностью M<SP POS="POST">.</SP>N, где M, N - разрядности соответственно множителя и множимого, параллельный сумматор 2, M групп по J узлов 3 памяти (J = 1,...,M, где J - номер группы). Каждая вычислительная ячейка 1 содержит элементы И 4 - 9, элементы ИЛИ 10, 11, элемент НЕ 12, два элемента ИСКЛЮЧАЮЩЕЕ ИЛИ 13, узел 14 памяти. Каждый узел памяти 3, 14 содержит элемент задержки, элемент НЕ, элементы И, элемент ИЛИ. 4 ил.

СОЮЗ СОВЕТСКИХ

СОЦИАЛИСТИЧЕСКИХ

РЕСПУБЛИК

ОПИСАНИЕ ИЗОБРЕТЕНИЯ

ГОСУДАРСТВЕННЫЙ КОМИТЕТ

ПО ИЗОБРЕТЕНИЯМ И OTHPblTHRM

ПРИ ГКНТ СССР

H АВТОРСКОМУ(СВИДЕТЕЛЬСТВУ

1 (21) 4322957/24-24 (22) 30 ° 10,87 (46) 23.09,89. Бюл. 35 (71) Ленинградский электротехнический институт им. В.И.Ульянова (Ленина) (72) О. Г.Кокаев, В. С.Кисленко (Sv)

Давид Амехо (NG) и Т.И.Талышинская (sU) (53) 687.325(088.8) (56) Авторское свидетельство СССР и 81 7705, кл. G 06 F 7/52, 1979.

Авторское свидетельство СССР

Н 1117635, кл. G 06 F 7/52, 1983. (54) ВЫЧИСЛИТЕЛЬНОЕ УСТРОЙСТВО (57) Изобретение относится к цифровой вычислительной технике и может быть

„„Я0„„1509872 А1 11 4 G 06 F 7/38

2 использовано при разработке высокопроизводительных устройств обработки потоков дискретной информации. Цель изобретения — упрощение устройства.

Вычислительное устройство содержит матрицу вычислительных ячеек размерностью m.n, где ш, и — разрядности соответственно множителя и множимого, параллельный сумматор, m групп по j узлов памяти (j -- 1, ..., m, где j номер группы}„ Каждая вычислительная ячейка содержит элементы И 4-9, элементы ИЛИ 10 и 11, элемент НЕ 12, два элемента ИСКЛЮЧАЮЩЕЕ ИЛИ 13, узел

14 памяти. Каждый узел памяти содержит элемент задержки, элемент НЕ, элементы И и элемент ИЛИ. 4 ил.

1509872 4

d (t + 1) =dZ+dd (t) +d (t)Z;

b = Ъ;

Z =Z где S(t + 1) и S(t) - значения выхода 25 соответственно в последующий и предыдущий моменты времени; с (t + 1) и c(t) — значения выхода 26 соответственно в последующий и предыдущий моменты времени;

d (t + 1) и d (t) — значения выхода 27 соответственно в последующий и предыдущий моменты времени; с

b и Ъ вЂ” значения выхода 28 вычислительной ячейки 1;

Е и Š— соответственно

/ значения входа 29 и выхода

30 30 вычислительной ячейки 1.

Узел 3 памяти описывается системой логических уравнений-:

Y(t + 1) = yZ + yY(t) + У()Е (4) где Y(t+1)

I и Y(t) — значения выхода 3 i узла

3 памяти соответственно в следующий .и предыдущий моменты времени, у — значение входа 32 узла 3 памяти;

Z Р и Z р — соответственно значения

I входа 33 и выхода 34 узла 3 памяти. Матричный умножитель работает в конвейерном режиме следующим образом.

Изобретение относится к цифровой вычислительной технике и предназначено для использования в универсальных и специализированных цифровых вычислительных устройствах .

Целью изобретения является упрощение устройства.

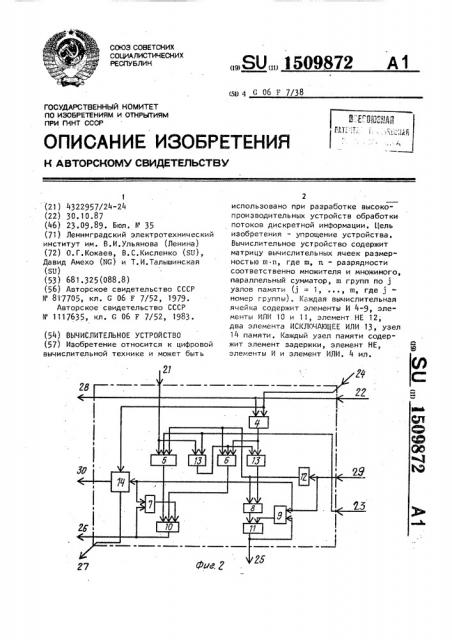

На фиг.1 представлена функциональная схема вычислительного устройства 10 для m п = 4; на фиг.2 - функциональная схема вычислительной ячейки; на фиг.3 - функциональная схема ячейки памяти ; на фиг.4 - временная диаграмма подачи управляющих сигналов.

Вычислительное устройство содержит. матрицу вычислительных ячеек 1 размерностью m х и,- где m, п - разрядности соответственно множителя и множимого, параллельный сумматор 2, m групп по j узлов 3 памяти (j = 1, ..., m; где j — номер группы), каждая вычислительная ячейка 1 содержит элементы И 4-9, элементы ИЛИ 10 и 11, элемент HE 12, два элемента ИСКЛЮЧА25

ЮЩЕЕ ИЛИ 13, узел 14 памяти, каждый узел памяти 3, 14 содержит элемент 15 задержки, элемент НЕ 16, элементы И

17-19 и элемент ИЛИ 20.

Матричный умножитель реализует функцию:

S = А + BD + С, (1)

Для вычисления произведения двух чисел В и D слагаемые А и С должны быть нулевыми. Реализация умножителем функции вида (1) расширяет его функциональные возможности.

Каждая вычислительная ячейка 1 умножителя осуществляет такую же 40 арифметическую функцию как весь умножитель, только для одноразрядных двоичных чисел, а, Ь, с, d:

S + с = а + bd + с„(2) где а, Ь, с, d — сигналы на входах

21-24 вычислительной ячейки 1, S, с — сигналы на выходах

25 и 26 вычислительной ячейки 1.

В формуле (2) S и с складывается с учетом веса.

Вычислительная ячейка 1 описывается следующей системой логических. уравнений:

S(t + 1) - ((а 9 с) ® (Ьй)) Z +

+ S(t)Z с (t + 1) acZ + bd(a Q+ с)Z +

+ с (й)Ер (3) В исходном состоянии на управляющих входах 35,-35< умножителя установлен сигнал "0". Процесс вычисления начинается с подачи на входы

36,-36, 37,-37, 38,-38 39,-39 з первых сомножителей В и слагаемых А, С. В течение времени Т (фиг.4) вычисление происходит в вычислительных ячейках 1 первого ряда ° е

5 1

В момент времени Т, когда вычисления в первом ряду закончились, на управляющий вход 35, подается сигнал

"1", который осуществляет запоминани информации, установившейся на выходах вычислительных ячеек 1 первого ряда . При этом на выходах 27 вычислительных ячеек 1 первого ряда запоминается множимое D Сигнал "1" на входе 35 запрещает также отработку вычислительными ячейками 1 первого ряда сигналов, которые будут появляться на их входах 36,-36, 37,37, 39,-39 . Единица на управляющем входе 35 сохраняется в течение времени Т (Фиг.4), что обеспечивает проведение вычислений на втором ряду вычислительных ячеек 1 и запоминание информации в узле 3 памяти второго ряда .

Время, пока в первом ряду вычислительных ячеек 1 не производятся вы числения, используют для подачи на входы 36,-36„37о 37з» 38 в 3 з» 39о

39 нового множимого D, младшего разряда множителя В и новых слагаемыхА и С

Подача новой информации на вычислительные ячейки 1 первого ряда проводится в промежуток времени (фиг.4). По окончании вычисления в первом ряду вычислительных ячеек 1 и запоминания в.узле 3 памяти ряда, в момент времени 2Т, после начала вычислений на управляющий вход 35 подается сигнал "1н» который осуществляет запоминание информации, установившейся на выходах вычислительных ячеек 1 второго ряда и на выходе узла 3 памяти второго ряда, а также запрещает отработку вычислительными ячейками 1 второго ряда и узлом 3 .памяти первого ряда сигналов, которые будут поступать на их входы.

С момента времени 2ТР вычисление. продолжается в третьем ряду вычислительных ячеек 1 и происходит работа узлов 3 памяти третьего ряда.

Поскольку первый ряд вычислительных ячеек 1 готов к работе, на его управляющий вход 35, в момент времени (Т + Т1,) подается сигнал "0", который разрешает обработку вновь поступившей информации вычислитель" ными ячейками 1 первого ряда. Сигнал

"0" на управляющем входе 35, держится в течение времени (° + Т ), что обеспечивает правильное вычисление.

509872

Так как вычислительные ячейки 1 второго ряда не производят вычислений, то промежуток времени с (2Т + »,) до (2Т р + Т + с) используется для подачи разряда Ь, второго множителя на вход 37, матричного умножителя, подготавливая его тем самым к новому вычислению.

Аналогично конвейерный процесс вы" числения продолжается дальше. По мере окончания вычисления в i-й ступени (i = 1, 2, ..., 5) матричного умножителя в нее вводится новая информация с периодом

Тум Tp+ T„+ » (5) при этом Z в течение времени Т „ находится в "1", а в течение времени (Т + О) - в "0". Подача новой информации на i-ю ступень с информационных входов умножителя, подсоединенных к

i-й ступени, разрешается в промежуток времени, начиная с момента времени 9, после установления Z B » !" и до истечения времени, после установления

Z, B "0". На информационных выходах

40 -40 с периодом Т „„„будут появляться результаты вычислений. Узлы 3 памяти обеспечивают синхронизацию появления и старших и m младших разрядов результата на информационных выходах умножителя.

Формула изобретения

Вычислительное устройство, содер" жащее матрицу вычислительных ячеек .. размерностью m х и (где m, п - разрядности соответственно множителя и множимого), каждая вычислительная ячейка содержит шесть элементов И, элемент НЕ, узел памяти, тп групп по

j узлов памяти (j = 1, ..., m, где

j — номер группы), причем каждый узел памяти содержит три элемента И, элемент ИЛИ, элемент НЕ, элемент задержки, причем первый вход первого элемента И узла памяти соединен с первым входом второго элемента И, второй вход которого соединен с первым входом третьего элемента И и выходом элемента ИЛИ, первый, второй и третий входы которого соединены соответственно с выходами первого, второго и третьего элементов И узла памяти, второй вход первого элемента И которого соединен с выходом элемента HE узла памяти, входы разрядов первого слагаемого устройства соеди1509872 нены соответственно с первым входом первых элементов И вычислительных ячеек первой строки матрицы, входы разрядов второго слагаемого устройства соединены соответственно с вторым входом первых элементов И вычислительных ячеек первой строки матрицы, входы разрядов множителя соединены соответственно с первым входом вторых элементов И вычислительных ячеек первого столбца матрицы, входы разрядов множимого устройства соединены соответственно с вторым входом вторых элементов И вычислительных ячеек первой строки матрицы и первым входом первых элементов И узлов памяти вычислительных ячеек первой строки матрицы, вторые входы третьих элементов И каждого узла памяти вы- 20 числительных ячеек i-й строки матрицы (i = 1, ..., m) соединены с i-м тактовым входом устройства и входом элемента задержки узла памяти, выход которого соединен с входом элемента 25

НЕ узла памяти, третий вход первого элемента И каждой вычислительной ячейки матрицы соединен с первым входом третьего и четвертого, элементов

И и выходом элемента НЕ вычислительной ячейки матрицы, выходы первого, третьего и пятого элементов И вычислительной ячейки матрицы соединены соответственно с первым, вторым и третьим входами первого элемента ИЛИ вычислительной ячейки матрицы, выход которого соединен с первым входом пятого элемента И вычислительной ячейки матрицы, выходы четвертого и шестого элементов И которой соединены соответственно с первым и вторым входами второго элемента ИЛИ вычислительной ячейки матрицы, выход кото" рого соединен с первым входом шестого элемента И вычислительной ячейки матрицы, первый вход первых элементов И вычислительных ячеек матрицы

n-ro столбца S-й строки соединены с шиной логического нуля устройства (S = 2, ..., m), первый выход первого элемента И вычислительной ячейки S-й строки r-го столбца (r =

= 1, ..., n-1) матрицы соединен с выходом второго элемента ИЛИ вычислительных ячеек (S-I)-и строки и (г+1)-ro столбца матрицы, выход первого элемента ИЛИ вычислительной ячейки i-й строки и 1-го столбца (1 = 1, ..., n) матрицы соединен с вторым входом первого элемента И вычислительной ячейки (i+1)-й строки и

1-ro столбца матрицы, выход элемента ИЛИ узла памяти вычислительной ячейки К-й строки (К = 1, ..., m-1) и 1- го столбца матрицы соединен с вторым входом второго элемента И вычислительной ячейки (К+1)-й строки и 1-го столбца матрицы, выходы первых и вторых элементов ИЛИ вычислительных ячеек m-й строки q-го столбца (q = r, ..., m) и выход первого элемента ИЛИ вычислительной ячейки первого столбца m-й строки матрицы соединены с соответствующими весовыми входами параллельного сумматора, и выходов которого соединены с выходами и старших разрядов устройства, m выходов младших разрядов устройства соединены соответственно с выходами элементов ИЛИ m-й группы узлов памяти, вторые входы третьего элемента И которой соединены с (m+1)-м тактирующим входом устройства, первые входы первого элемента И (i-1)-х узлов памяти j-й группы соединены соответственно с выходами элементов ИЛИ (j-1)-й группы, первый вход первого элемента И j --го узла памяти j --й "групрв соединен с выходом второго элемента ИЛИ вычислительной ячейки 1-й строки первого столбца матрицы вычислительных ячеек, второй вход пятого элемента И вычислительной ячейки i-й строки матрицы соединен с вторым входом шестого элемента И и с i-м тактовым входом устройства, первые входы вторых элементов И вычислительных ячеек i-x строк матрицы соединены с соответствующими разрядными входами множителя, о т л и ч аю щ е е с я тем, что, с целью упрощения устройства, в каждую вычислительную ячейку устройства дополнительно введены первый и второй элементы ИСКЛОЧАЮщЕЕ ИЛИ, причем первый и второй входы первого элемента И вычислительной ячейки матрицы соединены соответственно с первым и вторым входами первого элемента ИСКЗВЧРЮЦЕЕ

ИЛИ вычислительной ячейки, выход которого соединен с первым входом второго элемента ИСКЛОЧАЮЩЕЕ ИЛИ и вторым входом третьего элемента И вычислительной ячейки матрицы, выход второго элемента И вычислительной ячейки матрицы соединен с третьим входом третьего элемента И вычислительной

1509 7>

10 ячейки и вторым входом второго элемента ИСКЛОЧЮЩЕЕ ИЛИ вычислительной ячейки, выход которого соединен с вторым входом четвертого элемента И вычислительной ячейки, вход элемента

HE вычислительной ячейки. соединен с вторым входом шестого элемента И вычислительной ячейки матрицы.

36з 86Z Ç6 И

1509872

Составитель IP. Варакин

Техред А. Кравчук Корректор О. Кравцова

Редактор А.Шандор

Заказ 5812/45 Тираж 668 Подписное

ВНИИПИ Государственного комитета по изобретениям и открытиям при ГКНТ СССР

113035, Москва, Ж-35, Раувская наб., д. 4/5

Производственно-издательский комбинат "Патент", r. Ужгород, ул. Гагарина,1О1