Одноразрядный сумматор

Иллюстрации

Показать всеРеферат

Изобретение относится к вычислительной технике и может быть использовано в процессорах ЭВМ. Цель изобретения - упрощение сумматора. Одноразрядный сумматор содержит МОП- транзисторы 1-6 N-типа и 7-12 P - типа. Истоки транзисторов 1,5 и 2 соединены со входами первого и второго слагаемых и затворами транзисторов 2, 11 и 1, 7 стоки транзисторов 1, 2, 7 - с истоком транзистора 3 и затворами транзисторов 4, 5, 8, 9 затворы транзисторов 3, 10 и исток транзистора 4 - со входом переноса стоки транзисторов 3, 4, 8 - с выходом суммы и затворами транзисторов 6, 12 стоки 5, 6, 9 - с выходом переноса истоки транзисторов 10, 11, 12 - с шиной питания, а их стоки - с истоками транзисторов 8, 7 и 9. В сумматор введен резистор 13, через который исток транзистора 6 соединен со стоком транзистора 7. 1 ил.

СОЮЗ СОВЕТСНИХ

СОЦИАЛИСТИЧЕСНИХ

РЕСПУБЛИН

А1 (51)4 G 06 F 7/50

ГОСУДАРСТВЕННЫЙ НОМИТЕТ

ПО ИЗОБРЕТЕНИЯМ И ОТНРЫТИЯМ

ПРИ ГКНТ СССР

1 (21) 4274164/24-24 (22) 01,07.87 (46) 23.09.89. Бюл. № 35 (71) Ленинградский электротехнический институт им. В.И.Ульянова (Ленина) (72) В.И.Варшавский, Н.А.Голдин, А.Ю.Кондратьев и Б.С.Цирлин (53) 681.325.5(088.8) (56) Авторское свидетельство СССР № 1100620, кл. G 06 F 7/50,1983, Авторское свидетельство СССР

¹ 1439578. кл. С 06 Р 7/50, 27.05.87. (54) ОДНОРАЗРЯДНЫЙ СУИИАТОР (57) Изобретение относится к вычислительной технике и может быть использовано в процессорах ЭВИ. Цель изобретения — упрощение сумматора. Одноразрядный сумматор содержит МОП-тран„.Я0„„1509874

2 зисторы 1-6 п-типа и 7-12 р-типа. Истоки транзисторов 1,5 и 2 соединены с входами первого и второго слагаемых и затворами транзисторов 2,11 и

1, 7; стоки транзисторов 1, 2, 7 — с истоком транзистора 3 и затворами транзисторов 4,5,8,9; затворы транзисторов 3,10 и исток транзистора 4 — со входом переноса; стоки транзисторов

3,4,8 — с выходом суммы и затворами транзисторов 6,12; стоки 5,6,9 — с выходом переноса; истоки транзисторов 10, 11, 12 — с шиной питания, а их стоки — с истоками транзисторов

8,7 и 9. В сумматор введен резистор

13, через который исток транзистора

6 соединен со стоком транзистора 7.

1 ил.

74 4

3 15098

Изобретение относится к вычислительной технике и может быть использовано в процессорах ЭВМ.

Цель изобретения — упрощение сум5 матора.

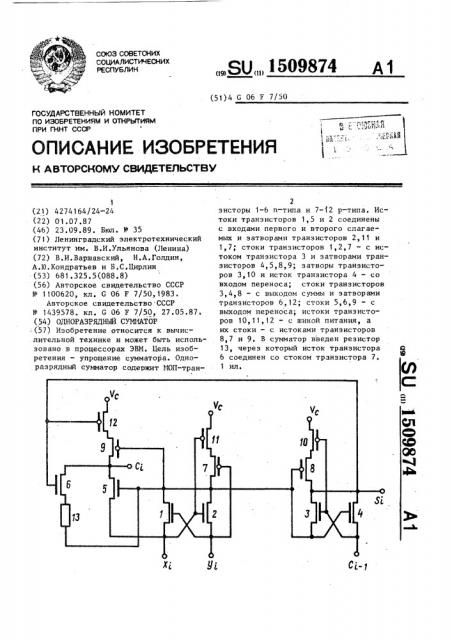

На чертеже представлена схема одноразрядного сумматора.

Одноразрядный сумматор содержит

МОИ-транзисторы 1-6 п-типа, 7-12 р-ти-10 па, резистор 13, выходы S; и С; суммы и переноса соответственно и входы

Х;, У и С 1, первого и второго слагаемых и переноса соответстсвенно.

Сумматор работает следующим обра- l5 зом.

Если на входе одного их слагаемых имеется единичное значение, а на входе другого — нулевое значение (Х, =1, У; О или Х; =1, У; 0), один из тран-20 зисторов 1 или 2 будет открыт и на их стоках будет низкий потенциал, поскольку один из транзисторов 7 или 11 будет при этом закрыт.

Если единичное значение имеется Hà25 входах обоих слагаемых (Х; = У; =1), то на стоках транзисторов 1 и 2 будет высокий потенциал, хотя оба транзистора 7 и 11 будут при этом закрыты.

Если же на входах обоих слагаемых имеется нулевое значение (Х, = Y; =О), то оба транзистора 1 и 2 будут закрыты и на их стоках будет высокий потенциал, так как транзисторы 7 и l1 при этом будут открыты. 35

Таким образом, потенциал на стоках транзисторов 1,2 и 9 соответствует логической функции ЭКВИВАЛЕНТНОСТЬ обоих слагаемых, т.е. Х . = Y

1 1

Аналогично, транзисторы 3,4 и 8,10 40 реализуют логическую функцию ЭКВИВАЛЕНТНОСТЬ для значений, поступающих на затворы этих транзисторов., т.е. на выходе S,. реализуется логическая функция 45

8;= Х;®У;ас;, °

При нулевом значейии на входах обоих слагаемых (Х; = Y 0) на затворах транзисторов 5 и 12 имеется высокий потенциал, и транзистор 5 открыт, а транзистор 12 закрыт, при этом на стоках транзисторов 5 и 6 будет низ-, кий потенциал, т,е. на выходе С; — нулевое значение (С; =О).

Если на входе одного из слагаемых имеется единичное значение, а. на входе другого слагаемого — нулевое значение (Х:, 1, У; 0 или Х,. О, У; 1), то на затворах транзисторов 5 и 12 будет низкий потенциал, и транзистор

l2 будет открыт, а транзистор 5 закрыт.Если при этом на выходе суммы имеется нулевое значение, что возможно только при единичном значении на входе переноса (С; =1), то закрыт и транзистор 6, а транзистор 9 открыт, и на стоках транзисторов 5 и 6 будет высокий потенциал, т.е. на выходе

С, †. единичное значение (С, =1). Если же на выходе суммы имеется единичное значение, что возможно при нулевом значении на входе переноса (С, =0) то низкий потенциал со стоков транзисторов 1 и 2 через резистор

13 и открытый транзистор 6 поступит на стоки транзисторов 5 и 6, а транзистор 9 будет при этом закрыт, следовательно, на стоках транзисторов

5 и 6 будет низкий потенциал, т.е. на выходе С вЂ” нулевое значение (С, =

О).

При единичном значении на входах обоих слагаемых (Х; = У,.=l) на стоках транзисторов 5 и 6 будет высокий потенциал, хотя транзистор 9 будет при этом закрыт, т.е. на выходе С; — единичное значение (С =1).

Таким образом,на выходе переноса

С, реализуется логическая функция, (X,.a+ +Y,.)

При нулевом значении на входах обоих слагаемых (Х, = Y; =О) и при единичном значении на выходе суммы, что возможно только при единичном значении на входе переноса (С . =1)

Э низкий потенциал имеется на стоке транзисторов 6,т.е. на выходе переноса С;, а высокий потенциал — на стоке транзистора 7, однако ток в этих открытых транзисторах ограничивается резистором l3.

Формула изобретения

Одноразрядный сумматор, содержащий шесть МОП-транзисторов п-типа и шесть МОП-транзисторов р-типа, причем истоки первого и второго транзисторов и-типа соединены с входами первого и второго слагаемых сумматора и затворами вторых и первых транзисторов и- и р-типов, а их стоки — с истоком третьего и затворами четвертого и пятого транзисторов и-типа и стоком первого и затворами третьего и четвертого транзисторов р-типа, затвор третьего транзистора и-типа соединен с истоком

Составитель М.Есенина

Техред А. Кравчук Корректор М. Васильева

Редактор А.Шандор

Заказ 5812/45 Тираж 668 Подписное

ВНИИПИ Государственного комитета по изобретениям и открытиям при ГКНТ СССР

113035, Москва, Ж-35, Раушская наб., д. 4/5

Производственно-издательский комбинат "Патент", г.ужгород, ул. Гагарина, 101

5 1509874

6 четвертого транзистора п-типа, эатво- типов соединены с выходом суммы сумма" ром пятого транзистора р-типа и вхо- .тора, истоки-второго, пятого и шевтодом переноса сумматора, а стоки тре- го транзисторов р-типа соединены с тьих транзисторов р и и-типов со

5 шиной питания сумматора а их стокиФ стоками четвертого транзистора п-ти- с истоками соответственно первого, па и выходом суммы сумматора, сток третьего и четвертого транзисторов пятого транзистора и-типа соединен с, р-типа, отличающийся тем, входом одного слагаемого сумматора, а что, с целью упрощения сумматора, он исток — с истоками четвертого транзис-1ð содержит резистор, через который истора р-типа и шестого транзистора ток шестого транзистора и-тяпа сои-типа и выходом переноса сумматора, едннен со стоком первого транзистора затворы шестых транзисторов и- и р- р-типа.