Устройство сопряжения процессора с внешними устройствами

Иллюстрации

Показать всеРеферат

Изобретение относится к вычислительной технике , в частности, к устройствам связи с объектами управления вычислительных комплексов, и предназначено для приема сигналов от двухпозиционных датчиков и ввода информации об их состоянии в ЭВМ с формированием инициативного сигнала запроса на прерывание текущей программы центрального процессора. Цель изобретения - повышение пропускной способности устройства за счет работы как в режиме опроса, так и в режиме прерывания. Устройство содержит регистр, два триггера, блок элементов ИСКЛЮЧАЮЩЕЕ ИЛИ, блок элементов И, шифратор адреса, блок формирования ответного сигнала, формирователь импульса, элемент задержки, три элемента И и четыре элемента ИЛИ. 1 з.п. ф-лы, 3 ил.

СОЮЗ СОВЕТСКИХ

СОЦИАЛИСТИЧЕСКИХ

РЕСПУБЛИК (51)4 C 06 F 9/46 13/32

1 1РИ,ГКНТ СССР

ОПИСАНИЕ ИЗОБРЕТЕНИЯ

К АВТОРСКОМУ СВИДЕТЕЛЬСТВУ

ГОСУДАРСТВЕННЫЙ КОМИТЕТ

IlO ИЗОБРЕТЕНИЯМ И (ЛНРЫТИЯМ

1 (21) 4391584/24-24 (22) 21,12,87 (46) 23.09.89, Бюл, У 35 (72) В,А.Чернокрылов, В.Т.Старцев, В,В.Куконега, B Г,Яковлев иЮ.В.Кудряшов (53) 281.3(088.8) (56) Соботка 3., Стары Я. Микропроцессорные системы, — М,: Энергоиздат, 1981, с. 156.

Модуль ввода дискретных сигналов

СМ 1800.9203, Техническое описание и и инструкции по эксплуатации„З;049.009

ТО. (54) УСТРОЙСТВО СОПРЯЖЕНИЯ ПРОЦЕССОРА

С ВНЕШНИМИ УСТРОЙСТВАМИ (57) Изобретение. относится к вычислительной технике, в частности к устройИзобретение относится к вычислительной технике, в частности к устройствам связи с объектами управления вычислительных комплексов, и предназначено для приема сигналов от двухпозиционных датчиков и ввода информации о6 их состоянии в 3ВМ с формированием инициативного сигнала запроса на прерывание текущей программы центрального процессора.

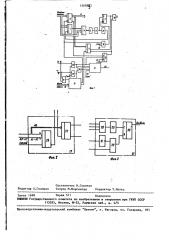

Цель изобретения - повьппение пропускной способности устройства за счет работы как в режиме опроса, так и в режиме прерывания, На фиг,l представлена структурная схема устройства; на фиг.2 — схема шифратора адреса; на фиг.3 — схема блока формирования ответного сигнала.

Я0 р (19} (II

2 ствам связи с объектами управления вы- числительных комплексов, и предназначено для приема сигналов от двухпоэиционных датчиков и ввода информации об их состоянии в 3ВМ с формированием инициативного сигнала запроса на прерывание текущей программы центрального процессора. Цель изобретения, — по-. вьппение пропускной способности устройства эа счет работы как в режиме опроса, так и в режиме прерывания. Устройство содержит регистр два триггера, блок: элементов ИСКЛЮЧАЮЩЕЕ ИЛИ, блок элементов И, шифратор адреса, блок формирования ответного сигнала, формирователь импульса, элемент задержки, три элемента И и четыре элемента ИЛИ..

I з.п. ф-лы, 3 ил.

Устройство содержит регистр 1, шин ный формирователь 2, запросный вход

3, устройство для подключения к выходу внешнего устройства, блок элементов ИСКЛ1ОЧАЮШЕЕ ИЛИ 4,. элемент ИЛИ 5, формирователь 6 импульса, триггер 7,, элемент 8 задержки, блок элементов

И 9, элемент И 10, выход- 11 для подключения к входу запроса .прерывания процессора, триггер 12, вход-выход

l3 для подключения к шине данных процессора, элемент ИЛИ 14, входы записи 15 и чтения 16 для подключения к выходам процессора, шифратор 17 адреса, вход 18 для подключения к адрес- ному выходу процессора, элемент ИЛИ

19, вход 20 сброса, блок 21 формирования ответного сигнала, элементы

1$9%%9И 22 ° 23 ° элемент ИЛИ 24, выход 25

6твета для подключения к входу процессора, неполные дешнфраторы 26 и 27 элемент ИЛИ 28, формирователь 29 импульса, триггер 30, элемент НЕ 31 и элемент ИЛИ 32.

Устройство работает следующим образом.

Перед началом работы (при включении энергопитания ЭВМ или нажатии кнопки "Сброс" ) устройство устанавливаегся в исходное состояние сигналом

"Сброс" по входу 20 что приводит к обнулению; триггеров 12 и 7 и означает состояние триггера .12 "Запрещено" и отсутствие изменений состояний на входах устройства. При обращении центрального процессора ЭВМ к устройству и режиме Запись" на инФормационном 2р входе-выходе 13 устанавливается информация, предназначенная для передачи в устройство: на входе 18 адреса комбинация сигналов, соответствующая коду базового адреса устройства и раз-25 решающая работу шинного формирователя 2, управляющего триггерами 12 и 7, задающая направление передачи информации по информационному входу-выходу 13 от системного интерфейса ЭВМ 3п через шинный формирователь 2 в триггер 12. На выходе шифратора 17 адреса при наличии на входе 15 команды

"Запись" вырабатывается сигнал, поступающий через. дешифратор 26 (Фиг.2) 35 и блок 21 (фиг ° 3) на выход 25 "Ответ" устройства, означающий, что на входевыходе 13 подготовлена информация для передачи и записи в триггер 12. Запись в триггер.12 логической "1" переводит 40 его в состояние "Разрешено", а логического "0" в состояние "Запрещено".

Таким образом, осуществляется программное управление триггером 12, 45

При обращении процессора к уст11 !Ф ройству ввода по команде Чтение на входе 16 на входе 18 адреса устанав.ливается комбинация сигналов, соот.-"ветствующая коду базового адреса на ииниях А0 и А1 (фиг,2), комбинация

- - сигналов, соответствующая коду разре--..мения работы шинного формирователя 2 жли блока элементов И, задающая на:.правление лередачи ящформации по входу-выходу 13 в системный интерфейс

1! 11

ЭВМ при наличии команды Чтение на входе 16, при этом на выходе шифратора 17 адреса вырабатывается сигнал, поступающий через блок 21 на выход 25 устройства, означающий,,что на шине данных подготовлена информация для передачи в системный интерфейс. Шинный формирователь 2 по команде "Чтение" передает информацию о .сигналах, 3 запроса, а блок элементов И 9 — о состоянии триггеров 7 и 12.

Рассмотрим работу устройства при формировании сигнала запроса на прерывание.

В исходном состоянии оба входа всех логических элементов ИСКЛЮЧАЮЩЕЕ ИЛИ

4 имеют одинаковый логический уровень, так как в регистре 1 записано текущее состояние входных сигналов 3.

При изменении состояния i-го входа 3 на противоположное входы i-го логического элемента ИСКЛЮЧАЮЩЕЕ ИЛИ 4 имеют различные логические уровни и на выходе образуется сигнал несравнения, который через элемент ИЛИ 5 воздействует на вход формирователя 6 импульса, в результате чего на выходе формирователя 6 импульса вырабатывается импульс, который переводит триггер 7 в единичное состояние, и через элемент 8 задержки поступает на синхровход регистра I в результате чего в

i-й разряд. регистра 1 заносится новое. состояние i-го входа входного сигнала 3, что приводит i-й логический элемент ИСКЛЮЧАЮЩЕЕ ИЛ11 4 в исходное состояние. Таким образом, при условии нахождения триггера 12 в состоянии

"PaspeøåHo оба входа элемента И 10 имеют уровень логической "1", что ведет к появлению сигнала запроса на-прерывание на выходе 11 устройства.

При выполнении центральным процессором ЭВМ операции "Чтение" иэ шинного формирователя 2 происходит определение, по какому именно входу пришел сигнал с входа 3 сигналов, и автоматически осуществляется сброс триггера

7 в нулевое состояние, что, в свою очередь, снимает сигнал запроса на прерывание с выхода 11 системного ин терфейса ЭВМ, Таким образом, устройство может работать в двух режимах: как устройство ввода дискретной информации, onрос которого производится в любое время по инициативе центрального процессора, и в режиме инициативной ра-. боты устройства, что позволяет по сигналам от двухпозиционных датчиков, соответственно выбрать нужную под1

35oP LS ! 5119883 6 программу обработки полученного пре-.— рывания, т,е, обеспечить мультипрограммный режим работы и управления несколькими независимыми технологическими объектами от одной ЗВМ.

Формула изобретения

1, Устройство сопряжения. процессора с внешними устройствами, содержащее .шинный формирователь, шифратор адреса и блок формирования ответного сигнала, вьгход которого является выходом устройства,для .подключения к входу ответа процессора, информационный вход шифратора адреса является входом устройства для подключения к адресным входам процессора, информационный вход-выход шинного формирова- 20 теля является входом-выходом устройства для подключения к шине данных процессора, запросный вход устройства для подключения к выходу внешнего устройства соединен с информацион- 25 ным входом шинного формирователя, о тл и ч а ю щ е е с я тем,.что, с целью повышения пропускной способности устройства за счет работы как в режиме опроса, так и в режиме прерывания. оно содержит регистр, б.",.х элементов

ИСКЛЮЧАЮ1ЕЕ ИЛИ,. четыре элемента ИЛИ, формирователь мпульса, элемент задержки. д"..a триггера, три элемента И и блок элементов И, выход которого со- 35 единен с входом-выходом устройства для подключения к шине данных процессора, запросный вход устройства для подключения к выходу внешнего устройства соединен с информацион. — 4g ным входом регистра и первым входом блока элементов ИСКЛМЧАЮП1ЕЕ ИЛИ, второй вход.и выход которога соединены соответственно с выходом регистра и входом первого элемента ИЛИ, выход которого через формирователь импульса соединен с входом элемента задержки и тактовым входом первого триггера, выход которого соединен с первым входом блока элементов И и 511 .первым входом первого элемента И, выход которого является выходом устройства для подключения к входу запроса прерывания процессора, вход сброса которого соединен с входом сброса 55 второго триггера, первым входом бло-ка формирования ответного сигнала и первым входом второго элемента ИЛИ, выход которого соединен с входом сброса первого триггера, вход устройства для подключения к выходу записи про цессора соединен с первыми входами третьего элемента ИЛИ и второго элемента И, выход которого соединен с первым входом четвертого элемента

ИЛИ, вторым входом блока формирования ответного сигнала н тактовьи входом второго триггера, выход которого соединен с вторым входом первого элемента И и вторым входом блока элементов

И, третий вход которого соединен с третьим входом блока формирования ответного сигнала и первым выходом шифратора адреса, вход устройства для подключения к выходу чтения процессора соединен с вторым входом третьего элемента ИЛИ и nepabme входом третьего элемента И, выход которого соединен с первым стробирующим входом шифратора адреса и вторым входом четвертого элемента ИЛИ, выход которого соединен с четвертым входом блока формирования ответного сигнала, пятый вход которого соединен с вторым входом второго элемента ИЛИ, управляющим входом шинного формирователя и вторым выходом шифратора адреса, второй стробирующий вход и третий выход которого соедчнены соответственно с выходом третьего элемента ИЛИ и вторыми входами второго и третьего элементов И, выход элемента задержки соединен с входом записи регистра, выход шинного формирователя соединен с информационным входом второго триггера.

2. Устройство по и. 1, о т л и— ч а ю щ е е с я тем, что,блок формирования ответного сигнала содержит. триггер, два элемента ИЛИ, формирователь импульса и элемент НЕ, выход которого соединен с первым входом первого элемента ИЛИ, второй вход и вы-.. ход которого соединены соответственно с первым входом блока формирования ответного сигнала и входом сброса триггера, выход которого является выходом блока формирования ответного сигнала, второй и третий входы которого соединены соответственно с первым и вторым входами второго элемента

ИЛИ, выход которого через формирователь импульса соединен с тактовым входом триггера, четвертый и пятый входы блока формирования ответного сигнала соединены соответственно с входом элемента НЕ и третьим входом второго элемента ИЛИ, 15098I33

Составитель М.Сорочан

Редактор О.Головач Техред М.Моргентал Корректор Т.Малец

Заказ l698 Тираа 57! Подписное

ВНИИПИ ГосУдарственного комитета по изобретениям и открытиям при ГЕНТ СССР

113035, Москва, %-35, Раувская наб. ° д. 4/5

Производственно-издательский комбинат "Патент", г. Ужгород, ул. Гагарина, 101