Устройство для распределения заданий процессорам

Иллюстрации

Показать всеРеферат

Изобретение относится к вычислительной технике и может быть использовано в многопроцессорных системах. Цель изобретения - повышение быстродействия. Устройство содержит блок регистров, блок элементов ИЛИ, два блока элементов И, три элемента ИЛИ элемент И, каждый каналдва элемента И и элемент ИЛИ, блок элементов И (кроме первого канала). В устройстве происходит распараллеливание процесса приема очередной задачи и подготовки устройства к приему следующей задачи. 2 ил.

СОЮЗ СОВЕТСКИХ.

СОЦИАЛИСТИЧЕСКИХ

РЕСПУБЛИК (50 4 С 06 F 9/46

; «111

1 ..-с

ОПИСАНИЕ ИЗОБРЕТЕНИЯ

К А BTGPCHGMY СВИДЕТЕЛЬСТВУ

ГОСУДАРСТВЕННЫЙ КОМИТЕТ

ПО ИЗОБРЕТЕНИЯМ И ОТНРЫТИЯМ

ПРИ ГКНТ СССР (21) 4398280/24-24 (22) 25.03.88 (46) 23.09.89. Вюл. Р 35 (72) Г.Н.Тимонькин, В.С.Харченко, С,Н.Ткаченко и Д.В.Дмитров (53) 681.325 (088.8) (56) Авторское свидетельство СССР

Р 1111165, кл. G 06 F 9/46.

Авторское свидетельство СССР

Р 1269136, кл. G 06 F 9/46, 1985. (54) УСТРОЙСТВО ДЛЯ РАСПРЕДЕЛЕНИЯ

ЗАДАНИЯ ПРОЦЕССОРАИ

Изобретение относится к вычисль; тельной технике и может быть использовано в многопроцессорных системах для оперативного распределения задач между процессорами.

Цель изобретения — повьппейие быстродействия устройства.

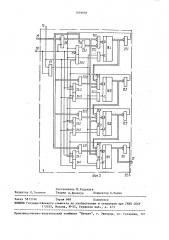

На фиг. 1 приведена функциональная схема предалагаемого устройства; на фиг.2 — функциональная схема блока регистров.

Устройство для распределения зада ний процессорам (фиг.1) содержит каналы и в каждом канале триггер 1, блок 2 элементов И, элементы И 3 и 4, о элемент ИЛИ 5, а также общие для всего устройства блок 6 регистров, блок

7 элементов ИЛИ, элемент ИЛИ 8, блоки 9 и 10 элементов И, элементы ИЛИ

11 и 12, элемент И 13, группы инфор мационных входов 14, тактовый вход

15, ответные входы 16, сигнальные вь

„„SU„„) 509895 A 1

2 . (57) Изобретение относится к вычислительной технике и может быть использовано в многопроцессорных сис- . темах. Цель .изобретения — повышение быстродействия. Устройство содержит блок регистров, блок элементов ИЛИ, два блока элементов И, три элемента

ИЛИ, элемент И, каждый канал — два элемента И и элемент ИЛИ, блок элементов И (кроме первого канала). В устройстве происходит распараллеливание процесса приема очередной задачи и подготовки устройства к приему следующей задачи. 2 ил.

1 ходы 17, группы информационных выходов 18.

Блок 6 регистров содержит регистры 19, блоки 20 элементов ИЛИ, элеменгы ИЛИ 21 и 2?, блоки 23 элементов И, элементы И 24 и 25, блок 26 элементов И и элемент И 27. 4"

Устройство работает следующим образом.

В начальном состоянии триггеры обнулены, блок 6 регистров не- со" фд держит никакой информации, на е 6" вы ходе - нулевой сигнал. Цепи установ- ки в исходное состояние условно не показаны. На выходе элемента ИЛИ 12 присутствует нулевой сигнал, следовательно, блок 10 элементов И открыт, а блок 9 элементов И закрыт.

На входы 14 устройства поступают коды задач для распределения по процессорам.

3 1509895

Поступление кода задачи на вход

14 устройства синхронизируется последовательностью синхроимпульсов на входе 15 сдвинутых относительно им5 пульсов по входу 14, т.е. код задачи на входе 14 появляется до появления очередного синхроимпульса на вхбде 15 и снимается до появления следующего за ним синхроимпульса. 10

Задача, поступивщая первой íà IIzoды 14 устройства, проходит через блок 2.1 элементов И для обслуживания в первый процессор. Код задачи также формирует единичный сигнал на 15 выходе элемента ИЛИ 8, который открывает элемент И 13. Очередной импульс с входа 15 проходит через элемент И

13 и элеменгы ИЛИ 5 на С-входы всех триггеров 1. Но по заднему фронту это.20 го импульса в единичное состояние устанавливается только триггер 1.1, ч ак как только íà его единичном входе единичный сигнал. Одновременно с кодом .задачи на выходе процессора 25 присутствует единичный сигнал с выхода 17. По заднему фронту этого сиг-. нала производится прием задачи в npoöåññoð. После того, как триггер 1.1 установится в единичное состояние, 30 нулевой сигнал с его инверсного выхода закрывает блок 2. 1 элементов

И и, действуя на инверсный вход элемента И 3.2, открывает его. В результате этого появляется единичный сиг35 нал на выходе элемента И 3.2. Этот сигнал открывает блок 2.2 элементтов И и очередная задача потупает в процессор этого канала аналогично описанному» .40

11 появляется единичный сигнал, который открывает элемент И 13 и, если .есть нераспределенные задачи в блоке 6 регистров или на инфорФ мационном входе 14, то очередной синхроимпульс проходит через открытый элемент И 13 и записывает задачу в освободившийся процессор.

После того, как последний свободный процессор возьмет задачу на об.служивание, на выходе элемента ИЛИ

11 появится нулевой сигнал, который, 45 действуя на инверсный вход элемента

KIN 12, вызовет на его выходе единичный сигнал. Этот сигнал закрывает блок 10 элементов И и открывает блок

9 элементов И для того, чтобы очередная задача поступила для хранения в блок 6 регистров. После того, как задача запишется в блок 6 регистров, на его сигнальном выходе появляется единичный сигнал, который через элемент ИЛИ 12 поддерживает нулевой сигнал на входе блока 10 элементов И и единичный сигнал на входе блока 9 элементов И. Это обеспечивает возможность выдавать задачи на обслуживание в соответствии с очередностью их поступления в устройство.

После того, как очередная задача поступит в блок 6 регистров, она ждет освобождения процессоров. На выходе элемента ИЛИ 8 постоянный единичный сигнал.

Как только один из процессоров закончит обслуживать задачу, он выставляет единичный сигнал на соответствующем входе 16. Сигнал с входа 16 открывает соответствующий элемент И

4 и поступает на нулевой вход соответствующего триггера 1. Таким об" разом, импульс с входа 15, пройдя через элемент И 4 и элемент ИЛИ 5, устанавливает триггер 1 в нулевое состояние. На выходе элемента ИЛИ

Формула и э о б р е и е н и я устройство для распределения заданий процессорам, содержащее каналы, каждый из которых содержит триггер, первый элемент И, и все каналы, кроме первого, содержат блок элементов

И, а также общие для всего устройства блок регистров, блок элементов

ИЛИ, первый и второй блоки элементов

И, три элемента ИЛИ, элемент И, причем группа информационных входов устройства подключена к группам информационных входов первого и второго блоков элементов И, выходы первого блока элементов И подключены к группе информационных входов блока регистров, выходы второго блока элементов И подключены к первым входам блока элементов ИЛИ, выходы которого подключены к группам информационных входов блоков элементов И каналов, инверсный выход триггера i-го канала (i=1, ..., п; и — число заданий) подключен к соответствующим инверсным входам первых элементов И каналов с (1+1)-го IIO Il йр к прямому входу первого элемента И i-го канала и к соответствующему входу первого элеменга ИЛИ, выход которого подклю1509895 чен к первому входу элемента И и к инверсному входу второго элемента

ИЛИ, выход второго элемента ИЛИ подключен к управляющим входам первого и второго блоков элементов И, синхронизирующий вход устройства подключен к второму входу элемента И, третий вход которого соединен с выходом третьего элемента ИЛИ, первая группа входов которого соединена с группой выходов блока регистров, выходы блоков элементов И каналов являются группами информационных выходов устройства, о т л и ч а ю щ е е— с я тем, что, с целью повышения быстродействия, в устройство введены в каждый канал второй элемент И и элемент ИЛИ, причем группа информационных входов устройства подключена к второй группе входов третьего элемента ИЛИ, выход элемента И подключен к первым входам элементов ИЛИ каналов, в каждом канале выход второго элемента И подключен к второму входу элемента ИЛИ своего канала, выход элемента ИЛИ канала подключен к тактовому входу триггера своего канала, синхронизирующий вход устройства подключен к первым входам вторых эле-. ментов И каналов, в каждом канале ответный вход устройства подключен к второму входу второго элемента И, 5 в каждом канале, начиная с второго, выход первого элемента И подключен к управляющему входу блоха элементов

И своего канала и является сигнальным выходом устройства, выход первого элемента ИЛИ подключен к управляющему входу блока регистров, информационные выходы которого подключены к вторым входам блока элементов ИЛИ, в каждом канале, начиная с второго, t5 выход первого элемента И подключен к единичному входу триггера, каждый ответный вход устройства соединен с нулевым входом триггера соответствующего канала, в первом канале инверс20 ный выход триггера соединен с единичным входом триггера, с управляющим входом блока элементов И и является первым сигнальным выходом устройства, тактовый вход которого соединен

25 с тактовым входом блока регистров, управляющий вход которого соединен с выходом первого элемента ИЛИ, прямой вход второго элемента ИЛИ соединен с сигнальным выходом блока реgp гистров.

1509895

Составитель М. Кудряшев

Техред А.Кравчук Корректор С.Черни

Редактор О.Головач

Заказ 5813/46 Тираж 668 Подписное

ВНИИПИ Государственного комитета по изобретениям и открытиям при ГКНТ СССР

113035, Москва, Ж-35, Раушская наб., д. 4/5

Производственно-издательский комбинат "Патент", г. Ужгород, ул. Гагарина, 101