Аналого-цифровая вычислительная система

Иллюстрации

Показать всеРеферат

Изобретение относится к вычислительной технике и может быть использовано для моделирования непрерывных и непрерывно-дискретных процессов. Целью изобретения является упрощение системы и повышение ее надежности. Аналого-цифровая вычислительная система содержит блок 1 распределения начальных условий, блок 2 памяти коэффициентов уравнений, селектор 3 адреса, (N+2) коммутирующие матрицы 4 аналоговых сигналов, (N+2) группы умножающих цифроаналоговых преобразователей 5 (УЦАП), N суммирующих усилителей 6, N интегрирующих усилителей 7, коммутатор 8 аналоговых сигналов, аналого-цифровой преобразователь 9 и регистр управления 10. Упрощение системы достигается на основе сокращения количества УЦАП 5 в каждой группе, используемых для задания коэффициентов матрицы моделируемой системы уравнений. Повышение надежности обеспечивается за счет оперативного переключения УЦАП внутри группы при выходе их из строя. 2 ил.

СОЮЗ СОВЕТСКИХ

СОЦИАЛИСТИЧЕСКИХ

РЕСПУБЛИК (19) (11) (5(1 4 G 06 J 1/00

E..ГЯ„"-Щ

: Е1М

ОПИСАНИЕ ИЗОБРЕТЕНИЯ

ГОСУДАРСТВЕННЫЙ НОМИТЕТ

ПО ИЗОБРЕТЕНИЯМ И ОТКРЫТИЯМ

ПРИ П(НТ СССР

К ASTOPCHOMY СВИДЕТЕЛЬСТВУ

1 (21) 4320080/24-24 (22) 26.10.87 (46) 23.09 .89 . Б л . К 35 (71) Отдел энергетической кибернетики АН МССР (72) И .Я.!Чор,А.А.Журавлев,М.Г.Левин, А.С.Трахтенберг и Г.П.Алехин (53) 681.34 (088.8) (56) Авторское свидетельство СССР

И - 1259300, кл. G 06 J 1/00, 1985.

Пухов Г.Е. и др. Автоматизированные цифроаналоговые устройства моде- лирования. — Киев, 1974, с. 172, рис. 76.

2 (54 ) АНАЛОГО-ЦИФРОВАЯ ВЫЧИСЛИТЕЛЬНАЯ

СИСТЕМА (57) Изобретение относится к вычислительной технике и может быть использовано для моделирования непрерывных и непрерывно-дискретных процессов.

Целью изобретения является упрощение системы и повышение ее надежности.

Аналого-цифровая вычислительная система содержит блок 1 распределения начальных условий, блок 2 памяти коэффициентов уравнений, селектор 3 адреса, (n+2) коммутирующие матрицы 4 аналоговых сигналов, (n+2) группы умз 1509955 4 ножающих цифроаналоговых преобразова- количества УЦАП 5 в каждой группе е телей 5 (УЦАП), и суммирующих усили- используеыах для задания коэффициентелей 6, и интегрирующих усилителей тов матрицы моделируемой системы

7, коммутатор 8 аналоговых. сигналов, уравнений. Повышение надежности обесан галого-цифровои преобразователь 9 и печивается за счет оперативного пере5 регистр управления 10. Упрощение сис- ключения УЦАП внутри группы при выхотемы достигается на основе сокращения . де их из строя. 2 ип. х, а(,х! +... +а,; х;+... +а,„х„+Ь,; !! Щ q !!д n !! °

I (1)50 с начальными условиями х! (0) х!Оэ ° ° вх! (0) х !о э ° ° ° э х„(0) = х„ 55

В соответствии с значениями коэффициентов а, Ъ| и начальных условий х1 уравнений (1) по известной е

Изобретение относится к.вычислительной технике и может быть использовано дпя моделирования непрерывных и непрерывно-дискретных процессов и систем управления в реальном и ускоренном масштабе времени.

Цель изобретения †упрощение системы и повышение ее надежности.

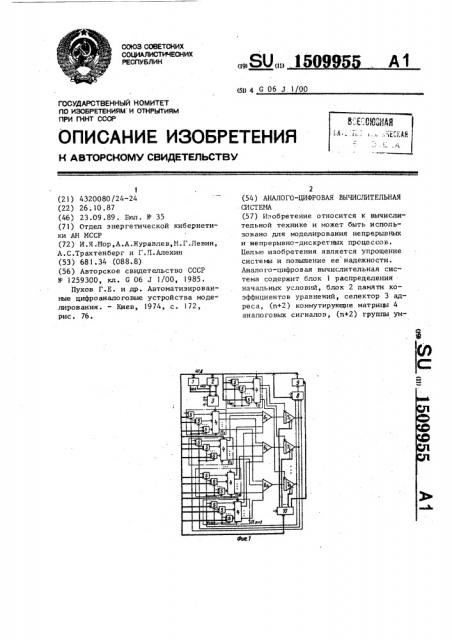

На фиг. 1 изображена блок-схема аналого-цифровой вычислительной системы; на фиг. 2 — алгоритм, поясняющий процесс автоматического набора схемы моделирования . 25

Вычислительная система содержит блок I распределения начальных условий, блок 2 памяти коэффициентов уравнений, селектор 3 адреса, (и+2) коммутирующи)с матриц аналоговых curn+z налов 4, " n умножающих цифроана1 ) =! логовых преобразователей (УЦАП) 5, причем m и, п суммирующих усилителей 6, и игтегрирующих усилителей 7, коммутатор 8 аналоговых сигналов, аналого-цифровой преобразователь (АЦП) 9 и регистр 10 управления.

Группа из m УЦАП 5, аналоговые входы которых йодключены к одной из пе- 40 ременных х, а выходы — к входам j-й коммутирующей матрицы 4 образуют j-й блок ll автонабора.

На этапе подготовки в блок 2 памяти загружается программа пользовате- 45 ля, содержащая исходную систему из и дифференциальных уравнений первого порядка: методике производится масштабирование переменных с определением соответствующих значений коэффициентов передачи k, 1.-« и коэффициента в о! цепи установки начальных условий k

10! для установки на УЦАП 5. При этом запоминаются индексы i u j отличных от нуля коэффициентов, по которым формируются коды управления коммутирующими матрицами 4.

Вычислительная система работает следующим образом.

В исходном состоянии блок 1 записывает в регистр !О код, в соответствии с которым на управляющих входах интеграторов 7 устанавливается режим !Исходное положение", а вход !Пуск"

ЛЦП 9 блокируется. Затем под управле.— нием блока l селектором 3 адреса последовательно выбирается УЦАП 5 и по шине данных иэ блока 2 памяти во внутренние регистры умножающих ЦАП 5 записываются значения соответствующих коэффициентов 1;,", k 1„ и k рассчитанных на этапе подготовки.

Аналогичным образом блок 1 осуществляет последовательную запись Во внутренние регистры коммутирующих матриц

4 кодов управления, сформированных по индексам тех коэффициентов а;,Ь; начальных условий х... которые в конкретном исходном уравнении (1) отличны от нуля. Таким образом, в исходном состоянии в УЦАП 5 установлены значения коэффициентов К;, k b и ..

1с„;, а в коммутирующих матрицах 4 г установлены связи, определяющие схему моделирования для заданной системы уравнений (1) с неполной матрицей отличных от нуля коэффициентов °

Алгоритм процесса автонабора схемы моделирования под управлением блока 1 приведен на фиг. 2, где k коэффициенты, устанавливаемые на

УЦАП 5, причем k<„„ = kb,, kl„, 1 ф01

5 15099

Решение системы уравнений (1) на- чинается при поступлении от блока 1 через регистр 10 управления сигналов

"Пуск" на управляющие. входы интегра5 торов 7. Таким же образом на управляющие входы интеграторов 7 подаются и другие сигналы управления его режимами: "Останов", Исходное положение".

При необходимости ввода аналоговой )p переменной в блок 2 памяти блок 1 через селектор 3 адреса обращается к коммутатору 8, в который заносит по шине данных. код, приводящий к подключению необходимо переменной х; к ана- (5 логовому входу АЦП 9. Затем на управляющий вход АЦП 9 через регистр 10 от блока 1 подается сигнал "Запуск

АЦП". Преобразованный сигнал считывается по шине данных в блок 2 памя- 20 ти по истечении времени преобразовайия. Иоделирование нелинейных уравнений возможно путем модуляции коэффициентов, например воспроизведение функции Ъ, = f(х;) путем считывания 25 х через АЦП 9 в блок 2 памяти выбор-! ки значения Ь;, соответствующего значению х; и соответствующего изменения коэффициента на УЦАП 5.

Таким образом обеспечивается . 30 уменьшение аппаратурных затрат путем сокращения количества УЦАП в каждой

j-й группе (j = 1,....,n+2) с п до

m и подключения их к входам сумми1 рующего усилителя через коммутирующую матрицу аналоговых сигналов размерностью mÄ хп, т.е. в матричную модуль вводятся (n+2) блоков автонабора, исключающие избыточность, имеющую место при наборе полной матрицы 40 коэффициентов для предельно предус.мотренного случая моделирования . всех п уравнений со всеми п (и+2) членами и начальными условиями. Предлагаемое решение позволяет за счет 45 учета разряженности матрицы коэффи) циентов повысить порядок автоматически набираемой системы уравнений. Кроме того, обеспечивается увеличение надежности и гибкости автонабора за счет того, что при выходе из строя любого из m УЦАП j-й группы схем ав1 тонабора вместо него может быть оперативно использован другой УЦАП той же группы.

Формула изобретения

Аналого-цифровая вычислительная система, содержащая (n+1) -ю группу

55 6 умножающих цифроаналоговых преобразователей, блок распределения начальных условий, подключенный шинами адреса, данных и управления к шинам адреса данных и управления блока памяти коэффициентов уравнений соответственно, аналого-цифровой преобразователь, соединенный выходом с шиной данных блока распределения начальных условий, а информационным входом — с выходом коммутатора аналоговых сигналов, информационные входы которого соединены с выходами п интегрирующих усилителей, а управляющий вход— с шиной данных блока расп1.еделения начальных условий, о т л и ч а ю— щ а я с я тем, что, с целью упрощения системы и повышения ее надежности, она содержит (n+2)-ю группу умножающих цифроаналоговых преобразователей, и суммирующих усилителей, n+2 коммутирующих матрицы аналоговых сигналов, регистр управления и селектор адреса, причем каждая j — я (1 < j < n+

+1) коммутирующая матрица аналоговых сигналов подключена каждым 1;-м (1 = k m, где ш n) сигнальным входом к выходу k-го умножающего цифроаналогового преобразователя j — и группы, а каждым i-м (1 < i « <- и) выходом к j-му входу i-ro суммирующего усилителя, соединенного выходом с игнальным входом i-го интегрирующего усилителя, подключенного выходом к аналоговым входам умножающих цифроаналоговых преобразователей i — и группы, а входом задания начальных условий — к i-му выходу (n+2) — и коммутирующей матрицы анало говых сигналог, соединенной сигнальными входами с выходами умножающих цифро анало говых преобразователей (и+2) -й группы, причем аналоговые входы умножающих цифроаналоговых преобразователей (n+1)-й и (n+2)-й групп подключены к шине ввода опорного напряжения, а входы управления режимом работы и интегрирующих усилителей и управляющий вход аналого-цифрового преобразователя соединены с выходами соответствующих разрядов регистра управления, причем цифровые входы всех умножающих цифроаналоговых преобразователей всех группу, управляющие входы всех коммутирующих матриц аналоговых сигналов и информационные входы регистра управления подключены к шине данных блока распределения начальных усло-1509955 иер мементо 8 cmelpe раца ктрфициенпа5,i: 1, а; ер д еиенва 5строкЕ j= t, п.Х; ер МРЛД 5Ьеи, г=,, вю ЯАПА-ео длока Л на8либаевся k, aemar иснеакв иежф хо&е и i--н Анодом иди 4

Составитель С.Казинов

Редактор И.Бланар Техред Л.Сердюкова Корректор M.Еароши

Заказ 5816/49 Тираж 668 Подписное

ВНИИПИ Государственного комитета по изобретениям и открытиям при ГКНТ СССР

113035, Москва, Ж-35, Раушская наб., д. 4/5

Производственно-издательский комбинат "Патент", r.Óæãoðoä, ул. Гагарина, 101 вий, соединенного шиной адреса и шиной управления с адресными и управЛяющими входами селектора адреса соответственно, выходы разрядов которого подключены к соответствующим стробирующим входам коммутатора аналоговых сигналов, регистра управления, коммутирующих матриц аналоговых сигналов и умножающих цифроаналоговых преобразователей всех групп.