Усилитель мощности

Иллюстрации

Показать всеРеферат

Изобретение относится к радиотехнике. Цель изобретения - увеличение КПД при работе на комплексную нагрузку. Усилитель мощности содержит двухтактный каскад 1, выполненный на транзисторах 2 и 3 разной структуры, и нагрузку 4. Каждое плечо каскада 1 включает диоды 5, 6 и 9, ключи 7, 8 и 10, многоуровневый компаратор 11 напряжения и источники питания блока питания 12. При работе каскада 1 на комплексную нагрузку 4 сдвиг по фазе между током и напряжением приводит к тому, что во время работы транзистора 2 напряжение на нагрузке 4 принимает отрицательные значения в моменты , когда ток не совпадает по фазе с напряжением. В эти моменты для снижения остаточного напряжения включаются источники питания с противоположной данному плечу полярностью питающего напряжения и источник с нулевым напряжением питания. При этом переход на источники с другой полярностью напряжения осуществляется без изменения направления тока нагрузки. Введение общей (нулевой) и отрицательных ступеней питающих напряжений позволяет снизить потери. 2 ил.

СОЮЗ СОВЕТСКИХ

СОЦИАЛИСТИЧЕСНИХ

РЕСПУБЛИН

„„SU„„1510068

А1 (51)4 Н 03 F 3/20

ОПИСАНИЕ ИЗОБРЕТЕНИЯ

К АВТОРСКОМУ СВИДЕТЕЛЬСТВУ

ГОСУДАРСТВЕННЫЙ КОМИТЕТ

ПО ИЗОБРЕТЕНИЯМ И ОТКРЫТИЯМ

ПРИ ГКНТ СССР

1 (21) 4320708/24-09 (22) 26.10.87 (46) 23.09.89. Бюл. К 35 (72) А.Н.Заварыкин, П.И.Клюев и В.А.Майоров (53) 621.375.026(088 ° 8) (56) Патент СНА № 3319175, кл. 330-22, 1967. (54 ) УСИЛИТЕЛЬ МОЩНОСТИ (57) Изобретение относится к радиотехнике. Цель изобретения — .увеличение КПД при работе на комплексную нагрузку. Усилитель мощности содержит двухтактный каскад 1, выполненный на транзисторах 2 и 3 разной структуры, и нагрузку 4. Каждое плечо каскада 1 включает диоды 5, 6 и

9, ключи 7, 8 и 10, многоуровневый компаратор 11 напряжения и источни2 ки питания блока питания 12. При работе каскада 1 на комплексную нагрузку 4 сдвиг по фазе между током и напряжением приводит к тому, что во время работы транзистора 2 напряжение на нагрузке 4 принимает отрицательные значения в моменты, когда ток не совпадает по фазе с напряжением.. В эти моменты для снижения остаточного напряжения включаются источники питания с противоположной данному плечу полярностью питающего напряжения и источник с нулевым напряжением питания. При этом переход на источники с другой полярностью напряжения осуществляется без изменения направления тока нагрузки. Введение общей (нулевой) и отрицательных ступеней питающих напряжений позволяет снизить потери. 2 ил. щадь, соответствующая мощности потерь для,первого и второго случаев.

Таким образом,. предложенный усилитель мощности обеспечивает более высокий КПД при работе на комплексную, нагрузку.

Формула изобретения

Усилитель мощности, содержащий двухтактный каскад, выполненный на

3 1510068

Изобретение относится к радиотехнике, а именно к усилителям мощности, работающим в режимах В, АВ, С,и может быть использовано для усиления сигналов низкой частоты.

Цель изобретения — увеличение КПД при работе на комплексную нагрузку .

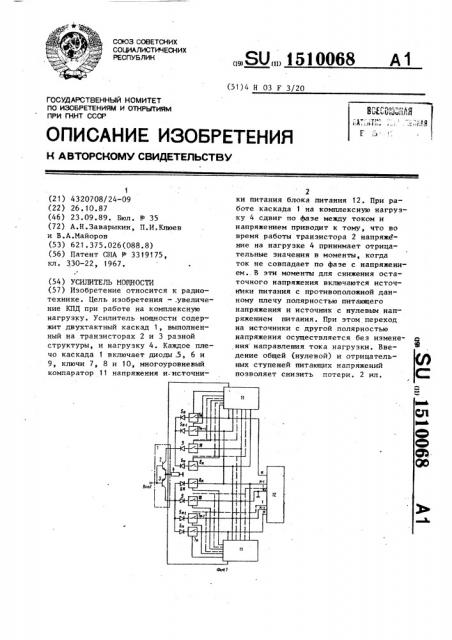

На фиг. 1 представлена структурная электрическая схема предложенного усилителя мощности, на фиг. 2 — временная диаграмма работы устройства. Усилитель мощности содержит двухтактный каскад 1, выполненный на транзисторах 2 и 3 разной структуры, 15 нагрузку 4, в каждом плече которого

N первых диодов 5,-. 5 ° ° ° 5„ N вторых диодов 6,, 6, ..., 6„, N первых ключей 7,, 7т, ... ° 7к, N вторых ключей 8 „, 8, ° ... 8щ, допол- 20 нительный диод 9, дополнительный ключ

10, многоуровневый компаратор 11 напряжения, блок 12 питания.

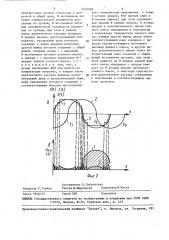

На фиг. 2, а кривая 1,соответствует напряжению в нагрузке, кривая 2 — 25 току в нагрузке, кривая 3 — напряжению на коллекторе транзистора. На фиг. 2,,5 кривая 1 соответствует напряжению коллектор-эмиттер транзистора для усилителя без нулевой и отри- 30 цательной ступеней питающих напряжений, кривая 2 — для предложенного технического решения. Штриховкой показана площадь, определяющая тепловые потери в первом и во втором случаях.

В предлагаемом устройстве, ключи

6-8 и 10 могут быть выполнены, например, на транзисторах, многоуровневые компараторы напряжений представ- 40 ляют собой систему компараторов, сигнальные входы которых объединены, а блок 12 питания содержит двухполярные источники питания с разными по уровню питающими напряжениями. 45

Устройство работает следующим образом.

Работа двухтактного каскада 1 этого усилителя от известного отличает-: ся только включением питающих напря50 жений при комплексном характере нагрузки. Сдвиг по фазе между током и напряжением приводит к тому, что во время работы транзистора 2 (на фиг.2, а интервал времени t,,t ) напряжение на нагрузке принимает отрицательные значения в моменты времени, когда ток не совпадает по фазе с напряжением. В эти моменты времени для снижения остаточного напряжения включаются источники питания с противоположной данному плечу полярностью питающего напряжения и источник с напряжением питания, равным нулю.

Характерно, что переход на источники с другой полярностью напряжения осуществляется без изменения направления тока нагрузки. Это связано с тем, что эти источники работают "На заряд", не отдают, а потребляют энергию. Тем самым реализуется принцип рекуперации энергии: при работе "На заряд" конденсаторы фильтров источников питания заряжаются, а затем при работе другого плеча разряжаются. Энергия, потребляемая от источника при этом, снижается. Введение общей (нулевой) и отрицательных ступеней питающих напряжений позволяют снизить потери, что наглядно показано на фиг. 2,о.

Пороги срабатывания многоуровневого компаратора 11 устанавливаются таким образом, чтобы к коллекторам транзисторов двухтактного каскада в любой момент времени было приложено минимальное из напряжений источников, превышающее напряжение в нагрузке на величину, нео(ходимую для того, чтобы транзисторы находились в активном режиме.

На фиг. 2, q приведены кривые, соответствующие току (кривая 2), напряжению (кривая 1) в нагрузке 4 и напряжению на коллекторах транзисторов

2 и 3 (кривая 3) для случая индуктивной нагрузки с cos g- =О. Напряжение в нагрузке опережает по фазе ток на

90 . Транзистор двухтактного каскада открывается в момент времени t закрывается в момент времени t . Йапряжение в нагрузке изменяется за этот интервал времени от максимума до минимума, На фиг. 2, 6 кривая 1 соответствует остаточному напряжению на транзисторах для известного усилителя, кривая 2 — для предлагаемого устройства. Штриховкой показана пло5 151 транзисторах разной структуры с нагрузкой в общей цепи, N источников питания отрицательной полярности различных по уровню, N источников питания положительной полярности различ0068

u(<) И) б

Ок3

И) Составитель Н.Дубровская

Техред N.Моргентал Корректор И.Иуска

Редактор -Г. Гербер

Заказ 5828/55 Тираж 884 Подписное

ВНИИПИ Государственного комитета по изобретениям и открытиям при ГКНТ СССР

113035, Москва, Ж-35, Раушская наб., д. 4/5

Производственно-издательский комбинат "Патент", г. Ужгород, ул. Гагарина, 101 ных по уровню, при этом в каждом плече двухтактного каскада включено

N первых диодов, многоуровневый компаратор, сигнальный вход которого соединен с одним выводом нагрузки, другои вывод которой соединен с общей шинои, опорные входы — с выводами

N источников питания соответственно, а выходы — с входами управления N- 1 первых ключей соответственно, о т— л и ч а ю шийся тем, что, с целью увеличения КПД при работе на комплексную нагрузку, в каждом плече двухтактного каскада введены дополнительный диод и дополнительный ключ, вхбд управления которого соединен с соответствующим выходом многоуровневаго компаратара напряжения, а также

iV вторых диодов, N-й первый ключ и вторых ключей, при этом одноименные выводы И первых диодов, N вторых

5 диодов и дополнительного диода каждого плеча объединены и подключены к коллектору транзистора данного плеча, каждый другой вывод диода через соответствующий ключ соединен с выводом соответствующего источника питания данного плеча, а другой вывод дополнительного диода через дополнительный ключ соединен с общей шиной источников питания, при этом вход каждого из N первых ключей данного плеча объединен с входом каждого из N вторых ключей противоположного плеча, а эмиттеры транзисторов двухтактного каскада объединены и подключены к соответствующему выводу нагрузки.