Способ знаковой дельта-модуляции и устройство для его осуществления

Иллюстрации

Показать всеРеферат

Изобретение относится к автоматике и вычислительной технике. Его использование в корреляционных системах для идентификации образов позволяет повысить быстродействие и расширить область применения за счет формирования дельта-модулированных (ДМ) сигналов второго и более высоких рангов. Способ реализуется в устройстве, содержащем элемент 1 <SB POS="POST">1</SB> вычитания, дискретизатор 2 <SB POS="POST">1</SB> и элемент задержки 3 <SB POS="POST">1</SB>. Благодаря введению остальных элементов 1 вычитания, дискретизаторов 2, элементов 3 задержки, а также групп 4 и 5 компараторов, сумматоров 6 и источников 7 и 8 положительного и отрицательного опорных сигналов в устройстве обеспечивается одновременное и практически безынерционное формирование знаковых ДМ - сигналов, начиная с первого ранга. 2 ил.

СОЮЗ СОВЕТСКИХ.

СОЦИАЛИСТИЧЕСКИХ

РЕСПУБЛИК

А1 (50 4 Н 03 M 3/00

ВЛ1ИЗМ 1 .1 !юil описдник изоБРКткниЯ

К АВТОРСКОМУ СВИДЕТЕЛЬСТВУ

ГОСУДАРСТ8ЕННЫЙ КОМИТЕТ

ПО ИЗОБРЕТЕНИЯМ И ОТКРЫТИЯМ пРи п<нт сссР (21) 4306861/24-24 (22) 03.08.87 (46) 23.09.89. Бюл. Р 35 (71) Физико-механический институт им. Г.В. Карпенко и Специальное конструкторско-технологическое бюро

Физико-механического института им. Г.В.Карпенко (72) В.А.Погрибной, О.P. Пристайко, И.В.Рожанковский и Ю.Ф.Кутаев (53) 621.376,56 (088.8) (56) Стил Р. Принципы дельта-модуляции.-И.: Связь, 1979, с, 13-16.

Дельта-модуляция. Теория и применение./Под ред. М.Д.Венедиттова.-И.:

Связь, 1976, с. 24, рис. 2,2. (54) СПОСОБ ЗНАКОВОЙ ДЕЛЬТА-МОДУЛЯЦИИ И УСТРОЙСТВО ДЛЯ ЕГО ОСУЩЕСТВЛЕНИЯ (57) Изобретение относится к автома„„ЯО„„!5100 9

2 тике и вычислительной технике. Его использование в корреляционных системах для идентификации образов позволяет повысить быстродействие и расширить область применения за счет формирования дельта-модулированных (ДМ) сигналов второго и более высоких рангов. Способ реализуется в устройстве, содержащем элемент 1) вычитания, дискретизатор 2 и элемент задержки 3, . Благодаря введению остальных элементов 1 вычитания, дискретизаторов 2, элементов 3 задержки, а также групп 4 и 5 компараторов, сумматоров б и источников 7 и 8 положительного и отрицательного опорных сигналов в устройстве обеспечивается одновременное и практически безынерционное формирование знаковых ДМ-сигналов, начиная с первого ранга.

2 с.п. ф-лы, 2 ил.

3 1510089

Изобретение относится к автоматике и вычислительной технике и может быть использовано в корреляционных системах для идентификации образов.

Цель изобретения — повышение быстродействия и расширение области применения за счет формирования дельтамодулированных сигналов второго и более высоких рангов ° 10

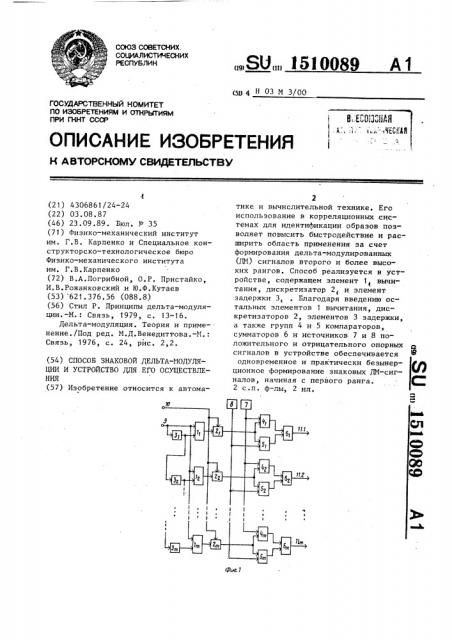

На фиг. 1 приведена блок-схема устройства, реализующего способ; на фиг. 2 — временные диаграммы сигналов.

Способ включает в себя: задержку входного сигнала на фиксированную величину (1, 2, 3,..., m периодов дискретизации); формирование разностей входного сигнала с каждым из задержанных; дискретизацию полученных 20 разностей с периодом дискретизации; запоминание дискретизированных значений какой-либо разности на период дискретизации; формирование равных, но разнополярных (т.е. положитель- 25 ного и отрицательного). опорных сигналов; сравнение каждого запомненноГо значения каждой разности с опорными сигналами; если. запомненное значение всякой разности больше положи- 30 тельного или меньше отрицательного опорных сигналов, формируют сигнал соответственно первой и второй полярности (например, положительный или отРицательный) с длительностью в период дискретизации; в противном случае формируют нулевые сигналы той же длительности.

Устройство содержит элементы 1 вычитания, дискретизаторы 2, элементы 40

3 задержки, первую 4 и вторую 5 группы компараторов, сумматоры 6, источники 7 и 8 положительного и отрицательного опорных сигналов. На фиг. обозначены информированный 9 и тактовый 10 входы и выходы 11.

В основе работы устройства, реализующего способ, лежит следующий новый алгоритм: f, х;-х;,. 3 >

О,-Ь х„-х;„ 3, N = ENT (8/T)

1, х, -х,,.( где 8 — интервал реализации случайного входного сигнала; Т вЂ” период дискретизации; r — - ранг.

Кодовое представление сигналов в предлагаемом способе знаковой дельтамодуляции (ДМ) подобно кодовому представлению сигналов при троичной ДИ, однако при первой из них оперируют знаками приращений, а при второй— взаимосвязанными шагами квантования, абсолютную величину которых для удоб" ства приравнивают к единице.

Ири любых видах дельта-модуляции нельзя допускать перегрузку по крутизне дельта-кодера, так как частота дискретизации при ДК связана с абсолютной величиной шагов квантования и, как правило, выше частоты Найквиста. В предлагаемом способе принципиально не требуется никаких шагов квантования, и частота дискретизации может быть равна и меньше частоты

Найквиста, а это ведет к резкому повышению скорости кодирования, т.е. увеличению полосы частот обрабатываемых сигналов при использовании одинаковой элементной базы.

Способ реализуется в предложенном устройстве следующим образом.

Входной сигнал x(t) (фиг. 2) поступает с информационного входа 9 на первые входы всех элементов вычита" ния, на вторые входы которых поступает задержанный входной сигнал. Время задержки сигнала в каждом элементе 3 задержки равно периоду дискретизации Т (фиг. 2).

Рассматривается более подробно формирование дельта-модулированных сигналов первого ранга на выходе первого сумматора б, так как работы остальных m-1 каналов аналогична.

Элемент 1,1 обеспечивает вычитание из входного сигнала задержанного (фиг. 26) сигнала. Двухполярный разностный сигнал x(t)-x(t"Т) с выхода элемента 1.1 (фиг. 22) поступает на вход дискретизатора 2.1, который под воздействием тактовых импульсов, поступающих с входа 10 устройства (фиг. 2S), обеспечивает дискретизацию разностного сигнала и запоминание его дискретных значений на время, равное периоду дискретизации. Выходной сигнал дискретизатора (фиг. 2 ) поступает на первые входы компараторов 4.1 и 5.1, которые производят сравнение входных сигналов одной полярности. Компаратор 4.1 производит сравнение положительного разностного сигнала с положительным опорным сигналом, поступающим с блока 7, а компаратор 5 — отрицательного разностно-.

5 151008

ro сигнала с отрицательным опорным сигналом, поступающим с блока 8.

Величину опорных сигналов источников 7 и 8 выбирают на основании априорных данных в диапазоне измене5 ния сигнала и допустимой погрешности изменения его прироста.

Если сигнал на первых входах компараторов 4.1 и 5. l не превышает по абсолютной величине опорных сигналов, на их выходах формируются нулевые сигналы. Если входной сигнал на первых входах обоих компараторов 4.1 и

5,1 превышает положительньпr опорный сигнал, на выходах компаратора 4.! и

5.1 формируются соответственно положительный единичный (Аиг. 2e) и нулевой (Аиг. 2 К) сигналы. Если входной сигнал на;первых входах обоих 20 компараторов меньше отрицательного опорного сигнала, на выходах компараторов 4.1 и 5.1 Аормируются нулевой и отрицательный единичный сигналы.

Сумматор 6.1 обеспечивает объединение 25 (суммирование) выходных сигналов первого 4.1 и второго 5.1 компараторов.

Таким образом, на выходе первого сумматора 6.1 формируются знаковые дельта-модулированные сигналы Первого ранга. Дельта-модулированный нулевой сигнал свидетельствует о постоянстве входного сигнала с флуктуациями не более + $, единичные положительные и отрицательные дельта-модулированные сигналы свидетельствуют о возрастании или убывании входного сигнала. Анализ выходного сигнала устройства позволяет исследовать характер изменения входных сигналов с вы40 сокой крутизной нарастания.

Формирование дельта-модулированных сигналов высоких рангов осуществляется аналогично.

Знаковые дельта-модулированные сигналы более высоких рангов необходимы 45 при исследовании как характера изменения входных сигналов, так и характера их взаимосвязи (в том числе стохастической) при построении сложных корреляционных систем для идентификации образов.

Формула изобретения

1. Способ знаковой дельта-модуляции, заключающийся в том, что входной сигнал задерживают на фиксированное время, формируют разностный

6 сигнал между входным и задержанным сигналами, дискретизируют полученный разностный сигнал с периодом, равным фиксированному времени задержки, и запоминают дискретизированное значение разностного сигнала на период дискретизации, о т л и ч а ю щ и йс я тем, что, с целью повышения быстродействия и расширения области применения за счет формирования дельта-модулированных сигналов второго и более высоких рангов, предварительно Аормируют равные по амплитуде и разнополярные опорные сигналы, задерживают входной сигнал соответственно на 2, З,...,m периодов дискретизации (rye m — число рангов), Аормируют разностный сигнал между выходным и каждым из задержанных сигналов, дискретизируют каждый из сфор" мированных разностных сигналов с периодом дискретизации, запоминают дискретизированные значения каждого разностного сигнала на период дискретизации, сравнивают каждое запомненное значение каждого разностного сигнала с опорными сигналами, если запомненное значение разностного сигнала больше амплитуды положительного или меньше амплитуды отрицательного опорных сигналов, Аормируют сигнал соответс-,венно положительной или отрицательной полярности фиксированной амплитуды с длительностью, равной периоду дискретизации, в противном случае формируют нулевой сигнал той же длительности. !

2. Устройство для знаковой дельта-модуляции, содержащее первый элемент вычитания, первый вход которогО объединен с входом первого элемента задержки и является информационным входом устройства, выход первого элемента задержки соединен с вторым входом первого элемента вычитания, выход которого подключен к информационному входу дискретизатора, тактовый вход которого является тактовым входом устройства, о т л и ч а ющ е е с я тем, что, v. целью повышения быстродействия и расширения области применения за счет формирования дельта-модулированных сигналов ,второго и более высоких рангов, в устройство введены источники положительного и отрицательного опорных сигналов, m сумматоров, первая и вто1510089

1О

15 оа1

Жив е

Фиг.2

Составитель О.Ревинский

Техред Л. Олийнык Корректор Н.Борисова

Редактор Г.Гербер

Заказ 5829/56 Тираж 884 Подписное

ВНИИПИ Государственного комитета по изобретениям и открытиям при ГКНТ СССР

113035, Москва, Ж-35, Раушская наб., д. 4/5

Пройзводственно-издательский комбинат "Патент", r.Ужгород, ул. Гагарина,10) рая группа по m компараторов, второй — m-й элементы задержки, второй—

m-й дискретизаторы и второй — m-й элементы вычитания, первые входы которых объединены и подключены к информационному входу устройства, вход второго элемента задержки подключен к выходу первого элемента задержки, выход j-ro элемента задержки (j-2, «т:1) соединен с вторым входом j-го элемента вычитания и входом Ц+1)-го элемента задержки, выход -ro элемента задержки подключен к второму входу m-ro элемента вычитания, выходы второго - m-ro элементов вычитания соединены с информационными вхо1 дами одноименных дискретизаторов, тактовые входы которых объединены и подключены к тактовому входу устройства, выходы первого — m-го дискретизаторов соединены с первыми входами одноименных компараторов первой и второй групп; выходы источников положительного и отрицательного опорных сигналов подключены к вторым входам компараторон соответственно первой и второй групп, выходы одноименных компараторов обеих групп соединены с первым и вторым входами одноименного сумматора, выход которого является соответствующим выходом устройства.