Устройство для обработки данных

Иллюстрации

Показать всеРеферат

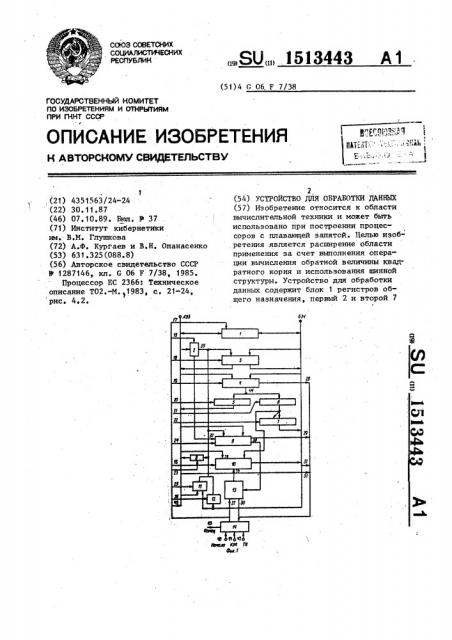

Изобретение относится к области вычислительной техники и может быть использовано при построении процессоров с плавающей запятой. Целью изобретения является расширение области применения за счет выполнения операции вычисления обратной величины квадратного корня и использования шинной структуры. Устройство для обработки данных содержит блок 1 регистров общего назначения, первый 2 и второй 7 мультиплексоры, блок 3 умножения, арифметико-логический блок 4 мантисс, первый 5 и второй 6 буферные регистры, блок 8 коррекции частного, узел 9 поиска левой единицы, блок 10 сдвига, блок 11 приближенного деления, блок 12 приближенного вычислений корня, арифметический блок 13 пордяков, блок 14 микропрограммного управления с соответствующими связями. 18 ил.

СОЮЗ СОВЕТСНИХ

СОЦИАЛИСТИ ЕСНИХ

РЕСПУБЛИК (51)4 G 06. F 7/38

ОПИСАНИЕ ИЗОБРЕТЕНИЯ

К А 8TOPCHOMV СВИДЕТЕЛЬСТВУ

ВтГФР9крq Ф у 1

ГОСУДАРСТВЕННЫЙ КОМИТЕТ

ПО ИЗОБРЕТЕНИЯМ И ОТКРЫТИЯМ

ПРИ ГКНТ СССР

1 . (21) 4351563/24-24 (22) 30. 11.87 (46) 07.10.89. Бюл. Р 37 (71) Институт кибернетики им. В.М. Глушкова (72) А.Ф. Кургаев и В.Н. Опанасенко (53) 631.325 (088.8) (56) Авторское свидетельство СССР

В 1287146, кл. G 06 F 7/38, 1985.

Процессор ЕС 2366: Техническое описание Т02.-М. 1983, с. 21-24, рис. 4.2.

„.SU„„1513443 А1

2 (54) УСТРОЙСТВО ДЛЯ ОБРАБОТКИ ДАННЫХ (57) Изобретение относится к области вычислительной техники и может быть использовано при построении процессоров с плавающей запятой. Целью изоб» ретения является расширение области применения sa счет выполнения операции вычисления обратной величины квад" ратного корня и использования шинной структуры. Устройство для обработки данных содержит блок 1 регистров общего назначения, первый 2 и второй 7

3 15 мультиплексоры, блок 3 умножения, арифметико-логический блок 4 мантисс, первый 5 и второй 6 буферные регистры, блок 8 коррекции частного, узел 9 поиска левой единицы, блок 10 сдвига, t3443 4 блок 11 приближенного деления, блок

12 приближенного вычисления корня, арифметический блок 13 порядков, блок 14 микропрограммного управления с соответствующими связями. 18 ил.

Изобретение относится к вычислительной технике и может быть использовано при построении арифметических процессоров с плавающей запятой.

Целью изобретения является расши- 15 рение области применения за счет выполнения операции вычисления обратной величины квадратного корня и использования шинной структуры.

На фиг. 1 представлена схема уст- 2О ройства для обработки данных; на фиг. 2 — схема блока умножения; на фиг. 3 — схема арифметико-логического блока мантисс; на фиг. 4 — схема узла поиска левой единицы; на фиг.5 — 25 схема блока сдвига; на фиг. 6 — схема блока коррекции частного; на

° фиг. 7 — схема арифметического блока порядков; на фиг. 8 — схема блока микропрограммного управления; на 30 фиг. 9 — схема узла регистрации состояния; на фиг. 10 — структура слова состояния; на фиг. 11 — структура микрокоманды; на фиг. 12 — диаграмма алгоритма операции вычитания; на фиг. 13 — диаграмма алгоритма операции сложения; на фиг. 14 — диаграмма алгоритма операции умножения; на фиг. 15-17 — диаграмма алгоритма операции деления; на фиг. 18 — диаграмма алгоритма операции вычисления обратной величины корня.

Устройство для обработки данных (фиг. 1) содержит блок 1 регистров общего назначения, первый мультиплек- 4g сор 2, блок 3 умножения, арифметикологический блок 4 мантисс, первый 5 и второй 6 буферные регистры, второй мультиплексор 7, блок 8 коррекции частного, узел 9 поиска левой еди- 50 ницы, блок 10 сдвига, блок 11 приближенного деления, блок 12 приближенного вычисления корня, арифметический блок 13 порядков, блок 14 микропрог.раммного упРавления, с первого по 55 тринадцатый управляющие выходы 15-27 соответственно блока 14 микропрограммного управлеж я, с первого по пятый входы 28-32 Условий блока 14 микропрограммного управления соответственно, первый А 33 и второй Б 34 двунаправленные информационные входы устройства, выход 35 мультиплексора 2, первый 36 и второй 37 информационные выходы узла 9 поиска левой единицы, первый информационный вход 38 блока

10 сдвига, вход 39 задания величины сдвига блока 10 сдвига, вход 40 начала работы устройства, вход 41 кода операции устройства, тактовый вход

42 устройства, выход 43 окончания работы устройства„ информационный выход 44 арифметико-логического блока 4 мантисс, ичформационный выход

45 блока 14 микропрограммного управления.

Структурные схемы блоков и узлов на фиг. 2-9 приведены для случая операндов двух форматов — "32" (24 разряда мантисса, 8 разрядов порядок) и "64" (56 разрядов мантисса, 8 разрядов порядок) разряда.

Блок 1 регистров общего .назначения предназначен для записи, хранения и считывания информации (побайтно или кратно байту) по двум двунаправленным входам А33 и Б34.

Мультиплексор 2 имеет трехстабильные выходы. Блок 3 умножения (фиг.2) содержит умножители (46-1)-(46-7), входи первых сомножителей которых соединены с входом 34 устройства, а входы вторых сомножителей — с выходом 35 мультиплексора 2, выходы старших и младших разрядов умножителей (46 1)-(46-7) являются соответствующими выходами блока 3 умножения, а вход разрешения соединен с выходом

18 блока 14 микропрограммного управления.

Арифметико-логический блок 4 мантисс (фиг.3) для разрядности "64" содержит четыре сумматора-вычитателя

47-50, элементы ИЛИ 51-53, демультиппексор 54, мультиплексор 55, элемент

KIN 56, выходы 57 сравнения операндов сумматоров-вычитателей, элемент

ИЛИ 58, группу сигнальных выходов

5 15134 арифметико-логического блока 4 мантисс, состоящую из выходов переноса

59, старшего разряда 60, разряда округления 61, равенства нулю 62 старших шестнадцати разрядов выхода 44 и равенства операндов 63, группу

Входов задания режима арифметико-логического блока 4 мантисс, состоящую из входов точности 64 (одинарная/ двойная), формата 65 (плавающая/фиксированная запятая), вида операции

66 и переноса 67, причем входы двадцати четырех старших разрядов ин34 подключе ны соответственно к первым и вторым информационным входам сумматора-вычитателя 50, следующие восемь (по-старшинству) входов разрядов информационных входов 33 и 34 соединены соответ- 20 ственно с первыми и вторыми информационными входами сумматора-вычитателя 49, младшие восемь входов разрядов информационных входов 33 и 34 подключены соответственно к первым и вторым 25 информационным входам сумматора-вы-! читателя 47, Остальные входы разрядов информационных входов 33 и 34 соединены соответственно с первыми и вторыми информационными входами сумматора- 30 вычитателя 48, выходы переноса сумматоров-вычитателей 47, 48 и 49 подключены к первым входам элементов ИЛИ 51>

52 и 53 соответственно, вторые входы которых соединены соответственно с первым, вторым и третьим выходами де35 мультиплексора 54 четвертый выход которого подключен к,входу переноса сумматора-вычитателя 47, выходы элементов ИЛИ 51, 52 и 53 соединены с входами переносов соответственно сумматоров-вычитателей 50, 49 и 48, выходы 57 сравнения операндов подключены к входам элемента ИЛИ 58, выходы сумматоров-вычитателей 47-50 соедине- .

45 ны с информационным выходом 44 блока

4, старшие шестнадцать выходов разрядов которого подключены к входам элемента ИЛИ 56, входы 64-67 группы

- блока- 4 подключены соответственно к управляющим входам демультиплексо.ра 54, мультиплексора 55, сумматороввычитателей 47-50 и к информационному входу демультиплексора 54 °

Буферные регистры 5 и 6 имеют вход сигнала записи и тристабильные выходы»

Мультиплексор 7 имеет два информационных входа и тристабильный выход

43 б и выполняет сдвиг на "8" бит влево нли передачу информации без сдвига. зел 9 поиска левой единицы (фиг,4) содержит восемь элементов ИЛИ (68-1)(68 8), два приоритетных шифратора

69 и 70 и мультиплексор 71, первый— восьмой входы байтов информационного входа 33 устройства подключены к входам соответственно первого — Восьмо» го элемента ИЛИ (68-1)-(68-8), выходы которых соединены с информационньии входами первого приоритетного шифратора 69, чьи выходы подключены к четвертому, пятому и шестому (старшим) выходам разрядов выхода Зб узла 9 и к первому информационному входу мультиплексора 71, управляющий и

ВторОи информационныи ВхОды кОтОрОгО, входы разрешения приоритетных шифраторов 69 и 70 соединены соответственно с входами разрядов входа задания режима узла 9, выход 37 которого соединен с выходами мультиплексора 71, сиг" нальные выходы приоритетных шифраторов 69 и 70 являются соответственно выходами 72 и 73 разрядов сигнального выхода узла 9 (наличие сигнала на выходах 72 и 73 соответствует отсутcTBpIo единичного бита), информационные выходы второго приоритетного шифратора 70 подк почены к трем младшим выходам разрядОВ выхода 36 узла 9, а информационные входы шифратора 70 соединены с выходом 35 мультиплексора 2.

Блок 10 сдвига (фиг. 5) предназначен для выполнения логических сдвигов влево и вправо на 0-63 бита и содержит пять сдвигателей 74-78. Первый сдвигатель 74 реализует сдвиг на О, 1, 2, 3 бита вправо, второй сдвигатель .75 — на О, 4, 8, 12 бит вправо, третий сдвигатель 76 — на

О, 16, 32, 48 бит вправо. Входы 38 и ЗЗ являются соответственно первым и BTQDbM информационными входами, выход третьего сдвигателя 76 — выходом блока 10 сдвига, вход 38 подключен к информационному входу четвертоа го сдвигателя 77, а входы трех младших разрядов входа 38 соединены с дополнительными входами разрядов первого сдвигателя 74, выходы разрядов последнего соединены с входами разрядов второго сдвигателя 75, дополнительные входы разрядов которого подключены к двенадцати младшим выходам, 1513443 разрядов четвертого сдвигателя 77

Э выходы разрядов пятого сдвигателя 78, выходы разрядов второго сдвигателя

75 подключены к входам разрядов третьего сдвигателя 76, сорок восемь до5 полнительных входов разрядов которого соединены с выходами разрядов пятого сдвигателя 78.

В случае выполнения правого сдвига 10 его реализация осуществляется на первом 74, втором 75 и третьем 76 сдвигателях. Операнд поступает на информационный вход первого сдвигателя 74.

Сигнал с выхода 16 поступает на входы 15 управления третьим состоянием четвертого 77 и пятого 78 сдвигателей и запрещает передачу через них информации на дополнительные входы разрядов второго 75 и третьего 76 сдвигателей.

Сдвиг влево выполняется через сдвиг вправо, число сдвигов вправо является дополнением до "64" числа сдвигов влево. Операнд поступает на вход 38, а по входу 33 поступает нулевое значе- 25 ние. Сигнал с выхода 16 поступает на входы управления третькм состоянием четвертого 77 и пятого 78 сдвигателей и разрешает передачу через них информации на дополнительные входы разря- 30 дов соответственно второго 75 и третьего 76 сдвигателей. Входы младших двуз разрядов числа сдвигов (вход 39) подключены к входам управления с числом сдвигов первого 74 и четвертого 77 сдвигателей, входы следующих. двух разрядов числа сдвигов соединены с входами управления числом сдвигов г второго 75 и пятого 78 сдвигателей, входы старших двух разрядов числа сдвигов подключены к управляющим входам числа сдвигов третьего сдвигателя 76.

Блок 11 приближенного деления может реализовать любой быстрый метод приближенного деления, например табличный. К адресным входам таблиц подключаются входы групп старших разрядов делимого и делителя, а на выходе блока под управлением сигнала с выхода 25 устанавливается значение прибли.50 женного частного.

Блок 12 приближенного вычисления корня может реализовать любой быстрый метод определения приближенного значе55 ння корня квадратного (или обратной величины корня), например табличный метод, К адресным входам таблиц подключается вход группы старших разрядов операнда, а на выходах устанавливается под управлением сигнала с выхода

26 приближенное значение корня квадратного (или обратной величины корня).

Блок 8 коррекции частного (фиг, 6) содержит реверсивный двоичный счетчик

79 с запоминанием, выходы которого подключены к входам демультиплексора, образованного дешифратором 80 и восемью шинными формирователями (81-1)(81-8), выходы дешифратора 80 подключены к управляющим входам соответствующих формирователей 81, информационные входы которых соединены с выходами счетчика 79, а выходы являются со-ответствующими выходами разрядов блока 8, счетный вход счетчика 79, вход разрешения и информационный вход дешифратора 80 являются входами соответствующих разрядов входа задания режима блока 8.

Арифметический блок 13 порядков (фиг. 7) содержит регистр 8? общсго назначения, сумматоры-вычитатели 83 и 84, и мультиплексор 85, регистр 86 порядка, схему 87 сравнения с константой, элемент ИЛИ 88, вьг оды 89-92 раэрядов сигнального выхода арифметического блока 13 порядков, входы 93-97 разрядов входа задания режима арифметического блока 13 порядков, причем вход 94 соединен с управляющими входами сумматоров-вычитателей 83 и 84, выход переноса сумматора-вычитателя

83 соединен с первым управляющим входом мультиплексора 85 и является выходом 89 блока 13, выход регистра 86 и вход 96 блока 13 соединены соответсТВрННо с информа щонным входом и Вхо дом разрешения схемы 87 сравнения с константой, выход младшего разряда и второй управляющий вход мультиплексора 85 соединены соответственно с выходом 92 и входом 95 блока 13, перBLIH информациочный выход регистров 82 общего назначения соединен с первым информационным входом первого сумматора-вычитателя 83 и вторым информационным входом второго сумматора-вычитателя 84, информационный вход блока

13 соединен с вторым информационным входом — выходом регистров 82 общего назначения, с вторым информационным входом сумматора-вычитателя 83, с первым информационным входом сумматоравычитателя 84 и выходом регистра 86 порядков, выход результата суьп аторавычитателя 83 соединен прямо и со

15134 сдвигом вправо на один разряд соответственно с первым и вторым информационными входами мультиплексора 85, выход которого соединен с информационным входом регистра 86 порядков, выход результата сумматора-вычитателя

84 соединен с третьим информационным входом мультиплексора 85, выходы равенства разрядов двух операндов первого сумматора-вычитателя 83 подключены к входам элемента ИЛИ 88, выход которого соединен с выходом 91 блока 13, выход мультиплексора 85 подключен к информационному выходу блока 13, 5 вход задания режима регистра 86 порядков соединен с входом 97 блока 13, выход схемы 87 сравнения с константой является выходом 90 блока 13.

Блок 14 микропрограммного управле-, ния (фиг. 8) содержит регистр 98 адреса микрокоманд, узел 99 памяти микрокоманд, регистр 100 микрокоманд, узел 101 регистрации состояния, триггер 102, выходы 103-105 соответствен- 25 но первого, второго управляющих полей и окончания работы регистра 100 микрокоманд, выход 106 трех младших разрядов регистра 98 адреса микрокоманд, выход 107 узла 101 регистрации состо- у яния, выход 108 адреса перехода узла

99 памяти микрокоманд, информационный вход 109 регистра 100 микрокоманд, выход 110 управления узла 99 памяти микрокоманд, регистр 111 команд, выходы

112-114 соответственно микроприказов переноса и полярности знака, третьего управляющего поля регистра 100 микрокоманд, узел 115 памяти команд, причем вход 41 кода операции устройства 4О подключен к информационным входам регистра f 11 управляющий вход которого вместе с входом сброса триггера 102 соединен с входом 40 устройства. Выход регистра 111 соединен с входом узла 5

115 памяти команд, выход которого подключен к первому информационному входу регистра 98, второй информационный вход которого соединен с выходом 108 узла 99, и управляющий вход подключен щ к выходу 110 узла 99, выходы старших разрядов и выходы трех младших разрядов регистра 98 соединены соответственно с входами старших разрядов узла 99 и входом узла 101, выходы 107 узла 101 со-i5> единены с входами трех младших разрядоэ узла 99, выход которого соединен с входом 109 регистра 100, вход 42 устройства соединен с тактовыми входами

43 !О регистров 98, 100 и узла 101, входы

28-32 блока 14 соединены с соответст- вующими входами узла 101.

Узел 101 регистрации состояния (фиг. 9) содержит восемь триггеров (116-1)-(116-8), восемь элементов И (117-1)-(117-8), выход 118, регистр

119, четыре мультиплексора 120-123, элементы ИСКЛЮЧАЮЩЕЕ ИЛИ 124 и 125, два формирователя шин 126 и 127, при» чем первые входы элементов И 117 подключены к соответствующим разрядам выходов 104 регистра 100, а вторые входы — к тактовому входу 42 устройства, выходы элементов И 117 соединены с тактовыми входами соответствующих триггеров 116, информационные входы которых подключены к входам

31 и 32, выходам 72, 61, 60, 59 и 63 и к выходу 118 элемента 125, выход триггера 116-1 соединен с четвертым информационным входом мультиплексора

120, выход триггера 116-2 — с информационным входом мультиплексора 121 и первым входом элемента 124, выход третьего триггера 116-3 — с шестым информационным входом мультиплексора

122, выход триггера 116-4 — с пятым информационным входом мультиплексора 121, выход триггера f16-S - с четвертым и вторым информационными входами мультиплексоров 122 и 123 соответственно, выход триггера f 16-6с четвертым информационным входом мультиплексора 121, выход триггера

116-7 — с вторым и третьим информационными входами мультиплексоров 122 и 123 соответственно, а также с информационным входом формирователя 126, выход триггера 116-8 соединен с вто,:рым информационным входоммультиплек.сора 121> выходы 62, 73, 89, 90, 91 и 92 подключены соответственно к первому, второму, третьему, четвертому, пятому и шестому информационным входам регистра 119, тактовый вход которого соединен с тактовым входом 42 устройства, первый выход (выход первого разряда) регистра 119 подключен к третьему информационному входу муль4 типлексора 120, второй выход — к третьему информационному входу мультиплексо" ра 122, третий выход — к второму ин- формационному входу мультиплексора

120, четвертый выход — к пятому информационному входу мультиплексора 122, пятый выход — к третьему информационному входу мультиплексора 121, а шес- .

11 151344 той выход - к седьмому информационному входу мультиплексора 122, первые информационные входы мультиплексоров

120-122 соединены с выходами разрядов выхода 106, а их управляющие входыс выходами разрядов выхода 103, выходы мультиплексоров 120-122 подключены к выходам 107, первый информационный вход мультиплексора 123 соединен с вы-10 ходом 113, управляющие входы соединены с выходом 114, а выход подключен к входу 67, вторые входы элементов

124, формирователей 126 и 127 соединены с выходами соответствующих разрядов 5 выхода 112, выход элемента 124 подключен к первому входу формирователя шин

127, выход которого соединен с информационным выходом 45 блока 14, выход формирователя шин 126 подключен к вхо-2О ду 38 блока 10 сдвига.

Слово-состояние (фиг. 10) содержит следующие признаки полей, формируемые на соответствующих входах.

Пля поля "28"; "59" - вьмод пере- 25 носа; "60" - выход старшего разряда;

"61" — выход разряда округления; "62"признак нулевого старшего слова; "63" признак равенства мантисс.

Для поля "29": "72" — признак нуле"у» вого операнда; "73" — признак нулевого байта.

Для поля "30": "89" — выход переноса "90" — признак сравнения "91"—

У признак равенства порядков; "92"младший разряд результата.

Для одноразрядных полей: "31"— знак первого операнда; "32" — знак второго операнда; "118" — результат 40 сложения по модулю два знаков операндов.

Микрокоманда (фиг. 11) состоит из следующих полей: поля "15" управления мультиплексором 2; поля "16 управле- 45 ния блоком 10; поля "17" управления блоком 1; поля "18" управления бло.ком 3; поля "19" с признаками: "64"точность операнда (одинарная/двойная);

"65" - Формат операнда (фиксирован,ный/плавающий); "66" — управление сумматорами-вычитателями 47-50; "67"— вход переноса; поля "20" управления регистром 5; поля "21" управления регистром 6; поля "22" управления мультиплексором 7; поля "23" управления блоком 8; поля "24". управления узлом 9; поля "25" управления блоком

11 поля "26" управления блоком 12;

3 12 поля "27" с признаками: 93" - управление регистром 82; "94" - управление сумматорами-вычитателями 83 и 84;

"95" - управление мультиплексором 85;

"96" управление схемой 87; "97"управление, регистром 86; поля «103" управления мультиплексорами 120, 121 и 122; поля "104" - поля маски элементов И 117; поля "105" микроприказа работы устройства; поля "108" — поля адреса следующей микрокоманды; поля

"110" - поля управления регистром 98; поля "112" - поля управления элементами 124, 126 и 127; поля "113" — сигнала входа переноса для блока 4; поля "114" - поля управления мультиплексором 123.

Все операнды для любой операции хранятся в регистрах общего назначения: знаки и мантиссы в блоке 1» поряд ки в регистре 82 блока 13.

Устройство (фиг. 1) работает следующим образом.

На вход 41 устройства поступает код операции, который под управлением сигнала на входе 40 (сигнал на входе 40 одновременно сбрасывает триггер 102) заносится в регистр 111 команд. Код операции на выходах этого регистра определяет адрес узла 115, содержимое соответствующей ячейки памяти которого является начальным адресом микропрограммы. Адрес начальной микрокоманды под управлением тактового сигнала с входа 42 и сигнала с выхода 110 записывается в регистр 98. Три младших разряда с выходов регистра 98 поступают через мультиплексоры 120, 121 и 122 соответственно на адресные входы младших разрядов узла 99 памяти микрокоманд, на старшие адресные входы которого поступает код старших разрядов регистра 98. Спустя время, определяемое временем чтения узла 99, на вторые информационные входы регистра

98 поступает адрес следующей микрокоманды с выхода 108 узла 99. Под управлением сигнала с выхода 107 поле управляющих сигналов с выходов узла 99 записывается в регистр 100 микрокоманд, а адрес следующей микрокомандыв регистр 98. Управляющие сигналы с выхода регистра 100 осуществляют маскирование через элементы записи признаков условий входов 31, 32 и 118 в триггеры 116. Остальные признаки условий в каждом такте записываются в регистр 1 19. Выходы последнего и

143; если 010, то переход к MK 150; если ХХ1 то переход к MK 142 (Х— ,безразличное состояние).

MK 130. Из блока считывается на вход А33 операнд У ° В блоке 10 выполняется сдвиг операнда Y вправо !, на число разрядов, определяемых содержимым регистра 86, которое с выходов 36 регистра 86 через сумматор 83 и мультиплексор 85 поступает с выходов 39 блока 13 в блок 10 на входы числа сдвигов. Результат сдвинутого операнда Y по входу Б34 записывается под, управлением поля "17" в один из регистров группы регистров блока 1.

Выполняется анализ признака "118": если О, то переход к MK 137; если 1, то .переход к MK 131.

МК 131. Мантисса операнда Х и денормализованная мантисса операнда Y читаются (под управлением поля "17") из блока 1 по входам АЗЗ и Б34 соответственно и поступают на входы блока 4. Результат суммы с выходов блока 4 (под управлением поля "19") записывается в регистр 5 (под управлением поля "20"). Порядок операнда Х (под управлением поля "93") поступает из регистра 82 на сумматоры 83 и

84 блока 13, где увеличивается на

"единицу" (под управлением поля "94"). результат записывается через мультиплексор 85 в регистр 86 (под управлением поля "97"). Признаки переноса

"59" блока 4 и "89" блока 13 фиксируются в соответствующих триггерах 116 узла 101 блока 14. Переход к МК 132.

MK 132. Под управлением поля "93" из регистра 82 считывается константа, равная единице, которая с выхода мультиплексора 85 поступает с выходов 39 блока 13 на входы числа сдвигов блока 10, Под управлением поля "20" содержимое буферного регистра 5 поступает по входу А33 на .информационные входы блока 10, где выполняется сдвиг вправо (под управлением поля "16"), и результат с выходов блока 10 по входу Б34 записывается в блок 1 по адре" су результирующей мантиссы. Анализ признаков "59" и "89": если 00, то . переход к MK 133; если 10, то переход к MK 136; если 11, то переход к MK 135.

MK 133. Под управлением поля "20" содержимое буферного регистра 5 по входу АЗЗ записывается в блок 1 (под управлением поля "17") по адресу ре1513443 14 триггеров 116 подключены к информационным входам мультиплексоров 120122, управляющие входы которых, определяемые выходами 103 регистра 100, позволяют осуществлять ветвление в микропрограмме по трем признакам условий одновременно. Микрокоманда, соответствующая окончанию микропрограммы, с помощью сигнала с выхода 105 устанавливает триггер 102 в единичное состояние, при этом выход 43 сигнализирует об окончании работы текущей микропрограммы и готовности выполнить следующую команду. l5

Устройство в процессе выполнения различных арифметических операций работает следующим образом.

Микропрограмма операции вычитания представлена на фиг. 12 и содержит 20 микрокоманды (MK) 128-152.

MK 128. Из регистров считываются мантиссы операндов Х и Y соответственно на входы А33 и Б34, Знаки "31" первого Х и 32" второго Y операндов 25 и результат "118" сложения по модулю два знаков на элементе 125 под управлением разрешающих сигналов "104" через элементы И 117 фиксируются в соответствующих триггерах 116 узла 101 30 блока 14. В блоке 13 признак "89" óïравляет выбором информационного входа мультиплексора 85 и под управлением микроприказа "97" поля "27" результат с выходов мультиплексора 85 записывается в регистр 86. Результат с выходов мультиплексора 85 поступает также на первые входы схемы 87, где сравнивается с константой и формируется признак больше 90, который фикси-40 руется в соответствующем триггере 116 узла 101 блока 14. В случае равенства порядков элемент ИЛИ 88 формирует признак "91 который фиксируется в соответствующем триггере 116. В блоке 45

4 (под управлением микроприказов поля "19") вычисляется разность операндов (Х вЂ” Y), которая записывается в буферные регистры 5 и 6 под управле - -нием микроприказов полей "20" и "21.", В соответствующих триггерах 116 фиксируются признаки "59" переноса, "60" значения старшего значащего разряда . и "63" равенства операндов. Переход к МК 129, . 55

MK 129. Анализ сформированных предыдущей микрокомандой условий "89", "91" и "90": если 000, то переход к

MK 130; если 100, то переход к МК

3 J6 полняется анализ условия "60", зафиксированного в MK 137: если О, то переход к MK 139; если 1, то переход к

MK 134.

MK 139. Под управлением поля "21" содержимое буферного регистра 6 с выходов поступает на информационные входы 38 сдвигателя 77 и дополнительные входы сдвигателя 74 блока 10. На информационные входы сдвигателя 74, соединенные с выходом А33, не поступает информация (что соответствует "нулевому" операнду). На входы 39 блока

10 с выходов мультиплесора 85 блока

13 поступает код числа сдвигов вправо. Под управлением поля "16" в блоке

10 выполняется операция сдвига вправо на число разрядов, которое является дополнением до "64" числа сдвигов влево, и результат по входу Б34 записывается (под управлением поля "17") в блок 1 по адресу результирующей мантиссы. Выполняется анализ признака "72", сформированного в MK 138: если О, то переход к MK 140; если 1, то переход к NK 142.

MK 140. В блоке 113 под управлением поля "27" считываются иэ регистра

ЗО 82 результирующий порядок и двоичный код левого ненулевого разряда мантиссы результата на соответствующие входы сумматора-вычитателя 83, разность с выходов последнего записывается в регистр 86. Признак "89" переноса сумматора 83 фиксируется в соответствующем триггере 116 узла 101 блока 14.

Переход к MK 141.

MK 141. В блоке 13 под управлением поля "27" содержимое регистра 86 записывается по адресу порядка результата в регистр 82. Выполняется анализ признака "89": если О, то переход к

MK 134; если 1, то переход к MK 142.

МК 142. Под управлением поля "17" в блок 1 и в регистр 82 блока 13 (под управлением поля "27") по адресу результата записываются мантисса, знак

Ф и порядок результата, равные нулевому значению. Установка в "единицу" триггера 102 блока 14, Конец операции.

15 151344 зультируюцей мантиссы. Под управлением поля "93" порядок операнда Х записывается по адресу результирующего порядка в регистр 82 блока 13. Переход к MK 134, 5

MK 134. Под управлением поля "112" с выхода 45 формирователя 127 узла

101 блока 14 значение знака операнда

Х по соответствующим разрядам входа

А33 записывается в разряды знака регистра результата блока 1 (под управлением поля "17"). Установка триггера 102 блока 14 в "единицу". Конец операции. 15

NK 135. Я блок 1 (под управлением поля "17") и в регистр 82 блока 13 (под управлением поля "93") по адресам результирующей мантиссы и результирующего порядка записываются "еди- 20 ницы" во всех разрядах, т.е. записывается максимальное значение результата. Переход к NK 134.

МК 136. Выполняется аналогично

МК 134, Дополнительно осуществляется 25 запись порядка операнда Х в регистр

82 блока 13 по адресу результирующего

4 фиксируется в соответствующем триг- 4О гере 116 узла 101 блока 14. Под управлением поля "93" в блоке 13 порядок операнда Х записывается по адресу результируюшего порядка в регистр

82. Переход к МК 138. 45

МК 138. Под управлением поля "20" содержимое регистра 5 по входу АЗЗ поступает на первые информационные входы узла 9, где под управлением поля "24" формируется на выходах 36 двоичный код номера левого ненулевого разряда. В блоке 13 этот код записывается в одном из регистров 82, и в сумматоре 84 (под управлением

55 порядка (под управлением поля "93") °

МК 137. Под управлением поля "17" из блока 1 считываются на входы АЗЗ и

Б34 соответственно мантисса операнда Х. и денормализованная мантисса операнда Y. В блоке 4 (под управлением поля "19") выполняется операция вычитания мантисс операнда Х и денормализованной мантиссы 7, резульгат под управлением полей "20" и "21" записывается в буферные регистры 5 и 6. Признак "60" с выходов 28 блока поля "94") вычисляется дополнение до

"64", результат через мультиплексор

85 записывается в регистр 86. Признак, "72" с выходов 29 узла 9 фиксируется в регистре 119 уэлз 101 блока 14. ВыMK 143. Выполняется аналогично

MK 130. Отличие состоит в том, что на вход АЗЗ иэ блока 1 считывается мантисса первого операнда Х. Выполчяется анализ признака "118": если О, то переход к MK 147; если 1, то переход к MK 144.

15134

17

МК 144. Выполняется аналогично

МК 131. Отличие состоит в том, что на вход А33 из блока 1 считывается мантисса вторичного операнда У, а

МС 5 на входы сумматоров-вычитателей 83 и

84 из регистра 82 блока f3 считывается порядок второго операнда Y. Переход к MK 145.

MK 145. Выполняется аналогично 10

MK f32. Анализ признаков "59" и "89", сформированных в МК 144: если 00, то переход к MK 152; если 10, то переход к МК 146; если 11, то переход к MK 135. !5

МК 146. Выполняется аналогично

МК 136. Отличие состоит в том, что по адресу порядка результата в регистр

82 блока 13 записывается порядок второго операнда Y. 20

МК 147. Под управлением поля "17" из блока 1 на входы А33 и Б34 считываются мантисса второго операнда Y и денормализованная мантисса операнда Х соответственно. Под управлением 25 поля "19" в блоке 4 вычисляется разность этих кодов и результат записывается в буферные регистры 5 и 6 (под управлением полей "20" и "21"). Переход к МК 148. 30

MK 148. Вьптолняется аналогично

NK 138. Анализ признака "60", полученного в MK 147: если О, то переход к МК 149; если 1, то переход к MK 139.

NK 149. Под управлением поля "112" инверсное значение знака операнда Х с выхода 45 формирователя шин 127 узла 101 блока 14 по входу А33 записывается в разряды знака результата регистра блока 1 (под управлением поля 40

"17") ° Установка в "единицу" триггера 102 блока 14. Конец операции.

MK 150. Под управлением поля "17" мантисса первого операнда Х записывается по адресу мантиссы результата в блок 1. Под управлением поля "27" порядок первого операнда Х записывается по адресу порядка результата в .регистр 82 блока 13. Выполняется анализ признаков "118", "89" и "63", сформированных в NK 128: если 000 ° то переход к МК 133; если 100, то переход к MK 144; если 110, то переход к MK 147; если 010, то переход к МК 151; если 101, то переход к

МК 142.

MK 151. Под управлением поля "17 из блока 1 нашины АЗЗи Б34 считываются мантиссы второго Y и первого Х

43 I8 операндов соответственно. Под управлением поля "19" в блоке 4 вычисляется

1 разность мантисс и результат записывается в буферные регистры 5 и 6 (под управлением полей "20" и "21"). Переход к МК 148.

MK 152. Под управлением поля "20" содержимое регистра 5 по.входу А33 записывается по адресу мантиссы результата в блок 1. Под управлением поля "27" порядок второго операнда

Y записывается по адресу порядка результата в регистр 82 блока 13. Переход-.к МК 134..

Микропрограмма операции сложения представлена на фиг. 13 и содержит микрокоманды 153-185.

МК 153. Вьптолняется аналогично MK

128. Переход к МК 154.

МК 154. Выполняется аналогично

МК 129. Анализ признаков "89", "91" и "90". сформированных в MK 153: если 000, то переход к МК 155; если

100, то переход к MK 168; если 010, то переход к MK 176; если ХХ1, то переход к MK 167.

МК 155. Вьптолняется аналогично

МК 130. Анализ признака "118" сформированного в MK 153: если О, то переход к MK 156; если 1, то переход к МК f62.

МК 156. Выполняется аналогично

ИК 131. Переход к МК 157.

МК 157. Выполняется аналогично

MK 132. Анализ признаков "59" и "89", сформированных в MK 156: если 00, то переход к NK 158; если 10, -то переход к NK 161; если Х1, то переход к

MK 160.

MK 158, Выполняется аналогично

MK 133. Переход к MK 159.

MK 159. Выполняется аналогично

МК 134. Конец операции.

МК 160. Выполняется аналогично

МК 135. Переход к MK 159.

МК 161. Выполняется аналогично

MK 136. Конец операции.

МК 162. Выполняется аналогично

МК 137. Переход к МК 163.

МК 163. Выполняется аналогично

NK 138. Анализ признака "60", сформированного в MK 162: если О, то переход к MK 164; если 1, то переход к.

MK 159.

МК 164. Выполняется аналогично

МК 139 Анализ признака "72", сформи» рованного в NK 163: если О, то пере19 15134 ход к MK 165; если 1, то переход к

МК 167.

ИК 165. Выполняется аналогично

MK 140. Переход к MK 166.

MK 166. Выполняется аналогично МК 141. Лнализ признака "89", сформированного в MK 165: если О, то переход к MK 159; если 1, то переход к

MK 167.

NK 167. Выполняется аналогично

ИК 142. Конец операции.

MK 168. Выполняется аналогично

MK 143. Анализ признака "118", сформированного в MK 153: если О, то переход к NK 169; если 1, то переход к ИК 173.

ИК 169. Выполняется аналогично

МК 144. Переход к MK 170.

МК 170, Выполняется аналогично 20

ИК 145. Анализ признаков "59" и "89", сформированных в МК 169: если 00, то переход к HK 172; если 10, то переход к MK 1?1; если Х1, то переход к

МК 159. 25

NK 171. Выполняется аналогично

МК 146. Конец операции.

MK 172 ° Выполняется аналогично

ИК 152. Конец операции.

MK 173. Под управлением поля "17" 30 из блока 1 на входы А33 и Б34 считываются мантисса второго операнда

Y и денормализованная мантисса опе, ранда Х соответственно ° Под управлением поля "19" в блоке 4 вычисляется разность и результат записывается в буферные регистры 5 и б (под управлением микроприказов полей "20" и

"21"). Переход к NK 174.

ИК 174. Выполняется аналогично 40

МК 148. Анализ признака "60", сформированного в NK 173: если О, то переход к NK 164; если 1, то переход к МК .175.

NK 175. Выполняется аналогично . 45

ИК 149. Конец операции.

NK 176. Под управлением поля "27" порядок первого операнда Х записывается по адресу порядка результата в регистр 82 блока 13. Лнализ при- 50 знаков "118", "89" и "63", сформированных в МК 153: если ОХХ, то переход к МК 177; если 100, то переход к МК 179; если 101, то переход к

ИК 172; если 110, то переход к MK 180. 5g

МК 177. Под управлением поля "17" из блока 1 на входы АЗЗ и 834 соответственно считываются мантиссы первого Х и второго Y операндов. Под

43 20 управлением поля "19" в блоке 4 вычисляется сумма мантисс и результат записывается в регистр 5 (под управлением микроприказов поля "20"). Под управлением поля "27" порядок операнда Х в блоке 13 увеличивается на

"единицу" и записывается в регистр 86.

Переход к MK 178.

МК 178. Выполняется аналогично

ИК 132. Анализ признака "89", сформированного в ИК 177: если О, то переход к ИК 158; если 1, то переход к ИК 160.

MK 179. Выполняется в целом аналогично MK 133 за исключением того, что переход к следующей МК осуществляется по анализу признака "60". сформированного в NK 153: если О, то переход к MK 163; если 1, то переход к MK 159.

MK 180. Под управлением поля "17" из блока 1 на входы А33 и Б34 считываются мантиссы второго Y и первого

Х операндов соответственно. Под управлением поля "19" в блоке 4 вычисляется разность мантисс и результат записывается в буферные регистры 5 и 6 (под управлением полей "20" и "21") °

Переход к MK 181.

ИК 181. Под управлением микроприказов поля "20" содержимое буферного регистра 5 передается на вход А33 и затем записывается по адресу мантиссы результата в блок 1 под управлением поля "17". Выполняется анализ признака "60", сформированного в

NK 180: если О, то переход к MK 182; если 1, то переход к ИК 175, МК 182. Выполняется в целом