Устройство для контроля программно-аппаратных средств эвм

Иллюстрации

Показать всеРеферат

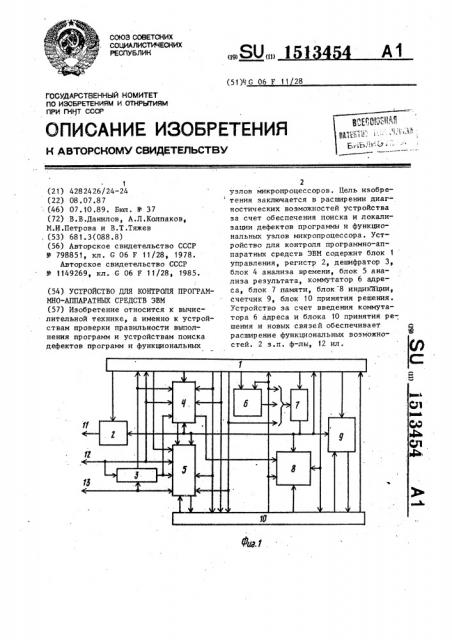

Изобретение относится к вычислительной технике, а именно к устройствам проверки правильности выполнения программ и устройствам поиска дефектов программ и функциональных узлов микропроцессоров. Цель изобретения заключается в расширении диагностических возможностей устройства за счет обеспечения поиска и локализации дефектов программы и функциональных узлов микропроцессора. Устройство для контроля программно-аппаратных средств ЭВМ содержит блок 1 управления, регистр 2, дешифратор 3, блок 4 анализа времени, блок 5 анализа результата, коммутатор 6 адреса, блок 7 памяти, блок 8 индикации, счетчик 9, блок 10 принятия решения. Устройство за счет введения коммутатора 6 адреса и блока 10 принятия решения и новых связей обеспечивает расширение функциональных возможностей. 2 з.п. ф-лы, 12 ил.

СОЮЗ СОВЕТСКИХ

СОЦИАЛИСТИЧЕСКИХ

РЕСПУБЛИК (19> (111

А1 (51)Ч G 06 F !1 28

ОПИСАНИЕ ИЗОБРЕТЕНИЯ

3 р И,1 II

Б> Б !> "— — ——

Н А BTOPCHOMV СВИДЕТЕЛЬСТВУ

СЛ

Сю

4ь

СЛ.

4ь

ГОСУДАРСТВЕННЫЙ КОМИТЕТ

ПО ИЗОБРЕТЕНИЯМ И OTHpbfTHRM

ПРИ ГК1 Т СССР

1 (21) 428 24 26/24-24 (22) 08. 07.87 (46) 07,10.89. Бюл. М- 37 (72) .В.В.Данилов, А.Л.Колпаков, M.È.Ïåòðîâà и В.Т.Тяжев, (53) 681.3(088.8) (56) Авторское свидетельство СССР

Р 798851, кл. G 06 F 11/28, 1978.

Авторское свидетельство СССР и 1149269, кл. G 06 F 11/28, 1985. (54) УСТРОЙСТВО ДЛЯ КОНТРОЛЯ ПРОГРАММН0-АППАРАТНЫХ СРЕДСТВ ЗВМ (57) Изобретение относится к вычислительной технике, а именно к устройствам проверки правильности выполнения программ и устройствам поиска дефектов программ и функциональных

2 узлов микропроцессоров. Цель изобре тения заключается в расширении диагностических возможностей устройства за счет обеспечения поиска и локализации дефектов программы и функциональных узлов микропроцессора. Устройство для контроля программно-аппаратных средств ЭВМ содержит блок 1 управления, регистр 2, дешифратор 3, блок 4 анализа времени, блок 5 анализа результата, коммутатор 6 адреса, блок 7 памяти, блок 8 индик Гции, счетчик 9, блок 10 принятия решения.

Устройство за счет введения коммутатора 6 адреса и блока 10 принятия решения и новых связей обеспечивает расширение функциональных возможностей. 2 з.п, ф-лы, 12 ил.

151345 з

Изобретение относится к вычислительной технике, а именно к устройствам проверки правильности выполнения программ и к устройствам поиска дефектов программ и функци5 ональных узлов микропроцессоров, Целью изобретения является расширение диагностических возможностей устройства за счет обеспечения по- 10 иска и локализации дефектов в контролируемых узлах процессора и программы.

Работа данного изобретения основывается на следующих положениях °

Проверка каждой программы состоит из ряда примеров (идентификаторов) . Крит ери ем для выб ора примеров может быть, например, следующее: совокупность наборов входных переменных 20 должна обеспечивать прохождение по всем ребрам алгоритма, по которому реализована программа, хотя бы два раза ° Используя этот критерий, почти во всех случаях удается обнаружить однократный дефект функционального, предикатного и константного симво" лов, из которых состоит программа.

Pабота устройства в режиме проверки основана на сравнении ..времени вы- 30 полнения программы с заданным промежутком времени и на сравнении результатов выполнения программы с эталонными результатами. Сначала осуществляется анализ времени выполнения программы. Если до истечения заданного промежутка времени на устройство не поступил сигнал об окончании работы программы, то данная ситуация классифицируется как зацикливание, Если фактическое время выполнения программы оказалось меньше расчетного, заданного с учетом определенного допуска, то данная ситуация классифицируется как преждевременное завершение программы. Необходимость допуска объясняется тем, что время выполнения программы зависит от места нахождения микрокоманд, входящих в команду. Например, одна и та же микрокоманда может находиться

50 в арифметико-логическом устройстве или в постоянном запоминающем устройстве в зависимости от того, выполнялась она нли нет в предыдущей команде. Допуск характеризует эти различия для всей программы, Если фактическое время выполнения программы уложилось в заданный допуск, То

4 4 происходит сравнение результатов выполнения программы с эталонными результатами. Если результаты не равньi, то данная ситуация классифицируется как дефект в программе, При равенстве результатов делается вывод об отсутствии дефектов в программе.

B режиме поиска дефектов используется то обстоятельство, что каждая команда программы при своем выполнении активизирует определенные функциональные узлы (ФУ) микропроцессора. Это позволяет каждой команде поставить в соответствие совокупность активизируемых ФУ. В системе команд микропроцессора содержатся команды записи в соответствии ФУ и команды считывания из ФУ. Первая группа команд относится к устанавливающим, а вторая — транслирующим командам. Сопоставив каждой команде микропроцессора входные, выходные ФУ и функцию преобразования информации, также соотнесенную с ФУ,и вьщслив устанавливающие и транслирующие команды, можно сформировать логически завершенные последовательности команд.

Эти последовательности осуществляют передачу информации с преобразованием или без него от входа микропроцессора к выходу и называются подмоделями. Так как вся система команд микропроцессора определяет функционирование управляющего и операционного автоматов, из которых состоит микропроцессор, то эти подмодели покрывают весь мйкропроцессор и обеспечивают полноту диагностирования. Подмодели упорядочиваются по включению на основе совокупности активизируемых ФУ. При этом в качестве первого элемента упорядоченной последо— вательности для теста поиска дефектов (ТПД) берется подмодель с минимальной совокупностью ФУ. Упорядоченная последовательность подмоделей определяет решетчатую модель микропроцессора, описываемого системой команд. Для получения входной тестовой программы подмоцели дополняются данными. В качестве данных могут быть использованы специальные входные наборы, созданные предварительно для тестирования соответствующего ФУ, либо псевдослучайная последовательность.

Если для всех наборов подмодели выходные результаты »е совпадают с

5 15 эталонными, тестирование прекращается и выдается сообщение, позволяющее установйть на каком элементе решетчатой модели произошла ошибка.

В противном случае на следующую подмодель подаются соответствующие тестовые данные и поиск дефектов продолжается. Если тест поиска дефектов прошел до конца без остановки, то индицируется сообщение об отсутствии дефектов.

На фиг.1 представлена схема предлагаемого устройства; на фиг.2схема блока управления; на фиг.3— схема блока анализа времени; на фиг.4 — схема блока анализа результата; на фиг.5 — схема блока принятия решения; на фиг.6 — схема первого узла синхронизации; на фиг.7— схема второго узла синхронизации; на фиг.8 — алгоритм работы устройства в режиме проверки; на фиг.9 — алгоритм работы устройства в режиме поиска; на фиг,10 - схема информации из области проверки, поиска и выходного файла объекта диагностирования, на фиг.11 - фрагмент теста; на фиг.12 — пример, поясняющий прохождение теста в структуре микропроцессора. На фиг.10a-в обозначены:

ЧТ вЂ” число примеров (идентификаторов) в тесте, КЧТ вЂ” метка конца ЧТ, ЧП вЂ” число проверяемых переменных, КПЧ вЂ” метка конца ЧП, ДП вЂ” значение допуска на время выполнения програм, мы, КДП вЂ” метка конца ДП, В — значение расчетного времени выполнения программы, ОК вЂ” область констант, КК вЂ” метка конца ОК, ЭЗ вЂ” эталонные значения выходных переменных, K33метка конца ЭЗ, ВЗ вЂ” значения входных переменных, КВЗ вЂ” метка конца

ВЗ, ОП вЂ” область примера, КП вЂ” метка конца ОП, НВ - метка начала вычислений, HP — метка начала результа тов, P3 — результаты вычисления примера (выходные переменные), КР— метка конца РЗ.

13454 6

45 хронизации, счетчики 16 и 17, дешифратор 18.

Блок 4 анализа времени (фиг.3) содержит элемент ИЛИ 19, триггеры

20-22, элементы И 23-25,счетчик 26, регистр 27, дешифратор 28, блок 29 сравнения.

Блок 5 анализа результата (фиг.4) содержит элементы ИЛИ 30-32, элементы И 33-35, триггеры 36 и 37, блоки. стековой 38 и 39 памяти, элемент

40 задержки, блок 4 1 сравнения.

Блок 10 принятия решения (фиг.5) содержит элементы И 42-48, элементы

HJIH 49-51, элементы 52 и 53 задержки, элемент НЕ 54, триггер 55.

Первый узел 14 синхронизации (фиг.6) содержит кнопки "Поиск" 56, "Проверка" 57 и "Пуск" 58, триггеры

59 и 60, элементы 61-63 задержки, элементы ИЛИ 64-66, элемент И 67.

Второй узел 15 синхронизации (фиг.7) содержит дешифраторы 68 и 69, элемент ИЛИ 70, триггер 71, элементы И 72 и 73, регистр 74.

Блок 1 управления организует работу всех блоков устройства.

С первого выхода блока 1 управления на вход записи регистра 2 выдаются команды разрешения записи значений входных переменных, с третьего выхода блока 1 управления на вход записи блока 5 анализа результатакоманды разрешения записи эталонных значений выходных переменных, с пятого выхода блока 1 управления на вход записи счетчика 9 — команда разрешения записи числа проверяемых переменных, с первой группы выходов блока 1 управления на группу входов разрешения записи блока 4 анализа времени — команды разрешения записи значений расчетного времени выполнения программы и допуска на время выполнения программы, ° с шестого выхода блока 1 управления — команда начальной установки на установочные входы блока 4 анализа времени, блока

55

Устройство для диагностирования программ (фиг.1) содержит блок 1 управления, регистр 2, дешифратор 3, блок 4 анализа времени, блок 5 анализа результата, коммутатор 6 адреса, блок. 7 памяти, блок 8 индикации, счетчик 9, блок 10 принятия решения.

Блок 1 управления (фиг.2) содержит первый 14 и второй 15 узлы син5 анализа результата и блока 10 приниятия решения; с седьмого выхода блока 1 управления сигнал задания режима выдается на входы задания режима блока 4 анализа времени и блока

10 принятия эталонных значений выход-: ных переменных. Затем по сигналам от блока 1 управления из блока 7 памяти в регистр 2 поступает выбор В — значений входных переменных. Выходы ре1513454 гистра 2 соединены с информационными выходами 11 устройства, с которых входные значения последовательно считываются в ОД. Метка КВЗ вЂ” конца об .ласти входных значений — также посту- 5 пает на ОД и служит для него сигналом начала вычислений. Начало вычислений подтверждается поступлением метки Н — начала вычислений (фиг.10в)

10 от ОД на информационные входы 13 устройства. Метка НВ распознается дешифратором 3, который вырабатывает команду начала отсчета времени выполнения программы, поступающую в блок

4 анализа времени. Отсчет времени прекращается только после поступления на входы дешифратора 3 от ОД метки HP — начала результатов, Если расчетное время выполнения програм20 мы истекло, а метка начала результатов еще не принята, то блок 4 анализа времени вырабатывает команду, разрешающую индикацию в блоке 8 индикации сообщения Зацикливание . При по ступлении метки начала результатов дешифратор 3 вырабатывает команду подготовки к приему результатов, ко, торая поступает в блок 5 анализа результата ° Затем в блок 5 анализа результата последовательно записыва30 ются P3 — результаты вычисления данного примера, поступающие от ОД на информационные входы 13 устройства.

Набор результатов завершается меткой КР— конца результатов, по кото- 35 рой дешифратор 3 вырабатывает команду в блок 4 анализа времени, раэре1 шающую сравнение фактического времени выполнения программы со значением допуска. Если фактическое время вы-; 40 полнения программы оказывается меньше допустимой величины, то блок 4 анализа вр емени вырабатывает команду, разрешающую индикацию решения; с седьмого выхода блока 1 управления сигнал задания режима выдается на входы задания режима блока 5 анализа результата, блока 10 принятия решения., на адресный вход блока 7 памяти; со второй группы выходов блока 50

1 управления на группу информационных входов коммутатора 6 адреса выдается информация о текущем номере примера и содержимое счетчика адреса; со второго выхода блока 1 .управления на вход чтения блока 7 памяти выдается команда разрешения считывания; с четвертого выхода блока 1 управления команда разрешения индикации выдается на третий вход разрешения индикации блока 8 индикации и на вход запроса индикации блока 10 принятия решения.

Регистр 2 предназначен для фиксации информации, поступающей на объект диагностирования. С информационных выходов регистра 2 на группу информационных входов объекта диагностирования выдаются значения входных переменных и метка конца входных значений.

Дешифратор 3 пр еднаэ начен для распознавания команд в потоке информации „поступающей от объекта диагностирования. С третьего выхода дешифратора 3 командная информация выдается на входы начала вычислений блока 1 управления и блока 4 анализа времени; с первого и второго выходов дешифратора 3 командная информация выдается на входы начала и конца режима блоков 4 анализа времени и 5 анализа результата.

Блок 4 анализа времени предназначен для анализа времени выполнения программы, С выхода признака сравнения блока 4 анализа времени на вход начала сравнения блока 5 анализа результата выдается сигнал сравнения; с выходов разрешения индикации блока 4 анализа времени йа пер-. вый и второй входы разрешения индикации блока 8 выдаются команды разрешения индикации.

Блок 5 анализа результата предназначен для сравнения результатов прохождения программы с эталонными значениями. С выходов результата сравнения блока 5 анализа результата на информационные входы блока

10 принятия решения выдаются сигналы сравнения (несравнения).

Коммутатор 6 адреса предназначен для реализации обращений к различным областям адресного пространства блока 7 памяти. С выходов коммутатора 6 адреса на группу адресных входов блока 7 памяти выдается адресная информация.

Блок 7 памяти пр едназ начен для ранения диагностической информации.

С выходов блока 7 памяти на информационные входы блока 1 управления выдается число примеров, метки, на информационные входы регистра 2 выдаются значения входных переменных,на

13454

9 15 информационные входы блока 4 анализа времени — значения рассчетного времени и допуска на время выполне" ния программы, на информационные вхо ды блока 5 анализа результата — эталонные значения выходных переменных, на группу информационных входов блока 8 индикации — информация о характере обнаруженных дефектов, на информационные входы счетчика 9— число проверяемых переменных.

Блок 8 индикации предназначен для индикации результатов диагностирования.

Счетчик 9 предназначен для хранения числа проверяемых переменных.

C выхода переполнения счетчика 9 на стробирующий вход блока 10 принятия решения выдается сигнал обнуления счетчика.

Блок 10 принятия решения предназначен для анализа процесса сравнения результатов вычисления примера с эталонными значениями. С выхода останова блока 10 принятия решения на вход останова блока 5 анализа результата выдается команда остановки работы, с тактового выхода блока 10 принятия решения на вычитающий вход счетчика 9 — команда изменения состояния, с выходов продолжения и разрешения счета блока

10 принятия решения на входы продолжения и вычитания блока 1 управления — команды продолжения работы, перехода к следующему примеру, с первого выхода разрешения индикации блока 10 принятия решения команда разрешения индикации выдается на управляющий вход блока 1 управления, на управляющий вход коммутатора 6 адреса, на адресный вход блока 7 памяти, на второй вход разрешения блока 8 индикации, с второ-го выхода разрешения индикации блдка 10 принятия решения на третий вход разрешения индикации блока 8 — . команда разрешения индикации.

Устройство для диагностирования программ (фиг.1) работает следующим образом.

Сначала происходит установка в исходное состояние блока 1 управления, а также блоков анализа времени

4, анализа результата 5, принятия решения 10 по сигналу от блока 1 управления. При этом на управляющий вход коммутатора 6 адреса от блока

5 !

О

25 . 30

10 принятия решения поступает нулевой сигнал, в соответствии с которым коммутатор 6 адреса подключает к группе адресных входов блока 7 памяти группу выходов блока 1 управления. Кроме выходов коммутатора 6 адреса, к группе адресных входов блока 7 памяти подсоединены: первый выход разрешения индикации блока 10 принятия решения, имеющий нулевое состояние после начальной установки, и восьмой выход блока 1 управления, состояние которого определяется выбрачным режимом работы устройства. При нулевом значении восьмого выхода блока 1 управления происходит обращение к области проверки (фиг.10а), а при единичном— к области поиска (фиг.10б) блока

7 памяти. Дальнейшая работа устройства осуществляется по синхронизирующим импульсам, поступающим от объекта диагностирования (ОД) на тактовый вход 12 устройства. Работа устройства в каждом из режимов начинается с осуществления серии операций считывания-записи. С этой целью блок 1 управления каждый раз выполняет следующие действия: выдает адрес считываемой информации, ко" торый поступает через коммутатор

6 адреса на группу адресных входов блока 7 памяти, формирует команду разрешения считывания, поступающую на блок 7 памяти; через время, необходимое для появления информации на выходах блока 7 памяти, блок 1 управления выдает команду разрешения записи в один из блоков устройства.

Рассмотрим работу устройства в каждом из режимов.

Режим проверки (фиг.8) начинается с записи, ЧТ вЂ” числа примеров (фиг,10а) из блока 7 памяти в блок

1 управления. Затем по сигналам от блока 1 управления из блока 7 памяти пройсходит запись констант: ЧПчисла проверяемых переменных в счет чик 9, значений ДП вЂ” допуска на вре- мя выполнения программы и В — рассчетного. времени выполнения программы в блок 4 анализа времени. Затем по сигналам от блока 1 управления иэ блока 7.памяти в блок 5 анализа результата записываются ЭЗ. Если фактическое время выполнения программы укладывается в рамки допуска, то блок 4 анализа времени вырабатывает.

ll

1513 команду, разрушающую последовательное сравнение результатов вычисления примера с эталонными значениями в блоке 5 анализа результата. Данные о совпадении или несовпадении каждой пары сравниваемых величин поступают для анализа в блок 10 принятия решения. Условия анализа сигналов сравнения (несравнения) в блоке 10 принятия решения зависят от выбранного режима работы устройства и определяются состоянием седьмого (восьмого) выходов блока 1 управления. В данном случае единичный сигнал присутствует на восьмом выходе блока 1 управления и задает следующий алгоритм анализа результатов. При несовпадении результата с эталонным значением блок 10 принятия решения вырабатывает команду, разрешающую индикацию ! в блоке 8 индикации сообщения "Ошиб ка в программе". При совпадении результата с эталонным значением блок

10 принятия решения вырабатывает ко1 манду уменьшения на единицу содержимого счетчика 9. Если же все ре1 !. зультаты прохождения примера совпадают с эталонными значениями, счетчик

9, достигнув нулевого состояния, выдает соответствующий сигнал на блок

10 принятия решения, который формирует команду остановки работы блока

5 анализа результата и команду перехода к следующему примеру в блоке

1 управления ° При этом число примеров в блоке 1 управления уменьшается на единицу, и работа устройства повторяется на следующем примере, Когда число примеров в блоке 1 управления достигает нуля, блок 1 управления выдает соответствующую команду, которая поступает в блок 8 индикации, разрешая индикацию соотношения "Дефекта нет" и в блок 10 принятия решения, запрещая дальнейшую работу устройства. ! Б режиме поиска (фиг.9) блок 4 анализа времени не используется, а следовательно, не проиводится и запись значений допуска на время выполнения программы и расчетного времени выполнения программы (фиг,106) .

В остальном порядок записи числа примеров, числа проверяемых переменных, эталонных значений, подачи входных значений на ОД полностью совпадает с аналогичными действиями в ре454

12 жиме проверки. В режиме поиска единичный сигнал, поступающий на блок

5 анализа результата с восьмого выхода блока 1 управления разрешает последовательное сравнение результатов прохождения примера с эталонными значениями сразу же после прихода метки КР— от ОД, Данные о совпадении или несовпадении каждой пары сравниваемых величин поступают в блок 10 принятия решения. При этом единичный сигнал, поступающий на блок 10 принятия решения с второго выхода задания режима блока 1 управления, задает следующий алгоритм анализа результата. При первом же совпадении результата с эталонным значением блок 10 принятия решения вырабатывает команду перехода к следующему примеру в блоке 1 управления. При этом число примеров в блоке 1 управления уменьшается на единицу и работа устройства повторяется на сле25 дующем примере. Когда число примеров в блоке 1 управления достигает нуля, блок 1 управления выдает соответствующую команду, которая поступает в блок 8 индикации, разрешая индикацию сообщения пДефекта нет и в блок 10 принятия решения, запрещая дальнейшую работу устройства.

При несовпадении результата с эталонным значением блок 10 принятия решения вырабатывает команду уменьшения на единицу содержимого счет" чика 9. Если же все результаты решения примера не совпадают с эталонными значениями, то счетчик 9, дойдя до нулевого состояния, выдает соответствующую команду на блок 10 принятия решения.При этом на первом выходе разрешения индикации блока 10 принятия решения появляется единичный сигнал, который поступает на управляющий вход коммутатора 6 адреса, подключая группу адресных входов блока 7 памяти к группе выходов номера примера блока 1 уп5О Равления и на гРуппу адресных входов блока 7 памяти, реализуя тем самым обращение к области номеров, а также на управляющий вход блока 1 управления, инициируя подачу команды разрешения считывания с блока 1 управления на блок 7 памяти, на блок

8 индикации, разрешая индикацию сообщения "Иеисправность", и на группу информационных входов блока 8

l3 15134 индикации от блока 7 памяти. Информация из области номеров блока 7 памяти, соответствующая номеру данного примера, содержит код команды, проверяемой на данном примере, и коды функциональных узлов ОД, задействованных на данной команде.

Блок ". управления (фиг.2) работает следующим образом.

Предварительно выбранный режим работы устройства определяет поступление единичного сигнала на один из двух выходов задания режима — 1РЖ (2РЖ). Работа блока начинается с появления на выходе СБР (сброс первого узла синхронизации 14) единичного сигнала, который поступает на выход

СБР блока, входы сброса второго узла синхронизации 15 и на вход нуля счет- 20 чика 16 адреса, приводя их в исходное состояние. Затем по сигналам, по" ступающим на тактовый вход блока,первый узел 14 синхронизации начинает формировать сигналы в следующей последовательности: ЧТ, Ф1, Ф2. Сигналы

ЧТ вЂ” разрешение считывания и синхронизирующий ф1 формируются с перекрытием, как это необходимо для выполнения операции считывания-записи.

Сначала сигнал ЧТ, поступающий на блок 7 памяти, разрешает считывание с него информации, а затем через время, необходимое для появления сигналов на выходах блока 7 памяти, на второй узел 15 синхронизации поступает сигнал Ф1. Если информация, поступившая от блока 7 памяти на вход второго узла синхронизации 15 классифицируется им как метка, то по сигналу Ф1 она записывается во . второй узел 15 синхронизации и определяет направление подачи следующего сигнала разрешения записи. Если данная информация меткой не признается, то по сигналу Ф1 второй узел

15 синхронизации формирует один из шести возможных сигналов разрешения записи, направление подачи которого

-определяется предварительно принятой меткой. Направление подачи пер50 вого сигнала разрешения записи обусловлено поступлением сигнала СБР на второй узел 15 синхронизаций в начале работы. Затем через время, необходимое для осуществления считывания-записи, сигнал Ф2 с выхода первого узла 14 синхронизации поступает: на вход второго узла 15 син54 14 хронизации как вспомогательный синхронизирующий сигнал и на счетный вход счетчика 16 адреса, увеличивая его содержимое на единицу.

Работа первого узла 14 синхронизации прекращается по сигналу НВ и возобновляется по сигналу "Продолжение". При поступлении на вход ИНД

4 блока 1 управления единичного сигнала обеспечивается безусловное фор" мирование сигнала ЧТ. По сигналу

ЗПЧТ вЂ” запись числа примеров, поступающему от второго узла 15 синхронизации, в счетчик 17 записывается

ЧТ из блока 7 памяти. Содержимое счетчика 17 уменьшается на единицу всякий раз при поступлении сигнала—

СЧП на вычитающий вход. При достижении счетчиком 17 нулевого состояния дешифратор 16, соединенный с выходами счетчика 17, вырабатывает сигнал разрешения индикации ИНД 5, который поступает в блок 8 индикации, разрешая индикацию сообщения "Дефекта нет" и в блок 10 принятия решения, запрещая дальнейшую работу устройства. Информационные выходы счетчиков 17 и 16 адреса как НП— группа выходов номера примера и СЧАгруппа адресных выходов блока 1 управления, поступают в коммутатор

6 адреса.

Блок 4 анализа времени (фиг.3) используется только в режиме про" верки, когда на вход 1РЖ от блока

1 управления поступает единичный сигнал, разрешающий формирование команд ИНД1, ИНД2, на выходах элементов И 24 и 25. В режиме поиска на вход 1РЖ приходит нулевой сигнал. Работа блока 4 анализа времени начинается с поступления на вход

СБР " сброс от блока 1 управления единичного сигнала, который проходя через элемент ИЛИ 19, устанавливает в ноль триггеры 20-22. Затем на информационные входы блока 4 анализа времени от блока 7 памяти поступает ДП вЂ” значение допуска на время выполнения программы, которое записывается в регистр 27 допуска по сигналу ЭРГД вЂ” запись в регистр допуска, приходящему от блока 1 управления. Затем на информационные. входы блока 4,анализа времени от блока 7 памяти поступает ВВ - значение расчетного времени выполнения программа, которое записывается в

151 счетчик 26 времени по сигналу ЭСЧВ— запись в счетчик времени, приходящему от блока 1 управления. Затем на вход НВ от дешифратора 3 посту.,пает единичный сигнал, который уста,навливает в единицу триггер 20.Еди" ,- ница с прямого выхода триггера 20 поступает на вход элемента И 23, разрешая прохождение через него тактовых сигналов от входа ТАКТ на вычитающий вход счетчика 26 времени . Работа счетчика 26 времени прекращается при поступлении от дешифратора

3 сигнала HP, который, проходя через элемент ИЛИ 19, сбрасывает в ноль триггер 20. Затем по сигналу

КР, поступающему от дешифратора 3, в блоке 29 сравнения происходит сравнение содержимого счетчика 26 времени с допуском на время выполнения программы, хранящимся в регистре !

27 допуска. В том случае, когда содержимое счетчика 26 времени не пре вышает величину допуска, блок 29 сравнения вырабатывает единичный сигнал CPBT - сравнение по времени, ко торый поступает в блок 5 анализа ре. зультата. Если же содержимое счетчика 26 времени не укладывается в допуск, то блок 29 сравнения выраба-! тывает единичный сигнал HCPB — несравнение, который устанавливает в единицу триггер 22.Единица с прямого выхода триггера 22, проходя через элемент И 25, как сигнал разрешения идикации ИНД2, поступает в блок 8 индикации и разрешает индикацию со(11 общения Преждевременное выполнение программы". Если сигнал HP так и не поступил, то при достижении счет чиком времени 26 нулевого состояния дешифратор 28, соединенный с группой выходов счетчика, формирует единичный сигнал, который устанавливает в единицу триггер 21. Единичный сигнал с прямого выхода триггера

21, проходя через элемент И 24, как сигнал разрешения индикации ИНД1, поступает на блок 8 индикации и разрешает индикацию сообщения "Зацикливание", Блок 5 анализа результата (фиг,4) работает следующим образом. Сначала на вход СБР†.сброс блока 5 анализа результата — от блока 1 управления подается единичный сигнал, который, проходя через элементы. ИЛИ 31 и 32, сбрасывает в ноль триггеры 36 и 37.

3454

5

Затем по сигналам ЗПЭЗ вЂ” запись эталонных значений, приходящим от блока 1 управления, во второй блок 39 стековой памяти записываются 33, которые поступают от блока 7 памяти.

Затем от дешифратора 3 приходит единичный сигнал HP, который устанавливает в единицу триггер 36. Единица с прямого выхода триггера 36 разрешает прохождение тактовых сигна» лов на вход ЗП.- запись первого блока

38 стековой памяти. По тактовым сигналам в первый блок 38 стековой памяти записываются Р3, которые поступают от объекта диагностирования через информационные входы 13 устройства. Затем от дешифратора 3 приходит единичный сигнал КР, который поступает на первый вход элемента

И 33. В режиме проверки одновременно с сигналом КР на вход CPBT — сравнение по времени — от блока 4 анализа времени должен поступить единичный сигнал, подтверждающий благополучный результат контроля по време-. ни выполнения программы. Проходя через элемент ИЛИ 30,он поступает на второй вход элемента И 33, разрешая прохождение через него сигнала КР., Если в режиме проверки сигнал CPBT не поступил, значит в объекте диагностирования произошло эациклирование, или время выполенния программы не уложилось в допуск. В этом случае работа блока 4 анализа результатов прекращается. В режиме поиска, когда контроль по времени выполнения программы не производится, от блока 1 управления на вход 2 РЖ блока 5 анализа результата постоянно подается единичный сигнал, который, проходя через элемент ИЛИ 30, разрешает прохождение сигнала КР через элемент И 33. С выхода элемента И 33 единичный сигнал устанавливает в единицу триггер 37 и, проходя через элемент ИЛИ 31, сбрасывает в ноль триггер 36, Единичный сигнал с прямого выхода триггера 37 поступает на вход элемента И 35, разрешая прохождение через него тактовых сигналов на входы разрешения считывания блоков 38 и 39 стековой памяти и на вход элемента 40 задержки. При поступлении единичных сигналов на входы ЧТ блоков 38 и 39 стековой памяти результаты решения примера иэ первого блока 38 и эталонные значения из вто- .

17 151 рого блока 39 подаются на входы блока 4 1 сравнения. Через. время, необходимое для формирования сигналов на выходах блоков 38 и 39 стековой памяти, с выхода элемента 40 задержки единичные сигналы поступают на вход РЗС. — разрешение сравнения блока 41 сравнения. По сигналам РЗС на выходах блока 41 сравнения формируются сигналы CPB — сравнение — или

НСР — несравнение, которые поступают в блок 10 принятия решения.

Работа блока 5 анализа результата прекращается при поступлении единичного сигнала ОС вЂ” останов — от блока t0 принятия решения.

Блок 10 принятия решения (фиг.5) подготавливается к работе при поступлении.сигнала СБР - сброс - от блока

1 управления, которым устанавливается в ноль триггер 55. Дальнейшая работа блока 10 принятия решения зависит от режима работы устройства.

В.режиме проверки на вход 1РЖ блока 10 принятия решения от блока

1 управления поступает единичный сигнал, который разрешает прохождение сигналов через элементы И 42 и

44, При поступлении сигнала НСРВнесравйение - от блока 5 анализа результата единичный сигнал, проходя через элемент И 43, устанавливает в единицу триггер 55, и через элементы ИЛИ 50 и задержки 52, как сигнал

ОСТ, подается на блок 5 анализа результата. Единица с прямого выхода триггера 55, как сигнал ИНДЗ вЂ” разрешения индикации, поступает на блок

8 индикации, разрешая индикацию сообщения "Ошибка в программе", При поступлении сигнала CPB от блока 5 анализа результата единица, проходя через элементы И 44 и ИЛИ 51, как сигнап - 1СЧ ПЕР— уменьшение на единицу числа переменных, подается на вычитающий вход счетчика 9. При поступлении сигнала СЧ ПЕР = О от счетчика 9 единица, проходя через элемен-. ты И 42 и ИЛИ 49, поступает как сигнал — 1 СЧ ПР— уменьшение числа примеров, на блок 1 управления и на вход элемента 53 задержки. Затем через время, необходимое для уменьшения числа примеров в блоке 1 управления и определяемое элементом 53 задержки, единичный сигнал поступает на вход элемента И 48. Если в этот момент на вход ИНД 5 от блока 1 уп3454 18 равления поступает нулевой сигнал, то будучи проинвертирован элементом

НЕ 54, формирует на выходе элемента

И 48 единичный сигнал ПРОДЛ - про-, должение, который поступает на блок

1 управления и служит .командой продолжения работы устройства на следующем примера. Если на вход ИНД 5

10 от блока 1 управления поступает единичный сигнал, ноль с выхода элемен та НЕ 54 закрывает элемент И 48, и работа устройства прекращается.

В режиме поиска на вход 2РЖ бло15 ка 3,0 принятия решения от блока 1 управления поступает единичный сигнал, который разрешает прохождение сигналов через элементы И 45и 47.При поступлении сигнала СРВ от блока 5

20 анализа результата единичный сигнал, проходя через элемент И 45, поступа-. ет на входы элементов ИЛИ 49 и 50, С выхода элемента ИЛИ 50 единица, проходя через элемент 52 задержки,как

25 сигнал ОСТ подается на блок 5 ана" лиза результата. С выхода элемента

ИЛИ 49 единица поступает как сигнал

СЧ ПР на блок 1 управления и на вход элемента 53 задержки. С выхода

30 элемента 53 задержки единица поступает на вход элемента И 48, который формирует сигнал ПРОДЛ по тому же принципу, что и в режиме проверки, При поступлении сигнала НСРВ от блока 5 анализа результата единичный сигнал, проходя через элементы И 46 и ИЛИ 51, как сигнал — 1 СЧ ПЕР пода- ется на вычитающий вход счетчика 9.

При поступлении сигнала СЧ ПЕР 0

40 от счетчика 9 единица, проходя через элемент И 47, как сигнал ИНД 4 поступает на блоки 1, 6, 7, 8 устрой:ства, обеспечивая индикацию в блоке

8 индикации. сообщения "Неисправ45 ность с указанием кода команды, проверяемой на данном примере и кодов функциональных узлов объекта диагностирования, задействованных на данной команде.

50 Первый узел синхронизации 14 блока 1 управления (фиг.6) работает следующим образом. Нажатием одной из кнопок "Поиск" 56 (" Проверка" 57) производится выбор режима работы уст55 ройства. После этого с прямого (ин-, версного) выхода триггера 59 единичный сигнал поступает на выхбд 2РЖ (1РЖ) первого узла 14 синхронизации.

Нажатием кнопки "Пуск" 58 осущест19 1513454

20 вляется пуск устройства. При этом единичный сигнал поступает на выход

СБР, на вход элемента 61 задержки, через элемент ИЛИ 65 на вход установки в ноль триггерЫ 60. Затем через время, необходимое для начальной установки всех блоков устройства, и определяемое элементом 61 задержки, единичный сигнал, проходя через элемент ИЛИ 64, устанавливает в единицу триггер 60. Единичный сигнал с прямого выхода триггера 60 по" ступает на вход элемента И 67, разрешая прохождение через него .тактовых сигналов со входа ТАКТ первого узла 14 синхронизации. Тактовые сигналы, проходя через элемент И 67 поступают через элемент ИЛИ 66 на выход ЧТ - разрешение считывания, на вход элемента 62 задержки, Затем через время, определяемое элементом

62 задержки, единичный сигнал поступает на синхронизирующий выход Ф1 и на вход элемента 63 задержки. Время задержки элементы 62 выбирается таким, чтобы сигналы ЧТ и Ф1 следовали с перекрытием. Затем через время, определяемое элементом 63 задержки, единичный сигнал поступает на синхронизирующий выход Ф2 первого узла 14 синхронизации. В процессе работы устройства триггер 60 переключается сигналами НВ или ПРОДЛ, которые проходят через элементы ИЛИ 65 (ИЛИ 64), При этом прекращаемся (возобновляется) формирование сигналов на выходах ЧТ, Ф1, Ф2 узла. Сигнал

ИНД 4, проходя через элемент ИЛИ 66, осуществляет безусловное формирование едининцы на выходе ЧТ, Второй узел 15 синхронизации бло-. ка f управления (фиг.7) работает по следующему принципу. При единичном состоянии триггера 71 в регистр 74 меток заносится информация, определяющая о