Ячейка однородной вычислительной среды

Иллюстрации

Показать всеРеферат

Изобретение относится к автоматике и вычислительной технике и предназначено для применения в устройстве для сжатия двоичных векторов и других системах логической обработки информации. Цель изобретения - повышение быстродействия ячейки за счет сокращения числа элементов в цепи распространения управляющего сигнала. Для достижения цели в ячейку, содержащую синхровход 1, первый 2 и второй 3 информационные входы, логические входы 4-6, первый 7 и второй 8 функциональные выходы, триггеры 9, 11, элементы НЕ 10, 13, 19, элементы И 14, 16-18, элементы ИЛИ 12, 15 с соответствующими связями, введены две новые связи. 2 ил.

„„Я0„„1513471

СОЮЗ СОВЕТСКИХ

СОЦИАЛИСТИЧЕСКИХ

РЕСПУБЛИК

А1 (51) 4 G 06 F 15/20

ОПИСАНИЕ ИЗОБРЕТЕНИЯ

Н А BYOPCHOMY СВИДЕТЕЛЬСТВУ

7(21)

8("4) 2 (x/) (г) (А ) (х„) > (х,) ГОСУДАРСТВЕННЫЙ НОМИТЕТ

ПО ИЗОБРЕТЕНИЯМ И ОТНРЫТИЯМ

ПРИ ГННТ СССР

1 (21) 4336179/24-24 (22) 30, 11.87 (46) 07. 10.89, Бюл. Ф 37 (71) Пензенский политехнический институт (72) В.С.Князьков, Т.В.Волченская, И,В,Бойков и С.Л.Афонин (53) 681.3(088.8) (56) Авторское свидетельство СССР

У 943739, кл. G 06 F 15/20, 1980„.

Авторское свидетельство СССР

М- 1256041, кл. G 06 F 15/20, 15/347, 1985. (54) ЯЧЕЙКА ОДНОРОДНОЙ ВЫЧИСЛИТЕЛЬНОЙ СРЕДЫ (57) Изобретение относится к автома2 тике и вычислительной технике и предназначено для применения в устройстве для сжатия двоичных векторов и других системах логической обработки информации. Цель изобретения — повьппение быстродействия ячейки за счет сокращения числа элементов в цепи распространения управляющего сигнала.

Для достижения цели в ячейку, содержащую синхровод 1, первый 2 и второй 3 информационные входы, логические входы 4-6, первый 7 и второй 8 функциональные выходы, триггеры 9, 11, элементы НЕ 10, 13, 19, элементы И 14, 16-18, элементы ИЛИ 12, 15 с соответствующими связями, введены две новые связи, 2 ил.

3 15134

Изобретение относится к автоматике и вычислительной технике и предназначено для использования в качест. ве решающих полей параллельных про,цессоров, ориентированных на нечис,ленную обработку информации.

- Цель изобретения — повышение быст родействия ячейки за счет сокращения числа элементов в цепи распространения управляющего сигнала. 10

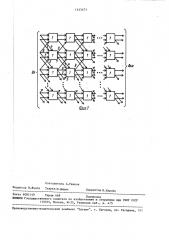

На фиг. 1 представлена схема соединения ячеек в устройство для сжатия двоичных векторов; на фиг. 2 — . функциональная схема ячейки.

Ячейка содержит синхровход 1, пер-11 вый и второй информационные входы 2 и 3, логические входы 4-6, функциональные выходы 7 и 8, триггер 9, элемент НЕ 10, триггер 11, элемент ИЛИ

12, элемент НЕ 13, элемент И 14, эле-2О мент HIIH 15, элементы И 16-18 и элемент НЕ 19.

Функционально ячейка выполняет вычисления следующих логических функций: 25

Z ) = .) (x(х х ч х хз х )

Е 1 = .((х, х Чхз, где Z „и Z — соответственно значения сигналов на выходах 7 и 8 ячейки; х — х — соответственно значения

5 сигналов на выходах 2-6 ячейки.

Устройство, построенное на базе ячеек, обеспечивает выполнение опера ций сжатия двоичных векторов. В про- .

: цессе работы устройства исходный ин, формационный вектор подается на входы

2 и 3 ячейки первого столбца, причем, О

i -й разряд вектора подается на вход

2 (i, 1) ячейки и вход 3 (1 + 1,1) ячейки. Логический вектор подается на входы 4-6 ячеек первого столбца, при-. чем 1 -й разряд вектора подается на 45 вход 6 (1,1)ÿ÷åéêè и вход 6 (1 — 1,1) ) ячейки. В, каждом такте на тактирующйе входы триггеров подается синхроимпульс. В результате двоичные векторы (информационный и логический) переда- р ются в преобразованном виде в соседний справа столбец. Значение i -го разряда логического вектора в j-u столбце при этом определяется значениями (i 1) ro i го (1 + 1) -Го разря дов логического вектора в (j-1)-м столбце; единица переходит в нуль, если (i +1)-й разряд логического вектора в (j-1)-м столбце был разен ну71 4, лю, нуль переходит в единицу, если (i — 1)-й разряд логического вектора в (j-1)-м столбце содержит единицу; в остальных случаях i -й разряд логического вектора передается без изменений, Значение 1 — го разряда информационного вектора в j-м столбце определяется rio следующему правилу. Если i -й раз ряд ло гическо го в ек то ра измен ился с единицы на нуль, то 1-й разряд информационного вектора j-го столбца обнуляется, если i -й разряд логического .вектора изменился с нуля на единицу, то i-му разряду информационного вектора j-го столбца присваивается значение (i -1)-го разряда информационного вектора (j-1)-го столбца, если значение i — го разряда логического вектора в следующий столбец передается без изменения, то значение i — ro разряда информационного вектора в следующий столбец передается без изменений.

Таким образом, в каждом такте в очередной столбец устройства перепиЪ дывается логический вектор, в котором все единицы, под которыми были нули, опустятся на одну строку. Одновременно с этим на одну строку опускаются соответствующие единичным разрядам логического вектора и значения информационного вектора.

В результате через (m-1) такт работы устройства происходит сжатие m-мерного двоичного вектора. Результат сжатия информационного вектора снимается с выхода 7 ячеек последнего столбца устройства.

Поскольку на каждом такте работы устройства информационный и логический векторы передаются в соседний справа столбец ячеек матрицы на вход устройства на каждом такте могут быть поданы следующие пары логических и информационных векторов. Таким образом, устройство реализует конвейерный принцип обработки информации.

В данной ячейке наиболее длинная цепочка последовательно включенных элементов состоит из первого элемента НЕ, четвертого элемента И, второго элемента ИЛИ и третьего элемента НЕ.

Таким образом, время задержки распространения сигнала в наиболее длинной цепочке элементов составляет время

4t где t — время задержки сигнала одним логическим элементом. В результате без нарушения правильности работы устройства допустимо поступле5 151347 ние на синхронизирующий вход ячейки сигнала синхронизации через время

4t, т.е. на время раньше, чем в известной ячейке. Так как для формирования конечного результата преобразования двоичного вектора требуется (m-1) тактов работы устройства, то соответственно предлагаемая ячейка по сравнению с известной будет рабо10 тать на время (m-1) t быстрее, где

m — число строк в матрице ячеек устройства.

Формула изобретения

Ячейка однородной вычислительной среды, содержащая три элемента НЕ, два элемента ИЛИ, четыре элемента И, два триггера, синхровход ячейки соединен с синхроводами первого и второго триггеров, выходы которых соединены с первым и вторым выходами ячейки соответственно, первый информационный вход которой соединен с первым входом первого элемента И, выход которого со-25 единен с первым входом первого элемента ИЛИ, выход которого соединен с входом установки первого триггера и входом первого элемента НЕ, выход которого соединен с входом сброса первого триггера, второй информационный

1 6 вход ячейки соединен с первым входом второго элемента И, выход которого соединен с вторым входом первого элемента ИЛИ, первый логический вход ячейки соединен с первым входом третьего элемента И, выход которого соединен с первым входом второго элемента

ИЛИ, выход которого соединен с входом установки второго триггера и входом второго элемента НЕ, выход которого соединен с входом сброса второго триггера, второй логический вход ячейки соединен с первым входом четвертого элемента И, выход которого соединен с вторым входом первого элемента И ивторым входом второго элемента ИЛИ, третий логический вход ячейки соединен с вторым входом четвертого элемента И и входом третьего элемента НЕ, выход которого соединен с вторым входом третьего элемента И, о тл и ч а ю щ а я с я тем, что, с, целью повышения быстродействия за счет сокращения числа элементов в цепи распространения управляющего сигнала, первый логический вход ячейки соединен с вторым входом второго элемента И, выход третьего элемента НЕ сое- . динен с третьим входом: второго элемента И.

1513471

° ° °

° е °

° ° °

° ° °

Составитель А.Ушаков

Редактор Н.Яцола Техред M.Äèäûê Корректор Н. Король

Заказ 6081/49 Тираж 668

ЦНИИПИ Государственного комитета по изобретениям и открытиям при ГКНТ СССР

113035, Москва, Ж-35, Раушская.наб., д. 4/5 производственно-издательский комбинат "Патент", г. Ужгород, ул. Гагарина, 101