Сигнализатор совпадения фаз

Иллюстрации

Показать всеРеферат

Изобретение относится к измерительной технике и может быть использовано в фазометрах и устройствах, где требуется совмещение электрического и механического нулей датчиков фазовращательного типа. Цель изобретения - расширение области применения - достигается путем обеспечения сигнализации совпадения фазы измеряемого напряжения с произвольно заданной фазой опорного напряжения при одновременном исключении необходимости настройки устройства в процессе перехода к измеряемым сигналам другого уровня. Сигнализатор совпадения фаз содержит компараторы 1 и 2, формирователь 3 импульсов, блок 4 D<SB POS="POST">T</SB>- триггеров, блоки 5 и 7 индикаторов, кодовый наборный блок 6, генератор 8 импульсов, счетчик 9, сумматор-вычитатель 10, постоянный запоминающий блок 11. При эксплуатации устройства не требуется осуществлять настройку пороговых уровней грубой и точной зон. 3 ил.

СОЮЗ СОВЕТСКИХ

СОЦИАЛИСТИЧЕСНИХ

РЕСПУБЛИК (д) 4 С 01 R 25/00

ОПИСАНИЕ ИЗОБРЕТЕНИЯ

К А ВТОРСКОМУ СВИДЕТЕЛЬСТВУ

2 ния — достигается путем обеспечениМ сигнализации совпадения фазы измеряемого напряжения с произвольно заданной фазой опорного напряжения при одновременном исключении необходимости настройки устройства в процессе перехода к измеряемым сигналам другого уровня. Сигналиэатор совпадения фаз. содержит компараторы 1 и 2, формирователь 3 импульсов, блок 4

D -триггеров, блоки 5 и 7 индикаторов, кодовый наборный блок 6, генератор 8 импульсов, счетчик 9, сумматорвычитатель 10 постоянный запоминающий блок 11. При эксплуатации устройства не требуется осуществлять настройку пороговых уровней грубой и точной зон. 3 ил.

ГОСУДАРСТ8ЕННЫЙ КОМИТЕТ

ПО ИЗОБРЕТЕНИЯМ И ОТНРЫТИЯМ

ПРИ ГКНТ СССР

1 (21) 4343441/24-21 (22) 14.12.87 (46) 15.10.89. Бюл. М 38 (72) В.Н.Вавилов, Е.С.Вальшонок и А.С.Сигалов (53) 621.317.373(088.8) (56) Авторское свидетельство СССР

У 602880, кл. С 01 R 25/00, 1979

Авторское свидетельство СССР

У 1195253, кл. G 01 R 25/00, 1985. (54) СИП1АЛИЗАТОР СОВПАДЕНИЯ ФАЗ (57) Изобретение относится к измерительной технике и может быть исполь" зовано в фаэометрах и устройствах, где требуется совмещение электрического и механического нулей датчиков фазовращательного типа. Цель изобретения — расширение области примене0

„„SU„„151512О А1 мости настройки устройства при переходе к измеряемым сигналам другого уровня.

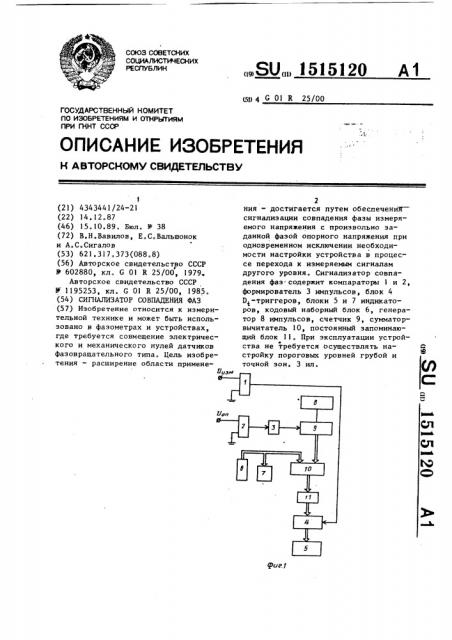

На фиг.1 приведена схема сигнализатора совпадения фаз; на фиг.2— пример выполнения блоков триггеров и индикаторов (4, 5); на фиг. 3 — диаграммы работы сигнализатора.

° Сигнализатор содержит компараторы 1 и 2, формирователь 3 импульсов, блок 4 D<-триггеров, первый блок 5 индикаторов, кодонаборный блок 6,второй блок 7 индикаторов, генератор 8 импульсов, счетчик 9, сумматор-вычитатель 10 и постоянный запоминающий блок 11, при этом первые входы первого и второго компараторов 1 и 2 соединены соответственно с входными шинами опорного и измеряемого напряжений, вторые их входы подключены к шине нулевого потенциала, выход первого компаратара 2 через формирователь

3 импульсов соединен с установочным входом счетчика 9, выход второго ком15

3 l 515120

Изобретение относится к измерительной технике и может быть использовано в фазомвтрах и устройствах, где требуется совмещение электричес5 кого и механического нулей датчиков фазовращательного типа.

Целью изобретения является расши рение области применения путем обеспечения сигнализации совпадения фа- 10 зы измеряемого напряжения с произвольно заданной фазой опорного напряжения с одновременным исключением необходи.—

Компаратор 2 в момент положительного перехода входного (опорного) напряжения через нулевой уровень вырабатывает импульс, передний фронт которого совпадает с нулевой фазой опорного напряжения. Формирователь 3 импульсов вырабатывает по этому фронту короткий импульс, сбрасывающий счетчик 9 в нулевое состояние. Частота генерации генератора 8 импульсов и разрядность счетчика 9 выбраны таким, чтобы переполнение счетчика происходило за интервал времени, равный периоду опорного напряжения (например, если частоты опорного и измеряемого сигналов равны f а разрядность о счетчика 9 — и то частота генерации

Э л генератора 8 должна быть fo 2 ).

При выполнении этого условия состояние счетчика 9 с точностью до выбранного уровня квантования, определяемого разрядностью счетчика 9, соответствует фазе опорного напряжения.

Кодонаборный блок 6 предназначен для задания значения фазы опорного напряжения, о совпадении с которой нулевой фазы измеряемого напряжения должно сигнализировать устройство.

Кодонабарный блок 6 может быть выполнен, например, на тумблерах. Совокупность выходных сигналов кодонаборного блока 6 характеризует двоичный код этой фазы, отображаемый вторым блоком 7 индикации„ Одновременно этот код поступает в качестве вычитаемого на второй вход сумматорапаратора 1 соединен с тактовыми входами всех триггеров блока 4 Dg-триггеров, выходы которых подключены соответственно к индикаторам первого блока 5.индикаторов, выходы кодонаборного блока Ь соединены с входами соответствующих индикаторов второго блока 7 индикаторов и вторыми входами сумматора-вычитателя 1О, первые входы которого соединены с выходами соответствующих разрядов счетчика 9, счетный вход которого подключен к выходу генератора 8 импульсов, выход сумматора-вычитателя 10 соединен с адресным входом постоянного запоминающего блока 11 (в дальнейшем — ПЗБ), выходы которого соединены с соответствующими информационными входами триггеров блока 4 D -триггеров.

Сигнализатор совпадения фаз работает следующим образом.

Рассмотрим, как меняется в течение периода опорного напряжения иразрядный результат вычитания из кода счетчика 9 (А) кода кодонаборного блока 6 (В), для чего рассмотрим коды разности чисел А и В при изменении одного из них (А) ат меньших значений до больших, например, в диапазоне трех младших разрядов. Для вычитания кода В из кода А необходима код В преобразовать в дополнительный код, для чего его надо инверсировать и прибавить единицу младшего разряда, после чего сложить кад числа А и дополнительный код числа В. Все операции при этом осуществляем в и-разрядвычитателя 10. На первый вход сумматора-вычитателя 10 поступает линей40 но-ступенчато изменяющийся код фазы опорного напряжения с выходов разрядов счетчика 9.

5 151512 ной сетке. Возникающий. при этом перенос в (п+1)-й разряд теряется.

Именно по такому алгоритму работает и-разрядный сумматор-вычитатель

10 сигналиэатора.

Допустим, что разрядность счетчика 9, сумматора 10 и кодонаборного блока 6 равна 8. Тогда коду нулевой фазы соответствует код 00000000, коду 180 — код 10000000, коду 90 код 01000000, коду 45 — код 00100000 и так далее.

Допустим, что в кодонаборном блоке

6 установлен код 01100000, что соот- 15 о ветствует фазе 135 (код числа В).

Дополнительный код числа В имеет вид

10011111

+I

10100000 20

Рассмотрим текущие разности А-В (см.таблицу).

0 6 момент прихода нулевой фазы измеряемого напряжения приводит к свечению соответствующего светодиода блока 5.

Пусть светодиод D соответствует младшему разряду выходного слова, а

D> — старшему. Все светодиоды D -0 в таком случае светятся, когда несовпадение фаз опорного и измеряемого напряжений не превышает единицы младшего разряда п-разрядного (в нашем примере — 8-разрядного) кода.

В ячейки с адресами 00000001 и

11111110 записываются нули в разрядах выходного слова х>, х, x а в разрядах х — единицы. Следовательно, при выборе этих ячеек, светятся светодиоды D> - D<, à D не светится, при этом регистрируется ситуация,когда несовпадение фаз опорного и измеряемого напряжений не превышает единицы второго разряда, В ячейках с адресами 00000010 и 1111)100, 00000011 и

Коды разности

А-В (адреса, ПЗБ) Коды числа А (счетчика 9) Величина зоны отличия

Таблица помогает понять принцип программирования ПЗБ 11 (ПЗБ 11 может быть выполнен, например, на основе микросхем серии 541PTI по бКО

347236ТУЗ. 1 корпус микросхемы позволяет построить ПЗБ 11 на 256 4-разрядных слов). Дрпустим, что в ячейки с адресами Illlllll и 00000000 записываются нули во всех разрядах выходного слова, Используются, например, упомянутые микросхемы 541РТ4.

Допустим, что нулевое значение разряда в выходном слове ПЗБ 11 в

01011001

01011011

01011)00

01011101

01011111

01100001

01100011

01100101

11100111

1 111 1001

1111101 0

11111011

11111101

11111111

00000001

00000011

00000101

00000111

-8

-7

-6

-5

-4

-3

-2

-l

+1

+2 л3

+4

+5

+6

50 позволяет сделать вывод, что абсолютная величина разности чисел А и В не превышает величины 2 "

Очевидно, что, увеличив раз рядность выходного слова ПЗБ 11, например, до 8 разрядов, а глубину памяти, например, до 2 ячеек, можно

/3 оперировать с 12-разрядными словами25

11111101 в разрядах х и х. записываются нули, а в разрядах х, и х - единицы. При выборе этих ячеек светятся светодиоды D y и 0,, à D, и D не светятся, регистрируя, что несовпадение фаз не превышает единицы третьего разряда. В ячейки с адресами

00000100 11111000

00000101 11111001

00000110 11111010

00000411 11111011 в разряде х записываются нули, а в разрядах х, х, и х — единицы. При выборе этих ячеек светится светодиод

D, а светодиоды Р, D, и D не светятся, регистрируя, что несовпадение фаэ не превышает единицы четвертого разряда.

При таком программировании ПЗБ 11 легко находят адгеса ячеек, подлежащих программированию: анализируя код разности, .видим, что анализ разности на эквивалентность К старших разрядов, т.е. проверка логического условия л-3 К и-к " Il-i X n- n-3 ° ° в к

1515120

° n

arcsin -- —, где U„дрейф порогового уровня; U „, амплитуда опорного или измеряемого напряжения. НаприMep, U z = l 0 В, U„« =1 — 10 В. Тогда ошибка выделения нуля для крайних значений входных напряжений равна соответственно 10 — 10 рад или 220 угловых секунд, т.е. пренебрежимо мала для большинства применений.

Формула изобретения

Сигналиэатор совпадения фаз, содержащий формирователь импульсов, первый блок индикаторов, блок D — . триггеров и первый и второй компараторы, первые входы которых соединены с входными шинами устройства, а вторые входы соединены с шиной нулевого потенциала, выход первого компаратора соединен с входом формирователя импульсов, выходы блока О+-триггеров соединены с входами первого блока индикаторов, отличающийся тем, что, с целью расширения области применения за счет обеспечения сигнализации совпадения фазы измеряемого напряжения с произвольно заданной фазой опорного напряжения с одновременным исключением необходимости настройки устройства при переходе к измеряемым сигналам другого уровня, в него введены кодонаборный блок, второй блок индикации, генератор импульсов, счетчик, сумматор-вычитатель и постоянный запоминающий блок, при этом выход формирователя импульсов соединен с установочным входом счетчика, выход генератора импульсов соединен со счетным входом

15 сче.личика, выходы разрядов счетчика соединены с первыми входами сумматора-вычитателя, выходы разрядов кодонаборного блока соединены с вторыми входами сумматора-вычитателя и поразрядно с входами второго блока индикаторов, выход второго компаратора соединен с тактовыми входами блока

Dg-триггеров, информационные входы которых соединены поразрядно с вы.—

25 ходами постоянного запоминающего блока, адресные входы которого подключены поразрядно к выходам сумматоравычитателя.

2 д

Составитель М.Катанова

Редактор А.Маковская Техреду.Олийнык Корректор С.Шекмар

Заказ 6273/44 Тираж 714 Подписное

ВНИИПИ Государственного комитета по изобретениям и открытиям при ГКНТ СССР

113035, Москва, Ж-35, Раушская наб., д. 4/5

Производственно-издательский комбинат "Патент", г. Ужгород, ул. Гагарина, 101