Цифровой многофазный генератор

Иллюстрации

Показать всеРеферат

Изобретение относится к радиотехнике и связи и может быть использовано в качестве образцового источника периодических сигналов любой формы с изменяющимися амплитудой и фазой по заданному закону. Цель изобретения - расширение функциональных возможностей путем обеспечения независимой модуляции каждого из N генерируемых сигналов. Для достижения цели в устройство введены задатчик 3 коэффициентов деления, N управляемых делителей 4 частоты, N дополнительных счетчиков 5. Коэффициент деления делителей 4 устанавливается с помощью задатчика 3. Изменяющиеся с различной частотой двоичные коды с выходов счетчиков 5 поступают на соответствующие входы задатчика 6 фазовых модуляций и соответствующие входы задатчика 13 амплитудных модуляций, на выходах которых двоичные коды изменяются по заданному закону, что приводит к независящей (раздельной) модуляции выходных сигналов по фазе и/или амплитуде с различной частотой. 1 ил.

СОЮЗ СОВЕТСКИХ

СОЦИАЛИСТИЧЕСКИХ

РЕСПУБЛИК (51) 4 Н 03 В 19/00

ОПИСАНИЕ ИЗОБРЕТЕНИЯ

К ABTOPGHOMV СВИДЕТЕЛЬСТВУ

ГОСУДАРСТВЕННЫЙ КОМИТЕТ

ПО ИЗОБРЕТЕНИЯМ И ОТКРЫТИЯМ

ПРИ ГКНТ СССР

1 (21) 4348894/24-09 (22) 23.12.87 (46) 15. 10. 89. Ьюл. у 38 (7 1) Омский институт инженеров железнодорожного транспорта (72) А.Н.Захаренко, А.В.Парамэин и В.Г.Шахов (53) 621.373.42(088,8) (56) Авторское свидетельство СССР

Р 1427551, кл. Н 03 В 19/00, 14.10.86. (54) ЦИФРОВОЙ ИНОГОФАЗНЫЙ ГЕНЕРАТОР (57) Изобретение относится к радиотехнике и связи и может быть использовано в качестве образцового источника периодических сигналов любой формы с изменяющимися амплитудой.и фазой по заданному закону. Цель изобретения — расширение функциональных воз„„80„„1515337 А1

2 можностей путем обеспечения независимой модуляции каждого иэ N генерируемых сигналов. Для достижения цели в устройство введены эадатчик 3 коэффициентов деления, N управляемых делилителей 4 частоты, N дополнительньм счетчиков 5. Коэффициент деления делителей 4 устанавливается с помощью эадатчика 3. Изменяющиеся с различной частотой двоичные коды с выходов счетчиков 5 поступают на соответствующие входы задатчика 6 фазовых модуляцией и соответствующие входы задатчика 13 амплитудных модуляций, на выходах которых двоичные коды изменяются по заданнсму закону, что приводит к независящей (раздельной) модуляции выходных сигналов по фазе и/нли амплитуде с различной частотой.1 ил.

1515337

Изобретение относится к радиотехнике и связи и может быть использовано в качестве образцового источника периодических сигналов любой формы

5 с изменяющимися амплитудой и фазой по заданному закону.

Целью изобретения является расширение функциональных возможностей путем обеспечения независимой модуляции каждого иэ N генерируемых сигналов.

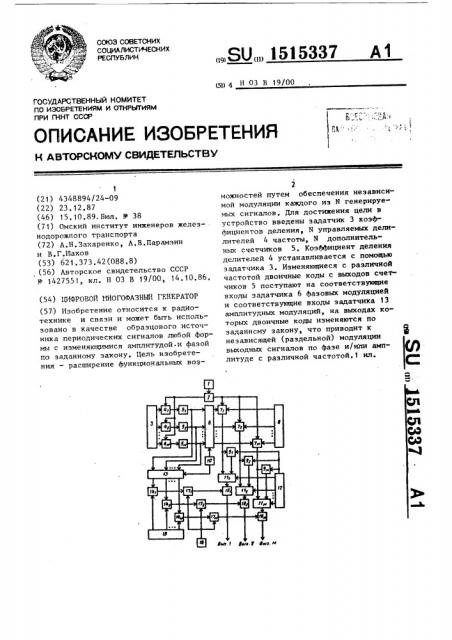

На чертеже представлена структурная электрическая схема цифрового многофаэного генератора. 15 Цифровой многофазный генератор содержит опорный генератор 1, счетчик 2, задатчик 3 коэффициентов деления, первый, второй,..., N-й управляемые делители 4,,4,...,4,„ частоты, первый, 20 второй,..., N-й дополнительные счетчики 5„,5,,...,5ц, задатчик 6 фазовых модуляций, первый, второй,...,N-й сумматоры 71,7 ... °,7, задатчик 8 фазовых сдвигов, первый, второй,...,N-й 25 блоки 9,,9 . ..9„, сравнения кодов, задатчик 10 режимон, первый, второй...

N-й блокп 11„,11 .. .,11„ оперативного запоь|инаншя, задатчик 12 формы сигналов, эадатчик 13 амплитудных 30 модуляций, первый, второй. ..N-й дополн1ГГельные сумматоры 14 „14 °, 14, задатчик 15 амплитуд, первый, )! Э второй,...,N-й цифроаналоговые преобразователи 16„,16,..., 16 „, первый, второй,...,N-й дополнительные цифроаналоговые преобразователи 17„,17 . ° .,17 „ и задатчик 18 масштаба.

Цифровой многофазный генератор работает следующим образом. 40

Последовательность импульсов поступает с выхода опорного генератора 1 на счетный вход счетчика 2.Изменяющийся двоичный код поступает на первые входы первого, второго,..., N-ro сумматора 71,7,...,7, на вторые входы которых с соответствующих вьвсодов задатчика 8 подаются постоянные двоичные коды, обеспечивающие относительный фазовый сдниг между ны- 50 ходными сигналами. В задатчике 12 эаписань1 коды мгновенных значений одного периода нескольких видов сигналов. Зт1л коды мгновенных значений требуемой формы сигнала переписываются н.первьп», второй,...,N-й блоки

11,,11,...,11„ по соответствующим адресам, коды которых с адресного выхода эадатчика 12 поступают на вторые входы первого, второго, ° .., N-го блоков 9,,9,...,9„. При сонпадении кода адреса на адресном входе первого, второго,...,й"го блоков 11 „ 11 ...,11„ с кодом адреса на адресном выходе задатчика 12 на выходе соответственно первого, второго,...,N-го блоков 9„,9,...,9„ формируется импульс записи. Формирование выходных сигналов осуществляется путем циклического считывания записанной в первом, втором,...,N-м блоках 11,,11

11ц информации и последующего преобразования ее н аналоговую форму на первом, втором,...,N-м цифроаналоговых преобразователях 16,,16,,...,16 >.

Амплитуда выходных сигналов занисит от напряжения на выходах первого,нторого,...,N-го дополнительных цифроаналоговых преобразователей 17,,17 ...,17, на информационные входы коl торых поступают двоичные коды с .выходов первого, второго,...,N-го дополнительных сумматоров 14,,14,, ...,14,„, на опорные входы подается напряжение с выхода задатчика 18.

На первые входы первого, второго,..., N-ro дополнительшлх сумматоров

14, 14 . .., 14 „ поступают постоянные двоичные коды с соответствующих выходов задатчика 15, Включение задатчика 6 и задатчика 13 осуществляется с помощью эадатчика 10. Последовательность импульсов с дополнительного вьгхода счетчика 2 поступает на счетные входы первого, второго, ...,N-ro управляемых делителей 4,, 4,...,4„ коэффициент деления которых устанавливается с помощью задатчика 3.

Изменяющиеся с различной частотой двоичные коды с выходов первого,второго,...,N-го дополнительных счетчиКоВ 5 >5 <> 5 „ поступают на соответствующие входы эадатчика 6 и соответствующие входы задатчика 13, на выходах которых дноичные коды изменяются по заданному закону, что приводит к независящей (раздельной) модуляции выходных сигналов по фазе и/или амплитуде с различной частотой.

Формула изобретения

Цифровой многофазный генератор,содержащий последовательно соединелные опорный генератор и счетчик, первый, второй, ..., N-сумматоры, первый, второй,...,N-й блоки оперативного эапо15! 5337

Составитель IO.Ìàêñèìîâ

Техред М,Моргентал Корректор С "ерни

Редактор А.Лежнина

Заказ 6293/55 Тираж 884 Подписное

ВНИИПИ Государственного комитета по изобретениям и открытиям при ГКНТ СССР

113035, Москва, Ж-35, Раушская наб., д. 4/5

Производственно-издательский комбинат "Патент", г.ужгород, ул. Гагарина,!01 минания, первый, второй,...,N-A блоки сравнения кодов, первый, второй, ...,N-й цифроаналоговые преобразователи, первый, второй,...,N-й дополнительные сумматоры, первый, второй,..., N-й дополнительные цифроаналоговые преобразователи, эадатчик фазовых модуляций, задатчик фазовых сдвигов, задатчик формы сигналов, задатчик амп-1р литуднь6с модуляций, задатчик амплитуд и задатчик масштаба, причем выход счетчика соединен с первыми входами первого, второго,...,N-ro сумматоров, выходы которых соединены с первыми 15 входами соответственно первого, второго, ° ..,N-ro блоков сравнения кодов и с адресными входами соответственно первого, второго, N-го блоков оперативного запоминания, первый, второй, 20 ...,N-ый выходы эадатчика фазовых сдвигов соединены с вторыми входами соответственно первого, второго,..., N-го сумматоров, третьи входы которых соединены с соответствующими вьгко-25 дами задетчика фазовых модуляций, первый, второй, ° ..,N-й информационные выходы задатчика формы сигналов соединены с информационными входами соответственно первого, второго;..., 3p

N-ro блоков оперативного запоминания, входы записи которых соединены с выходами соответственно первого, второго, N-го блоков сравнения кодов, адресный выход задатчика формы сигналов соединен с вторыми входами перво35 го., второго,...,N-ro блоков сравнения кодов, выходы первого, второго, .,,,N-ro блоков оперативного запоминания соединены с информационными Вхо 40 дами соответственно первого, второго,...,N-го цифроаналоговых преобразователей, опорные входы которых соединены с выходами соответственно первого, второго,...,N-ro дополнительных цифроаналоговых преобразователей, первый, второй,...,й-й выходы задатчика амплитуд соединены с первыми входами соответственно первого, второго,...,N-го дополнительных сумматоров, вторые входы которых соединены с соответствующими выходами задатчика амплитудных модуляций, выходы первого, второго,...,N-го дополнительных сумматоров соединены с информационными входами соответственно первого, второго,...,N-го дополнительньж цифроаналоговых преобразователей, опорные входы которых соединены с выходом эадатчика масштаба, управляющий вход задатчика фазовых модуляций соединен с первым выходом задатчика режимов, второй выход которого соединен с управляющим входом задатчика амплитудных модуляций, отличающийся тем, что, с целью расширения функциональных возможностей путем обеспечения независимой модуляции каждого иэ N генерируемых сигналов, введены задатчик коэффициентов деления, перный,второй,...,N-й управляемые делители частоты и первый, второй,...,N-й дополнительные счетчики, выходы которых соединены с соответствующими входами задатчика фазовых модуляций и соответствующими входами эадатчика амплитудных модуляций, первый, второ,N-й выходы задатчика коэффициентов деления соединены с информационными входами соответственно первого, второго, ...,N-го управляемых делителей частоты, выходы которых соединены со счетными входами соответственно первого, второго. ° .N-го дополнительных счетчиков, счетные входы первого, второго,...,й-го управляемых делителей частоты соединены с дополнительным выходом счетчика.