Устройство дуплексной передачи и приема сигналов

Иллюстрации

Показать всеРеферат

Изобретение относится к электросвязи. Цель изобретения - повышение помехоустойчивости за счет компенсации эхо-сигналов. Устройство содержит входной согласующий блок 1, коммутатор 2, два ЦАП 3, 11, АЦП 4, г-р 5, два блока памяти 6, 10, формирователь последовательности 7, вычитатель 8, сумматор 9. Для достижения цели в устройство введены сумматор 12, четыре регистра 13-15, 18, счетчик 16, блок 17 адресации и элемент И 19. При дуплексной передаче происходит три одновременно протекающих процесса: 1 процесс - запись суммы отсчетов передаваемых эхо-сигналов и принимаемых сигналов П процесс - расчет оценки эхо-сигнала, полученный в результате адаптации под параметры канала связи Ш процесс - запоминание рассчитанных оценок эхо-сигнала, компенсация их в суммарном стечении и преобразование в аналоговый вид принимаемого сигнала. Таким образом, в одной полосе частот организована дуплексная передача сигналов, компенсация сигналов своего передатчика на входе приемника и выдача данных сигналов потребителю. 2 з.п. ф-лы, 3 ил.

СОЮЗ СОВЕТСКИХ

СОЦИАЛИСТИЧЕСКИХ

РЕСПУБЛИК (191 (11> (А(1 4 Н 04 Ц 1/52

ОПИСАНИЕ ИЗОБРЕТЕНИЯ

ГОСУДАРСТВЕННЫЙ КОМИТЕТ

ПО ИЗОБРЕТЕНИЯМ И ОТКРЫТИЯМ

ПРИ П.(НТ СССР

К АВТОРСКОМУ СВИДЕТЕЛЬСТВУ (21) 4344039/24-09 (22) 15.12.87 (46) 15.10.39. Бюл. N 38 (71) Новосибирский электротехнический институт связи им. Н.Д.Псурцева (72) В.Б.Малинкин (53) 621.393.3 (088.8) (56) Авторское свидетельство СССР

N" 1133675, кл, H 04 В 1/52, 1983. (54) УСТРОЙСТВО ДУПЛЕКСНОЙ ПЕРЕДАЧИ

И ПРИЕМА СИГНАЛОВ (57) Изобретение относится к электросвязи. Цель изобретения - повышение помехоустойчивости за счет компенсации эхо-сигналов. Устр-ао содержит входной согласующий блок 1, коммутатор 2, два ЦАП 3, 11, АЦП.4, г-р 5, два блока памяти 6, 10, формирователь последовательности 7, вычитатель 8, 2 сумматор 9. Для достижения цели в устр-во введены сумматор 12, четыре регистра 13-15, 18, счетчик 16, блок

17 адресации и элемент И 19. При дуплексной передаче происходит три одновременно протекающих процесса: I процесс - запись суммы отсчетов передаваемых эхо-сигналов и принимаемых сигналов; II процесс - расчет оценки эхо-сигнала, полученный в результате адаптации под параметры канала связи; III процесс - запоминание рассчитанных оценок эхо-сигнала, компенсация их в суммарном стечении и преобразование в аналоговый вид принимаемого сигнала. Т.о., в одной полосе частот организована дуплексная передача сигналов, компенсация сигналов своего передатчика на входе приемника и выдача данных сигналов потребителю. 2 з.п. ф-лы, 3 ил.

Работу устройства можно разделит ь на процесс адаптации под параметры канала связи и процесс дуплексной передачи информации.

Процесс адаптации под параметры канала связи заключается в следующем.

Сразу после включения устройства все имеющиеся Ьлоки обнуляются и приводятся к исходному состоянию. От оконечного оборудования данных по управляющему выходу поступает в момент адаптации логическая единица.

По этому сигналу принудительно на период адаптации под параметры канала связи обнуляется второй блок 10 памяти, открывается элемент И 19, а также выход формирователя 7 последовательности через замкнутый коммутатор

3 15153

Изобретение относится к электросвязи и может найти применение в устройствах передачи данных по каналам связи, 5

Целью изобретения является повышение помехоустойчивости эа счет компенсации эхо-сигналов.

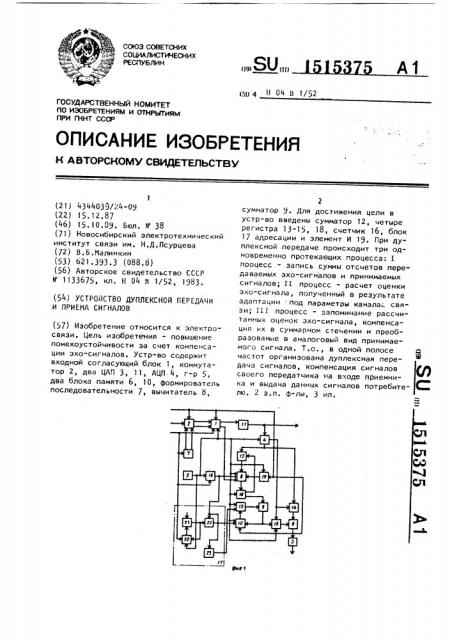

На фиг.1 изображена структурноэлектрическая схема устройства; на 10 фиг.2 - структурно-электрическая схема входного согласующего Ьлока; на фиг.3 - структурно-электрическая схема формирователя последовательности.

Устройство содержит входной согла- 15 ,сующий блок 1,коммутатор 2,первый цифроаналоговый преобразователь З,аналогоцифровой преобразователь 4,генератор

5, первый блок 6 памяти, формирователь 7 последовательности, вы- 20 читатель 8, первый сумматор 9, второй блок 10 памяти, второй цифроаналоговый преобразователь 11, второй сумматор 12, первый регистр 13, второй регистр 14, третий регистр 15, счетчик

16, блок 17 адресации, четвертый регистр 18 и элемент И 19.

Блок 17 адресации содержит регистр

20, первый сумматор 21, второй сумматор 22 и дешифратор 23.

Входной согласующий блок 1 содержит сумматор 24 по модулю два, коммутатор 25, блок 26 постоянной памяти, триггер 27, счетчик 28 и линию 29 задержки. 35

Формирователь 7 последовательности содержит счетчик 30 и выделитель

31 переходов через нуль.

Устройство работает следующим образом. 40

2 подключается к входу входного согласующего блока 1. На вход формирователя 7 последовательности по синхронизирующему выходу от оконечного оборудования данных поступают короткие синхроимпульсы.

Данные синхроимпульсы поступают на счетный вход счетчика 30. Таким образом, если на вход счетчика 30 поступают синхроимпульсы с частотой следования f» = В (где В - скорость передачи информации), то на выходе счетчика 30 будут импульсы с частотой следования f»=f»/m, где ш - коэффициент деления счетчика 30.

Коэффициент деления m счетчика 30 выбирают иэ условия

m (1) где L — длительность импульсной реакции эхо-тракта;

Т вЂ” длительность одного информационного сигнала.

Импульсы с выхода счетчика 30 являются датчиком информационных символов а;, под которые производится обучение (адаптация) устройства под параметры канала связи. Одновременно сигнал с выхода счетчика 30 формирователя 7 последовательности подается на вход выделителя 31 переходов через нуль, в котором выделяются границы переходов информационных символов, например при переходе от а, к а, от а,, к а v т,д. Данные переходы отмечаются короткими импульсами.

Таким образом на вход входного согласующего блока 1 подается с выхода формирователя 7 последовательности информационный сигнал а;, а также синхросигнал, отмечающий короткими импульсами начало каждого символа а;.

Кроме того, по третьему входу подается синхросигнал от оконечного оборудования данных с частотой следования, равной скорости передачи информации В. Информационный сигнал, сформированный формирователем 7 последовательности, в m раэ длиннее реального сигнала а;, который в дальнейшем

Ьудет передаваться по каналу связи.

Информационный символ а на первом тактовом интервале во входном согласующем блоке 1 подается на вход сумматора 24 по модулю два. Так как в первый момент времени линия задержки

1515375

29 была обнулена, то на вход сумматора 24 по модулю два подается нуль.

Выходной сигнал сумматора 24 по модулю даа можно записать выражением

1 5

i oeqs i-i oeyq оь 1ц э () где а „, „и а, — преобразованные

ОС Ч 1-1 06ЯЧ по закону относительности информационные символы на i-м и (i-1)-м тактовом интервале; а; „ - информационный символ, подлежащий передаче;

Д+ - операция суммирования по модулю два.

Начало каждого информационного символа a,",„„ сопровождается коротким синхроимпульсом,который поступает на обнуляющий вход триггера 27. Одновременно на тактовый вход триггера 27 подается импульсная последователь- 25 ность, а на установочный вход — сигнал с первого выхода оконечного оборудования данных.

Сигналы, подаваемые на обнуляющий и установочные входы триггера 27, яв- ляются приоритетными перед любыми другими сигналами. На установочный вход в период адаптации подается сигнал логической единицы, поэтому на данный отрезок времени этот сигнал в управ35 лении триггером 27 не участвует. В управлении триггером 27 на период адаптации участвуют сигналы, посту пающие на обнуляющий и тактовый входы. Так как сигнал, поступающий на 40 обнуляющий вход, имеет приоритет перед тактовым сигналом, поступающим на тактовый вход, то на первом тактовом интервале с началом первого обуI чающего а; „„„триггер 27 принудитель- 45 но устанавливается в нулевое состояние °

Сигнал с выхода триггера 27 управляет работой коммутатора 25, тем са50 мым выход сумматора 24 по модулю два оказывается подключенным к входу блока 26 постоянной памяти. Таким образом,на первомтактовом интервале первога обучающего сигнала на вход блока 26

55 постоянной памяти подается первый информационный символ а „»„, перекодированный в соответствии с выражением (1) по закону относительности. Одновременно синхронизирующий импульс кратковременно обнуляет счетчик 28.

По окончании синхронизирующего импульса счетчик 28 под действием тактовых импульсов, поступающих с выхода генератора 5, начинает изменять свое состояние от минимального значения до максимального значения. Код, подаваемый с выхода счетчика 28 в сочетании с первым обучающим символом

I а„., „, является адресом в блоке 26 постоянной памяти, где по соответствующим ячейкам записаны отсчеты рабочего сигнала S poe (k t). Так, по адресу (а;,„„ 00....00), хранится отсчет

Б,- (kit). Подстрочныи индекс адресного кода означает систему счисления, величина k,Ь t — дискретный момент времени появления первого рабочего сигнала. Двоичные отсчеты S«6 (k;6 t) последовательно появляются йа выходе блока 26 постоянной памяти и подаются на вход второго цифроаналогового преобразователя 11, где преобразуются в аналоговый сигнал Sp p (t). Сигнал

Sp,(t) поступает на вход канала свясвязи и далее в сторону противоположной станции. Одноврменно в период адаптации сигнал S,.,,(t) является сигналом обучения под эхо-сигнал на первом тактовом интервале.

После прихода второго синхроимпульса триггер 27 возвращается в единичное состояние, так как по установочному входу с выхода формирователя 7 последовательности синхросигнала нет и триггер 27 под действием синхросигнала записывает, логическую единицу, подаваемую на информационный вход.

Под действием сигнала логической еди. ницы с выхода триггера 27 коммутатор

25 подключает на вход блока 26 постоянной па,яти логический нуль.

Следовательно, на втором тактовом интервале адрес для блока 26 постоянной памяти будет изменяться от (000...00) до (011...11) ; по соот" ветствующим адресам в блоке 26 постоянной памяти сохранятся нули.

Поэтому после окончания действия

I первого информационного символа а„, ц на первом тактовом интервале на входе блока 26 постоянной памяти на следующих (m-1)тактовых интервалах поступают по адресным входам нули. Лналогично обстоит дело и с другими информационными символами. Лействительно, когда счетчик 30 отсчитает

1515375

m импульсов, то на выходе выделителя

31 переходов через нуль появляется очередной синхроимпульс,который вновь устанавливает триггер 27 в нулевое сос5 тояние. На выходе сумматора 24 по модулю два появляется второй информационный симгол, перекодированный по закону отно«тельности. Счетчик 28 вновь сбрасывается синхроимпульсом в нуль и начинает изменять свое состояние от миним. льного до максимального значения. На входы блока 26 постоянной памяти подается адрес, начиная с (а 2 „ „000... 00) 2 до (а О,. ÷ 11 ° 2 15

Производится обращение к второй линейке блока 26 постоянной памяти, из которого выводятся отсчеты второго рабочего сигнала S p1s (k ht) . Второй. рабочий сигнал S „62(kit) вновь выводится на вход второго цифроаналогового преобразователя 11. Таким образом во время адаптации под параметры канала связи с выхода входного согласующего блока 1 появляются отсчеты рабочего сигнала Sр „ (kdt)

Р08 1 на длительности одного тактового интервала. После окончания данного тактового интервала входной согласующий блок 1 выдает на вход второго цифроаналогового преобразователя 11 нули.

Такой алгоритм первоначальной адаптации необходим для того, чтобы имелась возможность записать эхо-сигнал, длительность которого много больше длительности рабочего сигнала, В про- 5 цессе дуплексной передачи информации входной согласующий блок l выполняет функции обычного модуля-.ора (амплитудного, фазового или частотного).

Поясним, каким образом производится настройка устройства под эхо-сигналы.

При поступлении отсчетов первого рабочего сигнала Б, (kit) с выхода входного согласующего блока 1 они превращаются вторым цифроаналоговым преобразователем 11 в аналоговое напряжение Б (t), которое посту1О 1 гает на вход канала связи и далее в сторону противоположной станции.

Сигнал Б,,(t) в зависимости от параметров подключенного канала связи и его состояния оказывается пр зобразованным (свернутым) с импульсной реакциеи канала связи. Поэтому на входе аналого-цифрового преобразователя 4 наблюдается суммарный сигнал, который равен:

Х () SPP61 ()* g(t-) (i () 1 (3) где g(t) - импульсная реакция эхотракта канала связи;

, (t) — шуп, поступающий иэ канала связи;

Символ * означает операцию свертки;

Сигнал Х,(t) в аналого-цифровом преобразователе 4 преобразуется в отсчеты цифрового сигнала Х,(Ьт), которые поступают на вход второго сумматора 12.

Та« как сигналом с управляющего выхода оконечного оборудования данных элемент И 19 открыт, то на выходе последнего появляется импульсная последовательность с выхода генератора 5, управляющая режимом работы первого блока 6 памяти. Так, если на входе первого блока 6 памяти установлено какое-либо число, по данному адресу вначале считывается прежнее содержимое данной ячейки памяти, а затем записывается новое значение с выхода второго сумматора 12. Считы" ваемое значение из первого блока 6 памяти переписывается в четвертый регистр 18, Одновременно с началом формирования первого сигнала Б „,,(kit) во входном согласующем блоке 1 первым синхрсимпульсом производится обнуление счетчика 16. После окончания первого синхроимпульса счетчик 16 под действием тактовых импульсов с выхода генератора 5 начинает изменять свое состояние с минимального значения до максимального. Перекодированный по закону относительности первый информационный сигйал а;, „c выхода входного согласующего блока 1 в сочетании с кодом, подаваемым с выхода счетчика 16, является адресом для первого блока 6 памяти. Таким образом, при формировании формирователем

7 последовательности первого обучающего информационного символа а, в первом блоке 6 памяти изменяются адреса, начиная с (а„, „00...00)2 и окончиваясь (в р 11 ° ° ° 11) е

Так как первойачально первый блок

6 памяти был обнулен, то из последнего из первой ячейки (адрес а„ „„„00... ...00) вначале считывается нуль, который затем переписывается в чет.вертый регистр 18. На выходе второго сумматора 12 появляется первый отсчет суммарного процесса.

1515375

40

Вухо (1 t) В рав (k ht) g(k< h ) +

+ (, (k ht), (4) который записывается в первом блоке

6 памяти по адресу (а, „„00.. ° 00)rz .

Аналогично отсчет дела с другими отсчетами. Так по адресу (а, „ 00...01)

10Б Ч записывается отсчет

S»0ñ(k ht) Sp„о,(k2ht)* g(kht)

+ ",(, а.) "" (5) 10 и так далее.

Аналогично обстоят дела при формировании входным согласующим блоком

1 на очередных m тактовых интервалах

Sра6 (kdt) соответствующего второ- 15 ра62 ( му информационному символу а2о,„„. В первом блоке 6 памяти по адресу (а„, „ 00...00)2 записывается отсчет, равный:

Вэхо2(k„„dt) = Вра62 1с„„, )* g(kht) + 20

+ (,(k„„dt), (6) где k;h t — дискретный момент времени, В ячейку памяти по адресу (а,„,„„

00...01)2 записывается величина

S», (k, dt) = Вра„(1„„Ю)* g(kht) +

При формировании формирователем

7 последова тел ь ности двухпози ционного сигнала после информационного ! симВОла Я2оь„ч ВнОВь формируется ы!сь, 30

Вновь в первом блоке 6 памяти производится обращение к первой линейке памяти, в котором хранятся отсчеты суммарного процесса S „о (k;ht). При этом вновь в первый момент производится считыва- З5 ние первый ячейки памяти Бэхо,(k,ht) из первого блока 6 памяти, которое переписывается в четвертый регистр

18. Во втором сумматоре 12 производится сложение Яэхо (k(dt) и $эхо, (k, ht). Результат сложения будет равен:

Syxoe<(k2 +id ) = аэхо,(kgh t) + (8) эхо ) эхо, (k 2 + ht) О 45 счеты передаваемого сигнала в разные моменты времени.

Таким образом, после передачи N раз обучающего сигнала а, „„„в первом блоке 6 памяти будет храниться величина и эхо, ® ) = корав,(kid t)* В(® ) ("-1

Ц 1с 6t) . (9)

Йногократное обучение необходимо для того, чтобы усреднить действие помех, действующих в канале связи, и тем самым улучшить качественные характеристики устройства в целом.

Как видно из формулы (9), для того чтобы иметь оценку эхо-сигнала, надо

S хо, (ЕЬс) разделить на N, Деление на

N производится в четвертом регистре

18. Для того, чтобы разделить полу ченный отсчет на N, необходимо величину отсчета S,, (kit) сдвинуть на

Z разрядов в сторону старших разрядов так, чтобы 2 N, где Z — число сбрасываемых разрядов. Например, если N выбрано равным 64, то отбрасываем 6 младших разрядов и тем самым производим деление на 64. Таким образом, после адаптации устройства под параметры канала связи, входной согласующий олок 1 формирует N раз рабочие сигналы Б 6,(t) и Sp (t), а на данные рабочие сигналы канал связи

N раз откликнется эхо- сигналом. Отсчеты данного эхо-сигнала в виде двоичного числа записаны в первом блоке

6 памяти, При обучении устройства под параметры канала связи скорость считывания и запись отсчетов из первого блока 6 памяти равна скорости формирования рабочих сигналов ° Такой режим обеспечивается подачей тактовой частоты на вход счетчика 16 точно такой же, что и на Вход счетчика 28 во входном согласующем блоке 1.

После перебора N раз информацион( ных символов а,а, „оконечное обоРУДование данных по управляющему выходу снимает положительный потенциал, тем самым снимается принудительный обнуляющий сигнал с второго блока 10 памяти, а также коммутатор 2 отключает выход формирователя 7 последовательности от входа входного согласующего блока 1. Кроме того, закрывается элемент И 19, тем самым первый блок 6 памяти переходит только в режим счииывания информации, поэтому полученные в процессе обучения эхо-сигналы остаются неизменными на протяжении сеанса связи.

Вход входного согласующего блока

1 оказывается подключенным после обучения к информационному выходу оконечного оборудования данных. Так как с выхода формирователя 7 последовательности синхроимпульс больше не поступает во входной согласующий блок

1, а с выхода оконечного оборудования данных после окончания обучения поступает логический нуль на установочный вход триггера 27, то последний

1515375

12 устанавливается в единичное состояние до окончания сеанса связи и подключает выход сумматора 24 по модулю два 2 к входу блока 26 постоянной памяти.

Входной согласующий блок 1 превращается тем самым по свойствам в обычный амплитудный, фазовый или частотный модулятор. Тип выбранного модулятора оговаривается перед сеансом связи путем соответствующих записей в блоке 26 постоянной памяти счетчиков рабочего сигнала, которые соотI ветствуют перечисленным выше видам 15 модуляции, Поясним каким образом производится дуплексная передача информации.

При дуплексной передаче происходит три одновременно протекающих процес- 20 са. Первый процесс - это запись суммы отсчетов передаваемых эхо-сигналов и принимаемых сигналов. Данная операция производится с помощью аналогоцифрового преобразователя 4 и второго ре- 25 гистра 14, Второй процесс - процесс расчета оценки эхо-сигнала, полученный в результате адаптации под параметры канала связи. Данный процесс произво- 30 дится с помощью первого 6 и второго

10 блоков памяти; первого 13, третьего 15, четвертого 18 регистров; первого 9 сумматора, счетчика 16, блока

17 адресации, состоящего из первого 35

21. и второго 22 сумматоров; регистра

20 и дешифратора 23.

Третий процесс — запоминание рассчитанных оценок эхо-сигнала, компенсация их в суммарном стечении и пре- 40 образование в аналоговый вид принимаемого сигнала. Данный процесс осуществляется с помощью третьего регистра 15, вычитателя 8 и первого цифроаналогового преобразователя 3.

Рассмотрим более подробно реализацию первого процесса - процесса записи сигнала, поступающего из канала связи.

Приходит принимаемый сигнал у,(t), который необходимо отделить от передаваемого сигнала (в нашем случае это S>, (kit)). Пусть на вход входного согласующего блока 1 поступает первыи формационный символ а,. Согласно выражению (1), данный информационный символ а, перекодируется в сумматоре 24 по модулю два и линии

29 задержки в относительный информационный сигнал a> . Значение данного информационного символа а совместно >

i с кодом счетчика 28 указывает область памяти блока 26 постоянной памяти, в котором хранятся отсчеты первого рабочего сигнала В,,(kit). Данные отсчеты, пройдя первый цифроаналоговый преобразователь 3, превращаются в аналоговые сигналы S (<.), раь < которые далее подаются в сторону противоположной станции. Одновременно с формированием рабочего сигнала

S»g,(kdt) во входном согласующем блоке 1 на втором выходе последнего появляется относительный информационный символ а,, который совместно с кодом счетчика 16 указывает в первом блоке

6 памяти область памяти, в которой записан отклик канала связи S „,(kit) на первый рабочий сигнал.

Как указывалось выше, количество отсчетов, необходимых для формирования рабочего сигнала и, меньше количества отсчетов записанного эхо-сигнала d при работе по реальным каналам связи <из-за наличия реактивных элементов, а также наличия дифференциальных систем каналов тональной частоты. Поэтому скорость обработки отсчетов эхо-сигнала должна быть как минимум в d/n раз выше, чем скорость формирования рабочего сигнала. На входе аналого-цифрового преобразователя 4 наблюдаем сумму двух сигналов: эхо-сигнала и принимаемого сигнала, а на выходе аналого-цифрового преобразователя 4 — ту же сумму, но в виде двоичного числа.

Х,(К,ht) = S xo,(kinet) + Ys(k,ht) (10)

Здесь k,gt обозначает первый дискретный момент времени, когда мы наблюдаем сумму двух сигналов на выходе аналого-цифрового преобразователя 4 при дуплексном обмене. Данный отсчет

Х,(k

Х, /1,дс) = Я,„,,(1 t) + Y<(k,

После появления отсчета Х,(k ht) последний записывается в первый стол15153 бец второго регистра 14, а предыдущее содержимое первого столбца, т.е.

Х, (k ht) переписывается во второй столбец и так делее. После формиро5 вания входным согласующим блоком 1 последнего отсчета рабочего сигнала второй регистр 14 полностью заполнится, При формировании первого отсчета второго рабочего сигнала в первый столбец второго регистра 14 уже будет записываться отсчет суммарного процесса, состоящего из главной части второго рабочего сигнала, принимаемого сигнала на втором тактовом интервале и эхо-сигнала от первого рабочего сигнала, т.е.

Х2,(1 n„at) = S»o (k Ьt) + У (k, Лг) + (12)

Данные отсчеты на втором тактовом интервале также последовательно записываются во второй регистр 14, продвигая предыдущие записанные отсчеты к входу вычитателя 8.

Аналогично обстоят дела и с дру- 25 гими отсчетами.

Поясним более подробно суть второго происходящего процесса - процесса формирования оценки эхо-сигнала. Из анализа формул (10)-(12) видно, что З0 к каждому принимаемому отсчету g (kit ) добавляются отсчеты эхо-сигналов, которые необходимо выработать и в дальнейшем скомпрометировать как указывалось выше. При формировании пер- 35 вого рабочего сигнала на первом тактовом интервале входным согласующим блоком 1 на выходе последнего появляется относительный информационный символ à . Значение данного символа 40 в сочетании с кодом, подаваемым с выхода счетчика 16 указывает в первом блоке 6 памяти область памяти,в которой записан образец эхо-сигнала $» (kit). Счетчик

16 начинает изменять свое состояние, тем самым на выходе первого блока 6 памяти последовательно появляются отсчеты первого эхо-сигнала. Как указывалось выше, отсчеты первого эхосигнала при многократном обучении оказалось в N раз больше реально существующих эхо-сигналов. Поэтому отсчеты первого эхо-сигнала, пройдя четвертый регистр 18, в котором отброшены r младших разрядов, оказываются поделенными на N (при выполнении условия 2 = N).

Таким образом, при изменении адресации на первом тактовом интервале

75 14 от (a, 00...00) = А до A,= (а, 11... 11) z на выходе четвертого регистра 18 последовательно появляются отсчеты первого эхо-сигнала

$ „ (kdt). Данные отсчеты затем по1 даются на первый вход первого сумматора 9, который совместно с вторым блоком 1О памяти, первым регистром

13, блоком 17 адресации и третьим регистром 15 вырабатывает оценку эхосигнала на первом тактовом интервале.

Поясним каким образом это производится, более подробно. Пусть в первый момент времени (первый тактовый интервал) блок 17 адресации вырабатывает адрес для второго блока 10 памяти синхронно с адресацией для первого блока 6 памяти. Таким образом, если для первого блока 6 памяти указывается адрес A,o = (a, 00...00), для второго блока 10 памяти указывается адрес В„, = (00...00) . Аналогично и с другими адресами, если для. первого блока 6 памяти указывается адрес A

t (а, 00, ° . 01), то для второго блока (10 памяти указывается адрес В, (00...01) и т.д. Здесь и далее подстрочные индексы (т.е. 2 и 1О) обозначают систему счисления. Порядок выработки такой адресации будет пояснен ниже.

Так как второй блок 10 памяти в момент обучения под эхо-сигналы

$,„о (kit) был принудительно обнулен ио, сигналом с выхода оконечного оборудования данных, во втором блоке 10 памяти по всем адресам в данный момент времени хранятся нули. Порядок обращения к ячейкам памяти второго блока 10 памяти следующий. В начале из какой-либо ячейки по заданному адресу считывается пре>инее содержимое, а затем вновь по этому же адр»су записывается результат суммирования с выхода первого сумматора 9. Т-,о ким образом, из ячейки с адресом В второго блока 10 памяти вначале в первый момент считывается нуль, а затем записывается результат суммирования с выхода первого сумматора 9, т,е. величина

$ qo, (1 1 ) + О = $ 1о,(1 ") °

Ааналогично по адресу В„во вторсм блоке 10 памяти записывается величина $э о (к Ьс), по адресу В„ величина $ „„ (kd „ ьt), а по адресу

В„ — последний отсчет первого эхосигнала $ „ (k< dt). При этом первые э о, 16

15 и отсчетов первого эхо-сигнала одновременно запоминаются в третьем регистре 15. Это будет оценка суммарного эхо-сигнала на первом тактовом интервале. С началом второго тактового интервала блок адресации 17 начинает адресацию для второго блока 10 памяти со сдвигом на величину п. Таким образом, если для первого блока 6 па0 I мяти вырабатывается адрес А„= (а2

00...00)2, то для второго блока 10 памяти вырабатывается адрес, равный

О о

Ало +

При переходе счетчика 16 в следующее состояние на первый блок 6 памяI ти выдается адрес, равный A, = (а2

00...01)2, а на второй блок 10 памяh+ ти вырабатывается адрес, равный B ло

Таким образом, с началом второго тактового интервала считывание и запись во втором блоке 10 памяти производится со сдвигом íà и относительно первого тактового интервала. Если на выходе счетчика 16 совместно с перекодированным символом на втором тактовом интервале последовательно появляются адреса в виде А „,А „,,A „...A", д ...A,o, то на выходе олока 17 адресации появляются адреса для второго блока 10 памяти соответственно в виде

О n+i 2n

@>о ило) В1о,В ло В 1О, В,, ° .. В, . Тогда с началом второго тактового интервала 1з первого блэка

О

6 памяти по адресу А, считывается

S „(k, х t), а из второго блока 0 паэхо, мяти по адресу Б„— значение S»0

% (kzdt) . Аналогично по адресу Л, из первого блока 6 памяти считывается отсчет S,„(k dt), ф из второго блока 1 0 памяти отсчет Я » (k„т х ) и т.д. В результате суммирования в первом сумматоре 9 появляется сумма двух отсч< TQB (в первый момент)

S xn (к ht ) + Бэх (k i d t) ° В следую щий момент данная сумма будет равна

S «(,k. dt) + S»o (k„„ dt) a T° . д» "ри этом результат суммирования первого сумматора 9 записывается вновь во второй блок 10 памяти. Так по адресу

В„записывается сумма, равная

Б,х (Е, A t) + Б,хо,(k„„g t), а по адСостояние счетчика 16 дешифрируется дисшифратором 23. При этом, если счетчик 16 изменяет свое состояние от А, до А „, то на выходе део О- n-< шифратора 23 логическая единица Если состояние дешифратора 23 изменяется от Л, до А,, то на выходе деg-n ь шифратора 23 — логический нуль. Данный сигнал с выхода дешифратора 23 принудительно обнуляет первый регистр

13. Таким образом, на входном тактовом интервале при изменении состояния

a-n Q четчика 16 от А, до A на выходе первого сумматора 9 будут только отсчеты второго эхо-сигнала

Sgxpg(kd-n Аt) Вэхо, (kd „+ф) 1 ° ° °

S»o (k< ц")

Данные отсчеты записываются по адреи-л !

5 сам В», В„„, В,о ... В соответло ственно.

На третьем тактовом интервале блок

17 адресации вновь передвигает свою адресацию еще на и. Таким образом, если на выходе счетчика 16 адреса

О изменяются в виде А,О, А„, А„,...

А,, то на выходе блока 17 адреd сации порядок обращения к второму блоку 10 памяти будет следующий: В„,", 2nt1 7n Z Bd ц 1 2

Bло > 81о х Влр > ВлО ° B„0 ю Bio ° ° венно на выходе первого сумматора 9 будут значения отсчетов эхо-сигнала в виде

30 S>xc (k16") + S xo,(k», d ") + эхо л(k2.

Shxoq (kg d t) + Вэхо (1 д, )

+ ОЭхо t(1 2 +2 о ) э а

35 Коз(Ь 2„dt) + эхОр(+ эхо, (kg х")

S,„„о,(1с dt) + S,„x,(k>ht). .хОъ(ь -n>id )

"ЭХО (®Ь +2 о )

45 о

Saxon (kd d t) .

Первые и отсчетов суммарного процесса с выхода первого сумматора 9 вновь зайисываются в третий регистр

15, который характеризует оценку эхосигнала на третьем тактовом интервале. Аналогично протекает процесс и на других тактовых интервалах.

Поясним, каким образом протекают процессы в блоке 17 адресации. Как показано выше, на первом тактовом интервале на выходе блока 17 адресации порядок обращения к ячейкам па17

1515375

10

1. Устройство дуплексной передачи и приема сигналов, содержащее входной согласующий блок, коммутатор, вычитатель, генератор, формирователь последовательности, первый блок памяти, первый цифроаналоговый преобразователь, последовательно соединенные второй цифроаналоговый преобразователь и аналого-цифровой преобразователь, последовательно соединенные первый сумматор и второй блок памяти, причем первый выход формирователя последовательности подключен к первому входу коммутатора, второй вход которого соединен с вторым входом второго блока памяти, выход генератора подключен к первым входам входного согласующего блока, аналого-цифрового преобразователя, первого блока памяти и третьему входу второго блока памяти, о т л и ч а ю щ е е с я тем> что, с целью повышения помехоустойчивости за счет компенсации эхо-сигналов, введены первый, второй и третий регистры, элемент И, последовательно соединенные счетчик и блок адресации,поспедовательно соединенные четвертый регистр и второй сумматор,выход которого подключен к второ, му входу первого блока памяти, третий „ четвертый и пятый входы которого соединены соответственно выходам . счетчика, элемента И и первым выхсдо". входного согласующего блока, выход первого блока памяти подключен к первому входу четвертого per c;Па, второй выход которого подключен v. псрвому входу первого сумматора, второй вход которого соединен с выходом первого регистра, первый и второй входы которого соединены соответственно с выходом второго блока памяти и перв. выходом блока адресации, второй выход которого подключен к четвертому Вхо ду второго блока памяти, первьй выход аналого-цифрового преобразователя

?О мяти будет таким же, как и обращение к ячейкам памяти первого блока 6 памяти. Однако работоспособность выработки оценки эхо-сигнала не зависит от того, с какого состояния начинается обращение в первый момент к ячейкам памяти второго блока 10 памяти. Пусть в первый момент времени в регистре 20 хранится число п, .

Тогда на выходе первого сумматора

21 будет значение, равное -п„ + и, =

= О. Таким образом, на второй вход второго сумматора 22 подается логический нуль, поэтому сигналы с выхода счетчика 16 беспрепятственно проходят на выход второго сумматора

22, тем самым обеспечивается синхронность адресации для первого 6 и второго 10 блоков памяти.

С началом второго тактового интервала его начало сопровождается синхроимпульсом от оконечного оборудования данных, тем самым состояние первого сумматора 21 записывается 25 в регистр 20, Как было показано выше, на выходе первого сумматора 21 был логический нуль. Тогда на выходе первого сумматора 21 появляется сигнал, равный и„о,„= и«, который подается на второй вход второго сумматора 22.

Таким образом производится увеличение адресации на втором тактовом интервале для второго блока 10 памя1и на n„

Аналогичны процессы на третьем тактовом интервале. Действительно после записи в регистр 20 с началом третьего тактового интервала сигнала и, с выхода сумматора 21 на выходе последнего появляется значение

n, n« = 2n«> и так далее.

Поясним третий процесс - процесс компенсации отсчетов эхо-сигналв в суммарном процессе, поступающем из канала связи. Как показано выше, суммарный процесс, повтупающий из канала связи, хранится во втором регистре 14, а оценки эхо-сигнала хранятся в третьем регистре 15. После окончания выработки оценки эхо-сигнала последние последовательно по сигналу с второго выхода аналого-цифрового преобразователя 4 (строб-импульсы окончания преобразования) начина55 ют считываться из третьего регистра

15, На выходе вычитателя 8 остается лишь принимаемый сигнал, поступающий от противоположной станции из канала связи, который далее преобразуется первым аналого-цифровым преобразователем 3 в аналоговую величину и выдается потребителю.

Таким образом в одной полосе частот организована дуплексная передача сигналов, компенсация сигналов своего.передатчика на входе приемника и выдача данных сигналов потребителю.

Формула изобретения

19

1515375 рым и третьим входами блока адресации, первым и четвертым входами, первым и вторым выходами которого явля5 ются соответственно вход дешифратора и второй вход первого сумматора, выходы дешифратора и второго сумматора. подключен к первому входу второго регистра и второму входу второго сумматора, второй выход аналого-цифрового преобразователя подключен к второму входу второго регистра и первому входу третьего регистра, второй вход и гыход которого соединены соответственно с выходом первого сумматора и первым входом вычитателя„ второй вход и выход которого соединены соответственно с выходом второго регистра и входом первого цифроаналогового преобразователя> выход генератора подключен к первым входам счетчика и элемента И, вторым входам блока адресации и четвертого регистра и третьим входам первого и третьего регистров, второй вход коммута ора соединен с.вторыми входами входного со- 2п гласующего блока и элемента И, второй вход счетчика соединен с третьими входами входного согласующего блока и блока адресации и входом формирователя последовательности, второй выход 25 которого подключен к четвертому входу коммутатора, первый и второй выходы которого подключены к четвертому и пятому входам входного согласующего блока, второй выход ко1орого подклю- 30 чен к входу второго цифроаналогового преобразователя, при этом блок адресации содержит дешифратор и последовательно соединенные регистр, первый сумматор и второй сумматор, первый и второй входы которого соединены соответственно с входом дешифра ора и первым входом регистра, второй и третий входы которого являются вто2. Устройство по п,1, о т л и ч а ю щ е е с я тем, что формирователь последовательности содержит последовательно соединенные счетчик и выделитель переходов через нуль, вход и выход которого являются первым и вторым выходами формирователя последовательности, входом которого является вход счетчика.

3. Устройство по п.1, о т л и ч а ю щ е е с я тем, что входной согласующий блок содержит триггер, счетчик, последовательно соединенные линию задержки, сумматор по модулю два, коммутатор и блок постоянной памяти, второй вход которого соединен с выходом счетчика, первый вход которого соединен с первым входом триггера, выход которого подключен к второму входу коммутатора, выход сумматора по модулю два подключен к входу линии задержки и является первым выходом вкодного согласующего блока, вторым выходом, первым, вторым, треть:.и, четвертым и пятым входом которого явпяются соответственно выход блок.-. памяти, второй вход триггера, в1эрой вход счетчика, второй вход сумматора по модулю два и третий вход триггера.

1515375 фиг 2

С