Устройство для вычисления симметрических булевых функций

Иллюстрации

Показать всеРеферат

Изобретение относится к вычислительной технике и микроэлектронике и предназначено для построения быстродействующих арифметико-логических устройств матричного типа. Цель изобретения - упрощение устройства за счет сокращения количества входов логических элементов. Устройство для вычисления симметричных булевых функций трех переменных содержит три элемента ИЛИ-НЕ, пять элементов И, один элемент СЛОЖЕНИЕ ПО МОДУЛЮ 2, три элемента И-НЕ, три информационных входа, четыре настроечных входа и один выход. На информационные входы устройства подаются двоичные переменные X<SB POS="POST">1</SB>,X<SB POS="POST">2</SB>,X<SB POS="POST">3</SB>, на настроечные входысигналы настройки φ<SB POS="POST">0</SB>, φ<SB POS="POST">1</SB>, φ<SB POS="POST">2</SB>, φ<SB POS="POST">3</SB>, значения которых принадлежат множеству {0,1} . На выходе устройства реализуется симметрическая булева функция F=F(X<SB POS="POST">1</SB>,X<SB POS="POST">2</SB>,X<SB POS="POST">3</SB>), определяемая вектором настройки φ(F)=(φ<SB POS="POST">0</SB>,φ<SB POS="POST">1</SB>,φ<SB POS="POST">2</SB>,φ<SB POS="POST">3</SB>). 1 ил., 1 ТАбл.

СОЮЗ СОВЕТСНИХ

СОЦИАЛИСТИЧЕСКИХ

РЕСПУ БЛИН (5I)4 G 06 F 7 00

ОПИСАНИЕ ИЗОБРЕТЕНИЯ

К ABTOPCHOlVlV СВИДЕТЕЛЬСТВУ

ГОСУДАРСТВЕННЫИ КОМИТЕТ

ПО ИЗОБРЕТЕНИЯМ И ОТКРЫТИЯМ

ПРИ ГКНТ СССР (21) 4382975/24-24 (22) 13. 01 . 88 (46) 23.10.89. Бюл. 1| 39 (72) Л.Б.Авгуль, А.П.Криницкий и В.П.Супрун (53) 681.3 (088 8) (56) Авторское свидетельство СССР

1179314, кл. G 06 F 7/00, 1984.

Авторское свидетельство СССР

9 1432500, кл. С 06 F. 7/00, 1987. (54) УСТРОЙСТВО ДЛЯ ВЫЧИСЛЕНИЯ СИММЕТРИЧЕСКИХ БУЛЕВЫХ ФУНКЦИЙ (57) Изобретение относится к вычислительной технике и микроэлектронике и предназначено для построения быстродействующих арифметико-логических устройств матричного типа. Цель изобретения — упрощение устройства за

Изобретение относится к вычислительной технике и микроэлектронике и предназначено для построения быстродействующих арифметико-логических устройств матричного типа °

Цель изобретения — упрощение устройства за счет сокращения количества входов логических элементов.

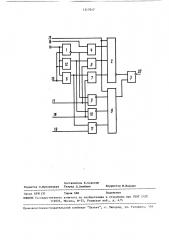

На чертеже представлена схема устройства для вычисления симметрических булевых функций трех переменных.

Устройство содержит три элемента

ИЛИ-HE 1-3, пять элементов И 4-8, три элемента И-НЕ 9-11, элемент СЛОЖЕНИЕ ПО МОДУЛИ 2 12, три информационных входа 13-15 устройства, четыре настроечных входа 16-19 устройства и выход 20 устройства.

„„SU„„3 517017 А 1 счет сокращения количества входов логических элементов. Устройство для вычисления симметрических булевых функций трех переменных содержит три элемента ИЛИ-НЕ, пять элементов И, один элемент СЛОЖЕНИЕ ПО МОДУЛЮ 2, три элемента И-НЕ, три информационных входа, четыре настроечных входа и один выход. На информационные входы устройства подаются двоичные переменные х,, х, х >, на настроечные входы — сигналы настройки h,, fi,, н,, ||з, значения которых принадлежат множеству (0,1 . На выходе устройства реализуется симметрическая булева функция F = Р(х,, х, х ), определяе- а

Я мая вектором настройки л(Р) = (и„

fi,, Г, II>) . 1 ип., 1 табл.

Устройство работает следующим образом.

На информационные входы 13-15 поI даются двоичные переменные х „, х и

1 х> соответственно, на настроечные входы 1 6-1 9 — сигналы настройки Г(,, и II соответственно, значения которых принадлежит множеству |0,11.

На выходе 20 устройства реализуется симметрическая булева функция F =

= F(х,, Ъ.„ х ), определяемая вектором настройки и(F) = (i,, |(,,, из).

Значения компонента вектора fi(Ã) и соответствующие ему реализуемые симметрические булевы функции F приведены в таблице настроек.

151 7017

Устройство имеет простую конструкцию, его сложность по числу входов логических элементов равна 28, в то время как сложность устройства-прототипа равна 35.

Формулаизобретения

Устройство для вычисления симметр |ческих булевых функций, содержащее три элемента ИЛИ-НЕ, первый вход nept вого из которых соединен с первым информационным входом устройства, выход первого элемента ИЛИ-НЕ соединен с первым входом второго элемента ИЛИIII;, выход которого соединен с выходом устройства, второй и третий информапионные входы которого соединены соответственно с первым и вторым входами третьего элемента ИЛИ-НЕ, о т л и ч а ю щ е е с я тем, что, с целью упрощения устройства, оно содержит пять элементов И, три элеменrа И-НЕ и элемент СЛОЖЕНИЕ ПО МОДУЛЮ 25

2, первый и второй входы которого соед п ены соответственно с вторым и третьим информационными входами устройства, выход элемента СЛОЖЕНИЕ ПО

МОДУЛЮ 2 соединен с первым входом первого элемента И-НЕ и первым входом первого элемента И, выход которогo соединен с вторым входом первого элемента ИЛИ-НЕ, второй вход первого

Реализуемая функция F на выходе 20 2

18 19

Л,!

17

0

О

1 !

1

0

0

1

О

1

0

0 !

0

1 !

0

0

0

0

О

0

0

0

0

0

О

0

О

1

1

1

1

1Х zxx3

Х1Х1Х, V Х1Х2Х V Х1

X X gV Х1Х3 ч Х1Х3

Х Х1>,3Ч Х1Х ХЗ \/ Х

Х1Х1Х3 V Х Х1Х V Х

Х Х ХХ VX1X3

Х, V Х1ЧХ3

1 3

Х1Х1Х3 Ч Х1Х1Х3

Х1Х1Х3 Х1Х Х 3 Х, Х,Х.„ХÇV Х1Х2+ Х Х3

Х1Х1/ Х1ХЭ / Х2ХЗ

Х Х1 Х1Х3 Х1ХЬ х,ч хз х х

ХХ1Х3

Х1Х3 х õ,õ х,х х,х,х ч х,х, Х, Х, Х3

Сигналы настройки на входах элемента И соединен с первым настро— ечным входом устройства и первым входом второго элемента И-НЕ, выход которого соединен с первым входом второго элемента И, второй вход второго элемента И-НЕ соединен с выходом третьего элемента ИЛИ-НЕ и первым входом третьего элемента И, второй вход которого соединен с вторым настроечным входом устройства, выход третьего элемента И соединен с третьим входом первого элемента ИЛИ-НЕ, четвертый вход которого соединен с выходом четвертого элемента И, первый вход которого соединен с вторым входом первого элемента И-НЕ и третьим настроечным входом устройства, второй вход четвертого элемента И соединен с первым входом третьего элемента И-HE и выходом пятого элемента И, первый и второй входы которого соединены соответственно с вторым и третьим информационными входами устройства, четвертый настроечный вход которого соединен с вторым входом третьего элемента И-НЕ, выход которого соединен с вторым входом второго элемента И, выход которого соединен с вторым входом второго элемента ИЛИ-НЕ, третий и четвертый выходы второго элемента И вЂ” соответственно с первым информационным входом устройства и с выходом первого элемента И-НЕ.

1517017

13

16

l9

Составитель В. Сорокин

Редактор О,Юрковецкая Техред Л.Олийнык Корректор М.П1ароши

Заказ 6391/51 Тираж 668 Подл исно е

ВНИИПИ Государственного комитета по изобретениям и открытиям при ГКНТ СССР

113035, Москва, Ж-35, Раушская наб., д. 4/5

Производственно-издательский комбинат "Патент", r. Ужгород, ул. Гагарина, 101