Устройство для деления

Иллюстрации

Показать всеРеферат

Изобретение относится к вычислительной технике и может быть использовано при построении быстродействующих процессоров цифровой обработки сигналов и в арифметических устройствах быстродействующих цифровых и комбинированных вычислительных машин. Цель изобретения - сокращение аппаратурных затрат. Новым в устройстве, содержащем регистры делимого 1 и делителя 2, два матричных умножителя 3, 4 и два сумматора 6, 7, является введение блока 5 приближенного вычисления обратной величины, блока 9 синхронизации и группы элементов НЕ. 1 з.п. ф-лы, 4 ил.

СОЮЗ СОВЕТСКИХ

СОЦИАЛИСТИЧЕСКИХ

РЕСПУБЛИК (51) 4 G 06 F 7/52

ОПИСАНИЕ ИЗОБРЕТЕНИЯ

Фиа.1

ГОСУДАРСТВЕННЫЙ КОМИТЕТ

ПО ИЗОБРЕТЕНИЯМ И ОТКРЫТИЯМ

ПРИ ГКНТ СССР

К А ВТОРСКОМУ СВИДЕТЕЛЬСТВУ

1 (21) 4400180/24-24 (22) 29.03.88 (46) 23.10.89. Бюл. N- 39 (71) Институт кибернетики им. В.М.Глушкова (72) В.К.Белик (53) 681.325(088.8) (56) Авторское свидетельство СССР

У 991417, кл. G 06 F 7/52, 1981.

Авторское свидетельство СССР

N - 1317432, кл. G 06 F 7/52, 1985. (54) УСТРОЙСТВО ДЛЯ ДЕЛЕНИЯ (57) Изобретение относится к вычислительной технике и может быть ис„„Я0„„1517026 А1

2 пользовано при построении быстродействующих процессоров цифровой обработки сигналов и в арифметических устройствах быстродействуюших цифровых и комбинированных вычислительных машин. Цель изобретения сокрашение аппаратурных затрат, Новым в устройстве, содержашем регистры делимого 1 и делителя 2, два матричных умножителя 3,4 и два сумматора 6,7, является введение блока 5 приближенного вычисления обратной величины, блока 9 синхронизации и группы элементов НЕ, 1 з,п, ф-лы, 4 ил, 1517026

Изобретение относится к вычисли1 тельной технике и может быть использовано при построении быстродействующих процессоров цифровой обработки сигналов и в арифметических устройст5 вах быстродействующих цифровых и комбинировапных вычислительных машин.

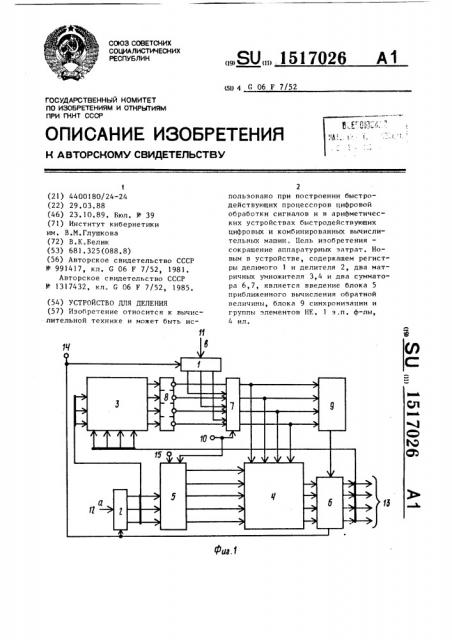

Целью изобретения является сокращение аппаратурных затрат. 10 !!а фиг. 1 приведена функциональная схема устройства; на фиг,,2 — функциональная схема блока приближенного вычисления обратной величины; на фиг, 3 — схема блока синхронизации; на фиг. 4 — возможн и вариант реализации б.»ока синхронизации.

Устройство для деления (фиг. 1) содержит регистр 1 делимого, регистр

2 делителя, первый 3 и второй 4 матричные умножители, блок 5 приближенного вычисления обратной величины, первый 6 (накапливающий) и второй 7 (комбинационный) сумматоры, группу 8 элементов НЕ, блок 9 синхронизации, вход 10 логической единицы устройства, информационные входы 11 и 12 делимого и делителя устройства соответственно, ш»формационные выходы 13 результата деления (частного устройства), управляющи»» вход 14 устройства и вход 15 логического нуля устройства.

Блок 5 приближенного вычисления обратной величины (фиг. 2) содержит 35 группу 16 элементов НЕ, комбинационньп» сумматор 1/, информационные входы 18 и выходы 19 блока.

Блок 9 синхронизации (фиг. 3) содержит входы 20 и выход 21 блока, 40 первый 22 и второй 23 элементы И, элементы ИЛИ-НЕ 24 и ИЛИ 25 и генератор 26 импульсов, В случае применения устройства в составе конвейернь.х систем с матричными синхронизируемыми умножителями блок 9 (фиг. 4) содержит дополнительно элемент НЕ 27, два элемента 28 и 29 задержки, выход

30 внешней синхронизации устройства и выходы 31 и 32 синхронизации для 50 матричньв< у»»»»ожителей.

В устройстве реализуется дискретным способом итерационный процесс, соответствующий уравнению

x " = x + ц(а) (-а.х " + Ь), где а — делитель;

Ь вЂ” делимое;

Ц а) =—

1 а

Устройство работает следующим образом.

По переднему фронту импульсного сигнала, поступающего на управляющий вход 14 устройства, осуществляется сброс накапливающего сумматора 6 в нулевое состояние, коды делимого и делителя в нормализованном виде с соответствующих входов 11 и 12 устройства заносятся в регистры 1 и 2 делимого и делителя соответственно.

Сигналы кода делителя с выхода регистра 2 поступают на информационные входы блока 5 приближенного вычисления обратной величины, в результате чего на выходе блока 5 устанавливаются сигналы кода с (а)

1 которые поступают, на входы пера вого сомножителя матричного умножителя 4. Кроме того, сигналы кода делителя с выходов регистра 2 поступают также на входы первого сомножителя матричного умножителя 3.

Сигналы кода (сначала нулевого) с выходов регистра поступают на входы второго сомножителя матричного умножителя 3. На выходе умножителя

3 образуется результат умножения, равный сначала нулевому коду. Сигналы результата умножения (сначала нулевого кода) с выходов умножителя 3 поступают на входы групп 8 элементов НЕ, где инвертируются в сигналы кода 1, 1 1...1, которые поступают на входы первого слагаемого сумматора 7, на входы второго слагаемого которого поступили сигналы кода делимого с выходов регистра 1. C учетом того, что вход переноса сумматора 7 соединен с входом 10 логической единицы, на выходе сумматора 7 образуется код (-ах " + Ь), где х = О, сигналы которого в прямом, если (-ах + Ь) Ъ О, или дополнительном коде, если -ах + Ь О, поступают параллельно на входы блока 9 синхронизации и на входы второго сомножителя умножителя 4, В результате на выходе умножителя 4 образуется соответственно в прямом или дополнительном коде результат умножения (а) (-ах + Ь) = ср(а)Ъ, сигналы кода которого поступают на входы сумматора 6.

1517026 зависимости от знака разности на вьг ходе сумматора 7. При поступлении сигналов нулевого кода с выходов сумматора 7 на входы блока 9 прекращается поступление очередного импульса с выхода 21 блока 9, а на выходе 30 сигнал логического нуля изменяется на сигнал логической единицы.

На выходах сумматора 6 и на выходах 13 устройства устанавливается код результата деления {частного), вычисленного с точностью младшего разряда. Сигнал на выходе 30 блока

9 может быть использован для синхронизации последующих устройств в системе обработки данных. Описанные процессы соответствуют случаю применения матричных умножителей 3 н 4 беэ синхронизации. В случае, когда матричные умножители 3 и 4 являются синхронизируемыми, импульсы с Bblxo дов 31 и 32 блока 9 поступают на входы синхронизации умножителей 4 и

3 соответственно а каждая итерация завершается не за один такт, а за три, длительность которых определяется задержкой в элементах 28 и 29 и периодом импульсов генератора 26.

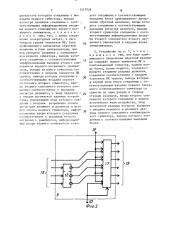

Блок 5 приближенного вычисления обратной величины работает следующим образом. При поступлении на входы

18 блока сигналов кода делителя в группе 16 элементов НЕ осуществляется инверсия сигналов всех разрядов, кроме старшего. Инверсные сигналы вместе с прямым сигналом старшего разряда делителя поступают на входы первого слагаемого комбинационного сумматора 17. С учетом того, что входы второго слагаемого сумматора 17 соединены с входом логического нуля, а вход переноса и младшего разряда первого слагаемого — с входом логической единицы, на выходах 19 сумматора 17 образуется код результата с (а) = 3 — 2 а = 1 а

Формула изобретения

1. Устройство для деления, содержащее регистры делимого и делителя, два матричных умножителя и два сумматора, причем информационные входы регистров делимого и делителя соеди нены соответственно с входами делимого и делителя устройства, выходы

Вследствие поступления на входы блока 9 ненулевого кода (вначале равного коду делимого b), на его выходе 21 появляется серия импульсов фиксированной частоты, а на выходе

30 внешней синхронизации уровень сигнала с единичного переходит в нулевой.

По сигналу первого импульса (иэ серии), поступившего с выхода 21 бло° ка 9 на вход синхронизации сумматора 6, в последнем образуется результат первой итерации x (" 0 +

+ ц (а) (-а ° О + b) = (а) ° Ъ, сигналы кода которого появляются на выходах

13 устройства и поступают на входы второго сомножителя умножителя 3. С учетом того, что на входах второго сомножителя сохраняются сигналы ко- 20 да делителя, на выходе умножителя 3 получается результат умножения а х > который в дополнительном коде, получаемом с помощью группы 8 элементов НЕ и подачей сигнала логической 25 единицы на вход переноса сумматора

7, поступает на входы первого слагаемого сумматора 7, на входах второго слагаемого которого по-прежнему сохраняются сигналы кода делимого, На выходе сумматора 7 образуются сигналы кода разности (-ах + Ъ), которые поступают параллельно на выходы блока 9 и на входы второго сомножителя умножителя 4, на входах первого слагаемого которого по-прежнему сох35 раняются сигналы кода у(а). На выходе умножителя 4 образуются сигналы кода результата умножения ср(а) к

«(-а х + Ъ), которые поступают на (11 входы сумматора 6.

В случае, если сигналы, поступившие на входы блока 9, не образуют нулевой код, т.е. (-ах + b) ФО, на выходе 21 блока 9 появляется следующий (второй) импульс, который поступает на вход синхронизации сумматора 6 и на его выходе устанавливаются. сигналы кода новой (второй) итерации х = х " + tp(a) (-а.х +b).

Описанный итерационный процесс продолжается в блоках 3, 4, 6, 7 и 8 с дискретностью поступления импульсов на вход синхронизации сумматора .

6 до тех пор, пока разность (-ах 1 + Ь), получаемая в сумматоре

1М

7,,йе станет меньше величины младшего разряда, чему соответствуют два кода О, 00...0 или 1, 11...1 в

-1517026 результата которого соединены с выходами первого сумматора, выходы регистра делителя соединены с соот- ветствующими информационными входа- ми первого сомножителя первого матричного умножителя, о т л и ч а юш е е с я тем, что, с целью сокрашения аппаратурных затрат, в него введены группа элементов НЕ, блок приближенного вычисления обратной величины и блок синхронизации, выход которого соединен с синхровходом первого сумматора, выходы которого соединены с соответствуюшими информационными входами второго сомножителя первого матричного умножителя, выходы которого соединены соответственно с входами элементсв НЕ группы, выходы которых соединены с соответствующими входами первого слагаемого второго сумматора, входы второго слагаемого которого соединены соответственно с выходами регистра делимого, а вход переноса с входом логической единицы устройства, управляющий вход которого соединен с входами разрешения записи регистров делимого и делителя и входом сброса первого сумматора, информационные входы которого соецинены соответственно с выходами второго матричного умножителя, информационные входы первого сомножителя которого соед ыены с соответствующими выходами блока приближенного вычисления обратной величины, входы которого соединены с соответствующими выходами регистра делителя, выходы второго сумматора соединены с соответствующими информационными входаФ ми второго сомножителя второго матричного умножителя и входами блока синхронизации.

2. Устройство по п. 1, о т л и— ч а ю щ е е с я тем, что блок приближенного вычисления обратной величи15 ны содержит группу элементов НЕ и комбинационный сумматор, причем входы блока, кроме первого, соответствующего старшему разряду делителя, соединены соответственно с входами элементов HE группы, выходы которых и первый вход блока соединены с соответствующими входами первого слагаемого комбинационного сумматора со сдвигом на один разряд в сторону старших разрядов, входы второго слагаемого которого соединены с входом логического нуля устройства, вход логической единицы которого соединен с входами переноса и младшего раз30 ряда первого слагаемого комбинационного сумматора, выходы которого соединены с соответствующими выходами блока, 15! 7026

С ос т ав ит ель Е . Myps ни а

Техред Л.Олийнык Корректор М. Шароши

Редактор О. Юрковецкая

Заказ 6391/51 Тираж 668 Подписное

ВНИИПИ Государственного комитета по изобретениям и открытиям при ГКНТ СССР

113035, Москва, Ж-35, Раушская наб., д. 4/5

Производственно-издательский комбинат "Патент", г. Ужгород, ул. Гагарина, 101