Микропрограммное устройство управления

Иллюстрации

Показать всеРеферат

Изобретение относится к вычислительной технике и может быть использовано в автоматизированных системах програмного логического управления технологическими процессами. Цель изобретения - повышение быстродействия. Устройство содержит первый блок памяти 1, регистры адреса 2 и микрокоманд 3, с первого по третий мультикомпрессоры 4, 5, 6, второй блок памяти 7, дешифратор 8, RS - триггер 9, счетный триггер 10, блок синхронизации 11, элемент И-ИЛИ 12, элемент ИЛИ 13 и элемент И 14. 2 ил.

СОЮЗ СОВЕТСКИХ

СОЦИАЛИСТИЧЕСКИХ

КСПМЬЛИК

„„SU„„1517028 . А1 (51)4 С 06 Г 9/22

ОПИСАНИЕ ИЗОБРЕТЕНИЯ

К А BTOPCKOMY СВИДЕТЕЛЬСТВУ

ГОСУДАРСТВЕННЫЙ КОМИТЕТ

ПО ИЗОБРЕТЕНИЯМ И ОТНРЬП ИЯМ

ПРИ ГКНТ СССР (21 ) 4404986/24-24 (22) 01.03.88 (46) 23 ° 10,89. Бюл, !II 39 (72) В.С.Харченко, Г.H.Òèìîíüêèí, В.П.Улитенко, С.Ф.Тюрин, С.Н.Ткаченко и Б.О.Сперанский (53) 681.3 (088.8) (56) Авторское свидетельство СССР

И 1140!21, кл. С 06 Г 9/22, 1984.

Майоров С,А., Новиков Г.И. Структура электронных вычислительных машин.-Л.: Машиностроение, 1979, с, 314 ,рис. 10.4.

2 (54) МИКРОПРОГРАММНОЕ УСТРОЛСТВО УПРАВЛЕНИЯ (57) Изобретение относится к вычислительной технике и может быть использовано в автоматизированных системах программного логического управления технологическими процессами. Цель изобретения — повышение быстродействия, Устройство содержит первый блок памяти 1, регистры адреса 2 и микрокоманд 3, с первого по третий мультиплексоры 4-6, второй блок памяти 7, дешифратор 8, RS-триггер 9, счетный

4 триггер 10, блок синхронизации 11 элемент И-ИЛИ 12, элемент ИЛИ 13 и элемент И 14, 2 ил, 1517028

1Ii1обРетение относится к вычислительной технике и Может быть использовано в автоматизированных системах г«ро гр аммпо го логического управления

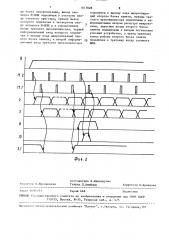

5 технологическими «троцессами, Цел«.ю изобретения является повыше«н с быстродействия устройства, 11а фиг. представлена функциональ««ая схема микропрограммного устройст- !р

I5ë упр..вле««пя; на фиг, 2 — временная диаграмма работы устройства, t

1IIIIcpol.po1.I«a IIoe устройство управления содержит первый блок памяти, нме«о«««««й выход 1, 1 кода адреса, старvill!I Разряд 1 ° 1,! кода и адреса, выход 1, 2 кода условия и выход 1, 3 код» м«. кроо пе р аций, регистр 2 адреса, р е ги с тр 3 ми кро команд, имеющий ьыхоj,II «.Риз««аков ко««ца командbl 3 ° 1 H KQH- 20 ца работы 3 ° 2, с .«ервого по третий мультиплексоры 4-6, второй блок 7 пакят««> имеющий вь«ход 7, 1 кода мпкроопер 1«jII«1 и «зых;«jI, 7. 2 приз нака конца работы, деши,«Ратор 8, RS-триггер 9, 25

< чет«г:,«««триггер 10, блок 11 синхронизации, ««мс -с«щ«-«й выходы 11, и 11. 2

i.еР во го н втopo I Режимов синхр онпз а1,IIII, эл l«eнт И;«И 12, элемент ИПИ 13, входы 15 код о«тержии, щ

««ь«хо;.i:i 16 «икрао««граций > вход 17 пус.:», "..:«д 18 останова и входы 19 логичсск:«х усло«1««й. !

1««кропрс граммное устройство управлеlii я раоо а T следующим образом, 11а вход«i 15 устройства подается код операции, а па вход 17 пуска — импульс ««уска, по которому устанавливается в "1" FS-триггер 9, Выхоцной сиг«««тл триггсра 9 з апускает блок 11 CHH- >0 хро ;«.«ации, который начинает генериро«а!1,1««е «еперекрывающиеся последовате-, л«,»oc vll импульсов на выходах 11. 1 и

11, 2, Б исходном положении все регистре«п тр ггерь«об«тут«е««ь«, (цепи не lo

«т зз;««ь«) . г«оэ тому информация с выходов

"Iy ыыт ««« ксора 4 записывается в ре«-ис iр 2 по з а;«нему фронту импульса ; "rvI ioäo 11, 2 блока 11, так как акт«!а «Р«. « э«I Ilc!« I«bi I («нвер сный ) в од эле-50 мент,..l 14. Выходные сигналы регистра

2 адрс у:"",ò первый блок 1 памяти, и на его «ь: дах уст;навливается информа-!

IIIII; » в: I. .: де « ° 1 — адрес следующей

; чей,» ii:i -i» г«, старший разряд 1, 1 ° 1 вы:.«от«;: 1, 1» с польз у ется для б езуслов-!

ioi. фар;;-Рования адреса следующеи я . «кп «змяти, на выходе 1.2 устанав:".i;».пегc> « 1 логического условия, поступающего на мультиплексор 5 ° При наличии нулевой информации на выходе

1. 2 мультиплексор 5 коммутирует на свой выход информацию с выхода 1, I I первого блока памяти и происходит безусловное формирование адреса следующей ячейки памяти независимо от логических условий на входах 19, Па выходе 1,3 первого блока 1 памяти устанавливается информация микроопераций, поступающая на мультиплексор б, которая и коммутируется на его выходы, так как счетный триггер 10 управляющий его входами, обнулен, Информация микроопераций записывается в регистр 3 по заднему фронту импульса на выходе 11.! блока 11 синхронизации, Таким образом> на выходах 16 устройства устанавливается информация микроопераций, а на выход 3 ° 1 регистра 3 подается логическая "1", По следующему импульсу на выходе 11,2 блока 11 синхронизации в регистр 2 с выходов мультиплексора 4 записывается адрес очередной ячейки первого блока 1 памяти. С первого блока 1 памяти вновь считывается информация об адресе следующей ячейки памя ги (выход 1,1), коде логических условий (выход 1.2) и микрооперациях (выход 1,3), В зависимости от логических условий, кода логических условий выход 1.1 в конкатенации с выходом мультиплексора

5 формируют адрес следующей ячейки памяти, Так же по импульсу на выходе

11.1 блока 11 очередная информация микроопераций записывается в регистр

3 и устанавливается на выходах 16 устройства. Далее устройство работает аналогично до тех пор, пока на выходе

3,1 регистра 3 не появится логический

"0", свидетельствующий о завершении команды, Тогда в регистр 2 будет записан адрес очередной команды с входов 15 кода операции.

Далее устройство работает аналогично до появления на выходе 3, 2 регистра 3 логической "!", свидетельствующей об окончании работы, Это приводит к сбросу RS-триггера 9 по второму входу элемента ИЛИ 13. В связи с этим останавливается блок 11 синхронизации и работа устройства завершается, RS — триггер 9 может быть также обнулен сигналом на входе 18 останова по первому входу элемента

ИЛИ 13 °

151702

Причем по окончании обработки очередного кода, операции, поступившего на входы 15 устройства, на выходе 3.1 регистра 3 устанавливается сигнал логической "1", который активирует вход разрешения дешифратора 8, дешифрующего код операции с соответствун»щих входов 15 устройства, В случае, если этот код соответствует операции по вычислению системы булевых функций, активируется выход дешифратора

8, Выход дешифратора Я активирует первый вход элемента И-ИЛИ 12> блокирует по первому входу элемент И 14, поэто- 15 му очередной импульс на выходе 11,2 блока 11 по второму входу элемента

И-ИЛИ 12 задним фронтом устанавливает счетный триггер 10, Выходной сигнал счетного триггера 10, равный логичес- 20 кой "1", активирует четвертый нход элемента И-ИЛИ 12 и управляющий вход мультиплексора 6, в связи с чем он коммутирует на свои выходы выход кода микроопераций второго блока 7 па- 25 мяти. Последний реализует аппаратно заданную систему булевых функций над аргументами логических условий, выставленных на нходах 19 устройства, Поэтому управляющие сигналы, сформированные на выходе 7,1 по импульсу на выходе 11,1 блока 11 синхрониз ации, записываются в регистр 3 и устанавливаются на выходах 16 устройства, Одновременно этим же импульсом по третьему входу элемента И-ИЛИ 12 обнуляется счетный триггер 10, На вхо ды 15 кода операции поступает код очередной операции, поэтому мультиплексор 4 коммутирует на свои выходы 40 информацию, По очередному импульсу на выходе 11,2 блока 11 информация с входов 15 устройства записывается в регистр 2, так как первый вход элемента И 14 не активирован выходом де- 45 шифратора 8 ° В дальнейшем устройство работает аналогично, При появлении на выходе 7,2 второго блока 7 памяти логической "1" по третьему выходу элемента ИЛИ 13 обнуляется RS-триггер 9, и работа устройства прекращается, Фор мул а иэобретения

Иикропрогра»»мное устройство управ35 ления, содержащее блок синхрониэ ации, первый блок памяти, регистр адреса, регистр микрокоманд, первый и второй мультиплексоры, i,S-триггер и элемент

8 6

ИЛИ, причем первый и»»формацион»»» и вход первой группь» первого мультиплексора соединен с выходом второго мультиплексора, первый информационный вход которого соединен с выходом модифицируемого разряда адреса первого блока памяти, выходы поля немодифицируемых разрядов адреса которого соединены с остальными информационными входами первой группы первого мультиплексора, остальные информационные входы второго мультиплексора являются входами логических условий устройства, управляющий вход второго мультиплексора подключен к выходу кода условий первого блока памяти, вторая группа информационных входов первого мультиплексора является входами кода операции устройства, упранлякщий вход первого мультиплексора подключен к выходу признака конца команды регистра микрокоманд, выходы первого мультиплексора подключены к информационным входам регистра адреса, выходы которого подключены к адресным входам первого блока памяти, S-вход RБSтриггера является входом пуска устройства, R -вход RS — триггера подключен к выходу элемента ИЛ!1, первый вход которого янляется входом останова устройства, а второй вход элемента ИЛИ подключен к выходу признака конца работы регистра микрокомаид, прямой выход RS-триггера подключен к входу пуска блока синхронизации, первый выход котороrc подключен к входу синхронизации регистре ».мкрокоманд, выходы кода микроопераций которого являются одноимен»»ыми Hhl ходами устройства, о т л и и а ю— щ е е с я тем, что, с целью и выше»»ия быстродействия, оно содержит второй блок памяти, счетный триггер, третий мульти.1лексор, дешифратор, элене нт

И- ИЛИ н элемент Н, при;ем информационные входы дешифратора подкл» чеиы к входам кода операции устройства, а вход разрешения депифратора подключен к выходу признака конца команды регистра микрокомаид, выход дешифратора подключен к первому входу элемента И и к первому входу элементе И-!1»И, второй вход которого подключеи к к,iходу второго блока си»»хро»»иэ звi.i*. и к второму входу элемента И, »;ь|х(ii, 31e мента И подключен к вхсду е»»ихр»и»»»э»ции регистра адреса, трет»»й» вх.,и э:ieмента И-ИЛИ подключен к»»с р»,;. »у . мхов

1517028

Дание. 2

Составитель В. Криворучко

Техред Л.Олийнык

Корректор Q.Êðàâöoâà

Редактор О,Юрковецкая

Тираж 668

Подписное

Заказ 639! /51

ВНИИПИ Государственного комитета по изобретениям и открытиям при ГКНТ СССР

113035, Москва, Ж-35, Раушская наб., д. 4/5

Произ лоде тленно-издательский комбинат "Патент", г. Ужгород, ул . Гагарина, 101 ду блока синхронизации, выход элемента И-ИЛИ подключен к счетному входу счетного триггера, прямой выход которого подключен к четвертому входу элемента И-ИЛИ и к управляющему входу третьего мультиплексора, первый информационный вход которого подключен к выходу кода микроопераций первого блока памяти, а второй информационный вход третьего мультиплексора подключен к выходу кода микроопераций второго блока памяти, выходы третьего мультиплексора подключены к ин5 формационным входам регистра микрокоманд, адресные входы второго блока памяти подключены к входам логических условий устройства, а выход признака конца работы второго блока памяти подключен к третьему входу элемента

ИПИ.