Способ ступенчатого регулирования частоты вращения асинхронного электродвигателя с тиристорным коммутатором

Иллюстрации

Показать всеРеферат

Изобретение относится к электротехнике и может быть использовано для управления электроприводами общепромышленных механизмов, в частности шахтных скребковых конвейеров, при питании электродвигателей квазисинусоидальным напряжением пониженной частоты. Целью изобретения является упрощение за счет формирования напряжений при переключении двигателя с фиксированной пониженной частотой вращения на номинальную частоту вращения. Устройство для реализации способа содержит тиристорный коммутатор 1, формирователь 9 синхроимпульсов, таймер 10, логические элементы 2И 11-25, 3И 26, 27, 4И 28, 2ИЛИ 29-31, 3ИЛИ 32, 3ИЛИ-НЕ 33, 4ИЛИ 34, 35, делитель 36 частоты, распределитель 37 импульсов, кольцевой распределитель 38 импульсов, блок 39 гальванической развязки, дифференцирующую цепь 40 и переключатели 41, 42. Предлагаемый способ и устройство для его реализации позволяют при сравнительно простой реализации обеспечить ступенчатый запуск двигателя с соотношением частот F<SB POS="POST">с</SB>/F<SB POS="POST">м</SB>=7 F<SB POS="POST">с</SB>/F<SB POS="POST">м</SB>=4 F<SB POS="POST">с</SB>/F<SB POS="POST">м</SB>=3, где F<SB POS="POST">с</SB> - частота напряжения сети, F<SB POS="POST">м</SB>-частота модулирующих напряжений. 3 ил.

СОЮЗ СОВЕТСКИХ

СОЦИАЛИСТИЧЕСКИХ

РЕСПУБЛИК (51)4 Н 02 Р 7 42

ОПИСАНИЕ ИЗОБРЕТЕНИЯ

К А ВТОРСКОМУ СВИДЕТЕЛЬСТВУ

ГОСУДАРСТ8ЕННЫЙ КОМИТЕТ

ПО ИЗОБРЕТЕНИЯМ И ОТКРЫТИЯМ

ПРИ fXHT СССР (21) 4142144/24-07 (22) 04.11.86 (46) 23.10.89. Бюл. 11- 39 (71) Донецкий политехнический институт (72) И.Т, Сидоренко, К.Н, Маренич и В,Б. Шевчик (53) 621.316.718.5(088.8) (56) Авторское свидетельство СССР

У 1221094, кл. В 65 С 23/00, 1986.

Авторское свидетельство СССР

Ф 1376209, кл. Н 02 P 7/42, 1985.

„„SU„„1517107 А 1

2 (54) СПОСОБ СТУПЕНЧАТОГО РЕГУЛИРОВАНИЯ ЧАСТОТЫ ВРАЩЕНИЯ АСИНХРОННОГО

ЭЛЕКТРОДВИГАТЕЛЯ С ТИРИСТОРНЫМ КОММУТАТОРОМ (57) Изобретение относится к электротехнике и может быть использовано для управления электроприводами общепромышленных механизмов, в частности шахтных скребковых конвейеров, при питании электродвигателей квазисинусоидальным напряжением пониженной частоты. Целью изобретения явля1517107

10 ется упрощение за счет формирования напряжений при переключении двигателя с фиксированной пониженной частотой вращения на номинальную частоту вращения. Устройство для реализации способа содержит тиристорный коммутатор

1, формирователь 9 синхроимпульсов, таймер 10, логические элементы 2И

11-25, ЗИ 26, 27, 4И 28, 2ИПИ 29-31, ЗИЛИ 32, ЗИЛИ-НЕ 33, 4ИЛИ 34, 35, делитель 36 частоты, распределитель 37

Изобретение относится к электротехнике и может быть использовано для управления электроприводами общепромышленных механизмов, в частности шахтных скребковых конвейеров, при питании электродвигателей квазисинусоидальным напряжением пониженной частоты.

Целью изобретения является упрощение за счет формирования напряжений при переключении электродвигателя с фиксированной пониженной частотой вращения на номинальную частоту вращения.

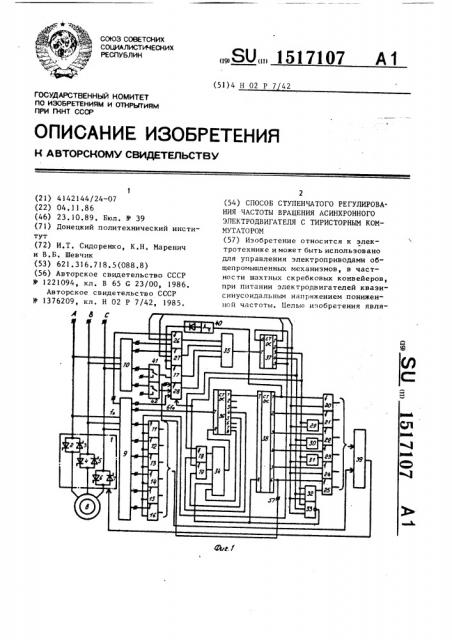

На фиг. 1 приведена структурная схема устройства для реализации способа ступенчатого регулирования частоты вращения асинхронного электродвигателя с тиристорным коммутатором," на фиг, 2 — схема формирователя синхро35 ниэирующих импульсов; на фиг. 3 — временные диаграммы, поясняющие работу устройства.

Устройство (фиг. 1) для реализации „ способа ступенчатого регулирования частоты вращения асинхрс>нного электродвигателя содержит тиристорный коммутатор 1, состоящий из трех пар встречно-параллельно соединенных ти- 45 рис тбров 2-7, включен Iblx между зажимами питающей сети и статорными обмотками синхронного электродвигателя 8, формирователь 9 синхронизирующих импульсов, таймер 10, пятнадцать

50 логических элементов 2 И 11-25, два логических элемента 3 И 26 и 27, логический элемент 4 И 28, три логических элемента 2 ИПИ 29-31, логический элемент 3 ИЛИ 32, логический элемент

3 KIN-HE 33, два логических элемента 4 ИПИ 34 и 35, делитель 36 частоты, распределитель 37 импульсов, кольцевой распределитель 38 импульимпульсов, кольцевой распределитель

38 импульсов, блок 39 гальванической развязки, дифференцирующую цепь 40 и переключатели 41, 42. Предлагаемый способ и устройство для его реализации позволяют при сравнительно простой реализации обеспечить ступенчатый запуск двигателя с соотношением часfñ/fì 7; fñ/f„4; f,/fÄ=3, где частота напряжения сети, f — частота модулирующих напряжений. 3 ил, сов, блок 39 гальванической развязки, дифференцирующую цепь 40, два переключателя 41 и 42.

Выходы формирователя 9 синхроимпульсов и таймера 10 подключены к зажимам питающей сети, первый — шестой выходы формирователя 9 импульсов соединены с оотв етств енно с первыми входами первого — шестого логических элементов 2 И 11-16, выходы которых соединены с соответствующими первыми входами блока 39 гальванической развязки, вторые входы которого соединены с выходами десятого-четырнадцатого и шестнадцатого логических элементов 2 И 20-25, выходы блока 39 гальванической развязки соединены с управляющими входами тиристорного коммутатора 1.Седьмой выход формирователя 9 синхроимпульсов соединен со счетным входом делителя 36 частоты, вход обнуления которого соединен с выходом первого логического элемента

4 ИЛИ 34, первый и второй входы которого соединены с выходами соответственно восьмого и девятого логических элементов 2 И 18 и 19. Восьмой и девятый выходы формирователя 9 синхроимпульсов соединены с первыми входами соответственно логического элемента

4 И 28 и первого логического элемента Э И 26. Первый и второй выходы таймера 10 соединены соответственно с вторым входом первого логического элемента 3 К 26 и первым входом второгс> логического элемента 3 И 27. Третий и четвертый выходы таймера 10 соединены с первыми входами соответственно первого 41 и второго 42 переключателей, вторые входы которых предназначены для подачи команд обратной связи. Выходы первого и второго переключателей соединены соответ1517107 ственно с первым входом седьмого логического элемента 2 И 17 и вторым входом логического элемента 4 И 28.

Вторые входы седьмого логического элемента 2 И 17 и второго логического элемента 3 И 27 объединены и подключены к выходу дифференцирующей цепи 40. Выходы первого и второго логических элементов 3 И 26 и 27, седь- 10 мого логического элемента 2 И 17 и логического элемента 4 И 28 соединены с соответствующими входами второго логического элемента 4 ИЛИ 35, выход которого подключен к тактирующему 15 входу распределителя 37 импульсов, первый выход которого соединен с третьим входом первого логического элемента 3 И 26, второй выход распределителя 37 импульсов соединен с тре- 20 тьим входом второго логического элемента 3 И 27 и с первыми входами десятого и четырнадцатого логических элементов 2 И 20 и 24, первого-третьего логических элементов 2 ИЛИ 2931, логического элемента 3 ИЛИ 32 и логического элемента 3 ИЛИ-НЕ 33.

Третий выход распределителя 37 импульсов соединен с третьим входом логического элемента 4И 28, первым входом девятого логического элемента

2 И !9, вторыми входами первого и третьего логических элементов 2 ИЛИ

29 и 31, логического элемента 3 ИЛИ

32 и логического элемента 3 H™H-НЕ

33. Четвертый выход распределителя

37 импульсов соединен с первым входом восьмого логического элемента 2 И 18, вторым входом второго логического элемента 2 ИЛИ 30 и третьими входами 40 логического элемента, 3 ИЛИ 32 и логического элемента 3 ИЛИ-НЕ 33, выход которого соединен с входом обнуления кольцевого распределителя 38 импульсов и третьим входом первого логи- 45 ческого элемента 4 ИЛИ 34. Пятый выход распределителя 37 импульсов соединен с входом остановки распределителя 37 импупьсов и вторыми входами первого-шестого логических элементов

2 И 11-16. Первые входы одиннадцатого-тринадцатого и пятнадцатого логических элементов 2 И 21-23 и 25 соединены с выходами соответственно первого-третьего логических элементов

2 ИЛИ 29-31 и логического элемента

3. KIH 32. Вторые входы десятого-пятнадцатого логических элементов 2 И

20-25 соединены соответственно с пер.вым-шестым выходами кольцевого распределителя 38 импульсов, первый и шестой выходы которого соединены дополнительно соответственно с входом дифференцирующей цепи 40 и с четвертым входом логического элемента 4 И

28. Первый выход делителя 36 частоты соединен с тактирующим входом кольцевого распределителя 38 импульсов, второй-четвертый выходы делителя 36 частоты соединены соответственно с вторыми входами восьмого и девятого логических элементов 2 И !8 и 19 и с четвертым входом первого логического элемента 4 ИЛИ 34.

Формирователь 9 синхронизирующих импульсов содержит (фиг. 2) трехфазный трансформатор 43, шесть компараторов 44-49, шесть дифференцирующих цепочек 50-55, логический элемент 6

ИЛИ 56. Входы компараторов 44-49 подключены к вторичным обмоткам трехфазного трансформатора 43, выводы первичных обмоток которого образуют входы формирователя 9 синхронизирующих импульсов. Выходы компараторов

44-49, образующие первый-шестой выходы формирователя 9 синхронизирующих импульсов, через соответствующие дифференцируюшие цепочки 50-55 соединены с входами логического элемента 6 ИЛИ

56 выход которого образует седьмой выход формирователя 9 синхронизирующих импульсов, выходы второй и шестой дифференцирующих цепочек 51 и 55 образуют соответственно девятый и восьмой выходы формирователя 9 синхронизирующих импульсов .

Устройство для реализации способа ступенчатого регулирования частоты вращения асинхронного электродвигателя с тиристорным коммутатором работает следующим образом.

При формировании трехфазной системы напряжений модуляции, частота которых задана соотношением Ед/f„7(k !

) в исходном состоянии на первых выходах делителя 36 частоты, распределителя 37 импульсов, кольцевого распределителя 38 импульсов устанавливается "1" на остальных их выходах — "0", Поэтому на входы логического элемента 3 ИЛИ-НЕ 33 поданы уровни "0", определяющие уровень "1" на его выходе, подаваемый на вход обнуления кольцевого распределителя

38 импульсов и через логический элемент 4 ИЛИ 34 — на вход обнуления

1517107

45 делителя 36 частоты. Этим запрещается переключение делителя 36 частоты и кольцевого распределителя 38 импульсов, На вход формирователя 9 синхронизирующих импульсов подается трехфазное напряжение сети частоты Й . Шесть компараторов 44-49 формирователя 9 формируют прямоугольные импульсы, совпадающие с участками превышения мгновенными значениями напряжений фаэ: А, В, С, В, С, А мгновенных значений напряжений фаэ соответственно В, С, А, А, В, С. Эти импульсы по- 15 ступают на первый-шестой выходы формирователя 9 синхронизирующих импульсов и на дифференцирующие цепи 50-55.

С выходов последних импульсы ограниченной длительности, совпадающие с 20 моментами равенства мгновенных значений напряжений двух фаз трехфаэной сети, подаются на логический элемент

6 ИЛИ 56. С его выхода последовательность импульсов U (фиг. 3) час- 25 тоты 6 f, подается на счетный вход делителя 36 частоты. На вход таймера

10 так же подается напряжение сети.

При появлении "1" на первом выходе таймера 10 импульс, синхронизирован- 30 ный с напряжением сети (например, с моментом равенства мгновенных значений напряжений U и U c в положительной области), снимаемый с девятого выхода формирователя 9 синхронизирующих импульсов, поступит через логические элементы 3 И 26, 4 ИЛИ 35 на тактирующий вход распределителя

37, перенеся "1" с его первого выхода на второй. Это определит появ- 4р ление "0" на входах обнуления делителя 36 частоты и кольцевого распределителя 38 импульсов, При этом на вторых входах логических элементов

2 И (20-25) устанавливается "1", Четвертый выход делителя 36 частоты связан через логический элемент

4 ИЛИ 34 с входом обнуления этого же делителя. Поэтому делитель 36 производит деление частоты синхронизирующих импульсов U на семь (переводится в исходное состояние каждым .восьмым импульсом). С выхода делителя 36 импульсы U< (фиг. 3) с частотой следования B семь раз меньшей частоты импульсов U поступают на

1 тактирующий вход кольцевого распределителя 38. Его выходные импульсы через логические элементы 2 И 20-25 поступают на соответствующие входы блока 39 гальванической развязки, где расширяются в три раза и поступают в виде пакетов отпирающих импульсов (фиг, 5 ) на цепь управления тиристоров 2-7 коммутатора 1.

Импульсы П -U > образуют трехфазную систему модулирующих напряжений, частота которых f„ задана в соотношении f /f 7 (f /f 6k+1 при

k l). При этом на тиристоры анодной группы 2, 4 и 6 подают импульсы соответс тв енно U U и U» соответствующие положительной полярности модулирующих напряжений, а на тиристоры катодной группы 3, 5 и 7 подают импульcbI соответственно Б,1, U 6 H U8 сооТ ветствующие отрицательной полярности модулирующих напряжений. На фиг. 3

ЭДС самоиндукции ротора двигателя (е„, е, е с показаны пунктиром) . совпадают с напряжением модуляции.

Таким образом, на выходе коммутатора формируется трехфазная система квазисинусоидальных напряжений (U„, Б, U ) пониженной частоты. При пос явлении на втором выходе таймера 10 команды на переключение режимов электропитания электродвигателя 8 (уровень "1") по истечении работы очередного канала (например, шестого) кольцевого распределителя 38 импульсов в момент Г импульс ограниченЯ ной длительности с выхода дифференц1рующей цепи 40 через логические элементы 3 И 27, 4 ИЛИ 35 поступает на тактирующий вход распределителя 37 импульсов, перенося "1" с его второго выхода на третий. Этим запрещается подача сигналов управления на блок

39 гальванической развязки с первого, третьего и пятого выходов кольцевого распределителя 38. В этом случае кольцевой распределитель 38 формирует чередующиеся запрещающие и разрешающие сигналы. Последние снимаются с второго, четвертого и шестого выходов кольцевого распределителя

38 и через логические элементы 2 ИЛИ

29 и 31, 3 ИЛИ 32, а также 2 И 21, 23 и 25 и блок 39 гальванической развязки подаются на цепи управления тиристоров 2-7 коммутатора 1. Одновременно уровень "1" устанавливается на первом входе элемента 2 И 19, определяя коэффициент деления делителя

36 равный четырем. Уровень "1" устанавливается и на третьем входе логи1517107

9 ческого элемента 4 И 22, разрешая по дачу очередной команды управления на вход распределителя 37 импульсов.

Таким образом, частоту модулирующих напряжений понижают в 4 раза по сравнению с частотой напряжений сети

Ес и при этом формируют чередующиеся запрещающие и разрешающие сигналы (начиная с запрещающего) каждый дли1 2 тельностью 4 х = (поскольку с с длительность импульса, снимаемого с каждого из шести выходов кольцевого

1 распределителя 38, составляет 4 — ) с

При этом управляющие импульсы U -U подают на соответствующие тиристоры коммутатора 1 на интервалах существования разрешающих сигналов, В этом случае на втором выходе кольцевого распределителя 38 формируются импульсы U !, Ь „ на четвертом

HMH ëb b U » U g H U g B шестом импульсы U, U < U (интервал времени 7,— на фиг. 3) . Этим достигается плавное повышение частоты вращения ротора двигателя 8, что отражается изменением кривых ЭДС самоиндукции ротора. Последние на фиг. 3 совпадают с модулирующими напряжениями, формирующими кривые фазных квазисинусоидальных напряжений. В момент формирования каждого очередного импульса на выходе кольцевого распределителя 38 изменяется полярность соответствующего модулирующего напряже ния °

При появлении команды на дальнейшее повьппение частоты вращения ротора электродвигателя (уровень 1" на четвертом выходе таймера 10 или уровень

"1" на втором входе переключателя 42 при использовании команд обратной связи по частоте вращения электродвигателя) уровень "1" подается на второй вход логического элемента 4 И

28. На первый и четвертый его входы подаются синхросигналы соответственно с восьмого выхода формирователя

9 и с шестого выхода кольцевого распределителя 38 ° В момент одновременного поступления сигналов на все входы логического элемента 4 И 28 с его выхода уровень "1" поступает через логический элемент 4 ИЛИ 35 на тактирующий вход распределителя 37, перенося "1" с его третьего выхода на четвертый. Уровень "1" подается на входы логических элементов 2 ИЛИ 30 и 3 HJIH 32, раз5 решая подачу на тиристоры 2-7 коммутатора 1 управляющих сигналов через блок 39 гальванической развязки с третьего и шестого выходов кольцевого распределителя 38. Этим определя10 ется соотношение длительностей чередующихся запрещающих и разрешающих сигналов, как 2:1. При этом импульсы

U3» U < и U формируются сигналом с третьего выхода кольцевого распреде-!

5 лителя 38, а импульсы U, U q u U с шестого выхода, Уровень "1" подается на вход логического элемента

3 ИЛИ-HE 33, разрешая работу делителя 36 и частоты кольцевого распреде20 лителя 38 и на первый вход логического элемента 2 И 18 устанавливая коэффициент деления делителя 36 равный трем.

Таким образом, в момент изменения полярности одного из модулирующих напряжений, частоту последних понижают в три раза по сравнению с частотой напряжения сети f с и при этом формируют чередующиеся запрещающие и раз30 решающие сигналы. Длительность paspeшающих сигналов задают равной 3 "

1 3 к cf а запрещающих 2 . Управс

fc ляющие импульсы подают на тиристоры

35 на интервалах существования разрешающих сигналов. При этом отрезки синусоидальных напряжений сети, предшествующие моменту, сформированы в момент окончания запрещающего сиг40 нала при частоте модуляции f соотношения f /f =4 и принадлежат одновременно напряжениям модуляции этой частоты и формулируемой в дальнейшем частоты модуляции Е соотношения

45 f /f„, 3. Это позволяет плавно увеличить частоту вращения ротора электродвигателя 8 до уровня соответствующего заданной частоте модулирующих напряжений (на участке — 7з фиг. 3).

50 В этом случае в момент появления каждого очередного импульса на любом из выходов кольцевого распределителя

38 также изменяется полярность. соответствующего модулирующего напряже55 ния, совпадающего с ЭДС ротора, приведенными на фиг. 3.

При поступлении команды на подачу к электродвигателю 8 напряжения сети

1517107

12 (уровень "1" на третьем выходе таймера 10 или уровень "1" на втором входе переключателя 41) уровень ".1" подается на первый вход логического элемента 2 И 17, По истечении цикла

5 работы кольцевого распределителя 38 в момент уровень "1" поступает на тактирующий вход распределителя 37, перенося уровень "1" с его четвертого выхода на пятый. Этим вводится запрет на подачу в блок 39 гальванической развязки выходных импульсов кольцевого распределителя 38. Отсутствие уровней "1" на втором — четвер- 15 том выходах распределителя 37 определяют появление уровня "1" на выходе логического элемента Э ИЛИ-НЕ 33 и подачу этого уровня на входы обнуления делителя 36 и кольцевого распре- 2О делителя 38 импульсов, запрещая их работу. Формирование двухтактных напряжений на выходе коммутатора 1 прекращается. Одновременно уровень

"1" подается на вход остановки Q рас- 25 пределителя 37, прекращая процесс переноса команд на его выходах, и на вторые входы логических элементов 2 И 11-16, разрешая подачу прямоугольных импульсов управления с ЭО первых шести выходов формирователя

9 на блок 39 гальванической развязки.

На электродвигатель 8 при этом подается напряжение сети.

Таким образом, при управлении электродвигателем согласно предлагаемому способу упрощается процесс формирования напряжения пониженных фиксированных частот и переключение электродвигателя во вращающемся состоянии от источника квазисинусоидального напряжения пониженной частоты к трехфазной сети, Формула из обретения 45

Способ ступенчатого регулирования частоты вращения асинхронного электродвигателя с тиристорным коммутатором, при котором формируют соответственно первое, второе и третье модули- 50 рующие напряжения, образующие трехфазную систему с фиксированной частотой, соответствующей заданной частоте вращения электродвигателя и определяемой иэ соотношения f /f „ - 55 6K+1, подают управляющие импульсы для тиристоров анодной группы коммутатора при положительной полярности соответствующих модулирующих напряжений, а для тиристоров катодной группы ком-. мутатора при отрицательной полярности соответствующих модулирующих напряжений, отличающийся тем, что, с целью упрощения за счет формирования напряжений при переключении электродвигателя с фиксированной пониженной частоты вращения на номинальную частоту вращения, при заданной частоте модулирующих напряжений в соотношении f,/f =7, определяют момент изменения полярности любого иэ модулирующих напряжений и с этого момента задают частоту модулирующих напряжений в соотношении f,/f„=4, формируют чередующиеся запрещающие и разрешающие импульсы, каждый дли2 тельностью, начиная с запрещаюс щего, и подают управляющие импульсы на соответствующие тиристоры коммутатора на интервалах существования разрешающих импульсов, после соответствующего повьппения частоты вращения электродвигателя на интервале существования разрешающего импульса определяют момент времени, отстоящий от начала разрешающего импульса на 1/2 Г„ и синхронизированный с напр;жением сети, и с этого момента задают частоту модулирующих напряжений в соотношении f /f =Ç, формируют чередующиеся запирающие и разрешающие импульсы, начиная с запрещающего и задавая длительность запрещающих импульсов, равную 1/f, а длительность разрешающих импульсов, равную

1/?fee и подают управляющие импульсы на соответствующие тиристоры коммутатора на интервалах существования разрешающих импульсов, а после соответствующего повышения частоты вращения электродвигателя определяют момент изменения полярности любого из модулирующих напряжения и подают на электродвигатель трехфазное напряжение сетевой частоты, где fс — частота напряжения сети, f „„ — частота модулирующих напряжений,-К вЂ” 1, 2, 3... число натурального ряда.

1517107

1 " и, и

v, Составитель С. Поэднухов

Редактор Г. Гербер Техред А.Кравчук Корректор Л. Бескид

Заказ 6399/55 Тираж 551 Подписное

ВНИИПИ Государственного комитета по изобретениям и открытиям при ГКНТ СССР

113035, Москва, Ж-35, Раушская наб., д. 4/5

Производственно-издательский комбинат "Патент", г.ужгород, ул. Гагарина,101