Устройство фазовой автоподстройки частоты

Иллюстрации

Показать всеРеферат

Изобретение относится к радиотехнике. Цель изобретения - повышение быстродействия. Устройство фазовой автоподстройки частоты (ФАПЧ) содержит перестраиваемый генератор 1, делитель 2 частоты с переменным коэф. деления, фазовый детектор 3, фильтры 4 и 12 нижних частот, опорный генератор 5, выделитель 6 разностной частоты, фазовый компаратор 7, элементы ИЛИ 8 и 9, реверсивный счетчик 10, преобразователь 11 код-напряжение, преобразователь 13 временных интервалов, распределитель 14 импульсов, блок установки кода (БУК) 15, блок сравнения кодов (БСК) 16, задатчик 17 кода частоты, RS-триггер 18, коммутатор 19 и элемент задержки 20. Данное устройство позволяет за один период разностной частоты проводить измерение частотной ошибки в кольце ФАПЧ, состоящем из генератора 1, делителя 2, детектора 3 и фильтра 4, а также проводить компенсацию этой ошибки грубым каналом управления. Кроме того, использование по п.2 ф-лы БУК 15 и БСК 16, а также коммутатора 19 позволяет ограничить максимальное значение периода разностной частоты на выходе выделителя 6, что приводит к существенному сокращению времени выделения информации о частотной ошибке. Дана ил. выполнения преобразователя 13. 1 з.п. ф-лы, 2 ил.

СОЮЗ СОВЕТСКИХ

СОЦИАЛИСТИЧЕСКИХ

РЕСПУБЛИН

1 А1 (191 (Il) (su 4 Н 03 Ь 7/00. I Г

ОПИСАНИЕ ИЗОБРЕТЕНИЯ

К Д 8Т0РСКОМУ СВИ4ЕТЕЛЬСТВУ

ГОСУДАРСТВЕННЫЙ КОМИТЕТ

ПО ИЗОБРЕТЕНИЯМ И ОТКРЫТИЯМ

ПРИ ГКНТ СССР (21) 4286243/24-09 (?2) 20.07.87 (46) 30.10.89. Бюл.Р 40 (7I) Московский электротехнический институт связи (72) А.И.Кабанов (5.3) 621.396.666(088.8) (56) Авторское свидетельство СССР

1(1160564 кл. Н 03 Ь 7/10, 1983. (54) УСТРОЙСТВО ФАЗОВОЙ АВТОПОДСТРОЙКИ ЧАСТОТЫ (57) Изобретение относится к радиотехнике. Цель изобретения — повышение быстродействия. Устр-во фазовой автоподстройки частоты (ФАПЧ) содер-жит перестраиваемьп» r-p I делитель

2 частоты с переменным коэф. деления, фазовый детектор 3, фильтры 4 и 12 нижних частот, опорный r-p 5, выдели-. тель 6 раэностной частоты, фазовый компаратор 7, эл-ты ИЛИ 8 и 91 реверсивный счетчик 10, преобразователь !1

2 код-напряжение, преобразователь !3 временных интервалов, распределитель

14 импульсов, блок установки кода (БУК) !5, блок сравнения кодов (БСК)

16, задатчик 17 кода частоты, RS" триггер 18, коммутатор 19 и эл-т задержки 20. Данное устр-во позволяет за один период раэностной частоты проводить изменение частотной ошибки в кольце ФАПЧ, состоящем из г-ра 1, делителя 2, детектора 3 и фильтра 4, а также проводить компенсацию этой ошибки грубым каналом управления.

Кроме того, использование по п.2 ф-лы БУК 15 и БСК 16, а также коммутатора 19 позволяет ограничить максимальное значение периода раэиостной частоты на выходе выделителя 6, что приводит к существенному сокращению времени выделения информации о частотной ошибке. Дана ил. выполнения преобразователя 13. 1 з.п. ф-лы, 2 ил.

1518881

При изменении рабочей частоты задатчик 17 кода частоты вырябатыва> т по импульсному выходу импульс переключения частоты, который поступает на вхг>д RS-триггеря 18, устанавливая его в единичное состояние. При этом на инверсном выходе РБ-триггера 18 появляется c>f>.»àë, соответствующий нулевому потенциалу, который, поступая HQ управляющий вход фазового компаратора 7, запрещает ня время его работу. Этим же сигналом, посту50

Изобретение относится к радиотехнике и может быть использовано в широкополосных системах синхронизации и синтезаторах частоты, радиоиз5 мерительных устройствах.

Цель изобретения — повышение быстродействия °

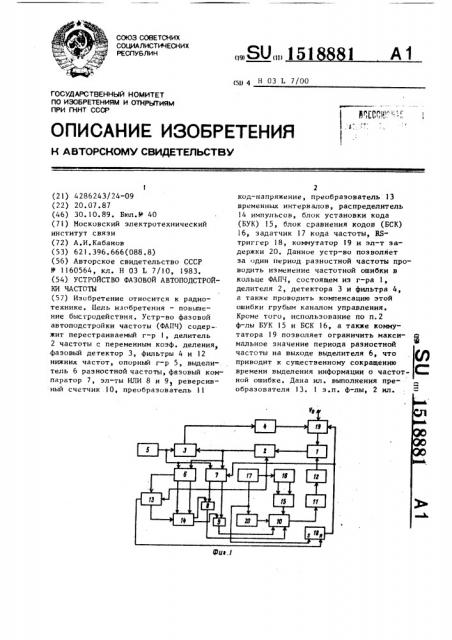

На фиг.l представлена структурная электрическая схема устройства

10 фаэовой автоподстройки частоты (ФАПЧ); на фиг.2 — структурная схема преобразователя временных интервалов устройства ФАПЧ.

Устройство фазовой автоподстройки частоты (фиг.l) содержит перестраиваемый генератор (ПГ) 1, делитель частоты с переменным коэффициентом деления (ДПКД) 2, фазовый детектор (ФД) 3, первый фильтр нижних частот

4, опорный генератор 5, выделитель раэностной частоты (ВРЧ) 6, фазовый компаратор 7, первый и второй элементы ИЛИ 8 и 9 соответственно, реверсивный счетчик 10, преобразователь 25 код — напряжение (ПКН) 11, второй ФНЧ

12, преобразователь временных ингервалов (ПВИ) 13, распределитель 14 импульсов, блок 15 установки кода, блок 16 сравнения кодов, задатчик 17 кода частоты, RS-триггер 18, коммутатор 19, элемент 20 задержки.

Преобразователь 13 временных интервалов 13 содержит первый триггер 21, первый элемент И 22, генератор пилообразного напряжения (ГПН) 23 со сбросом, интегрирующий преобразователь напряжение — код (ИПНК) 24, а также преобразователь цифра-аналог (ПЦА) 25. ИПНК 24 состоит из второго 40 триггера 26, генератора 27 импульсов, ключа 28, второго элемента И 29, интегратора 30 со сбросом и компаратора 31 напряжений, Устройство фяэовОЙ автоподстройки >15 частоты работает следующим обрязом.

I лающим на управляющий вход коммутатора

19, производится отклн>чение выхг>да

ФНЧ 4 от второго управляющего входа

ПГ I и подключение к нему источника постоянного напряжения Uy, который соединен с вторым входом коммутатора

19. Величина U» выбирается такой, при которой частота ПГ 1 соответствует середине диапазона перестройки по второму входу ПГ 1.

При этом на выходе кода задатчика !

7 кода частоты появляется новый код частоты, который поступает на управляющий вход ДПКД 2, устанавливая тем самым новый коэффициент деления частоты. Это же значение нового кода частоты поступает в блок 16 срявнения кодов, где производится его сравнение с кодом частоты, хранящимся в запоминающем элементе блока 16 сравнения кодов, и выносится оценка проведенного сравнения. Код, хранящийся в блоке

l6 сравнения кодов, соответствует средней частоте диапазона перестройки устройства фазовой автоподстройки частоты. Если код новой частоты меньше или равен коду, хранящемуся в блоке 16 сравнения кодов, то сигнал единичного уровня появляется на первом выходе, если меньше — на втором.

Блок 16 сравнения кодов управляет рабо ° гой блока 15 установки кода, на выходах которого, в зависимости от наличия единичного уровня на одном из его входов появляется один иэ кодов Х или

У, хранящихся в запоминающих элементах блока 15 установки кода. При записи кода Х в реверсивный счетчик 10 на выходе ПГ 1 устанавливается частота, равная максимальной рабочей частоте устройства фазовой автоподстройки частоты. При записи кода Y устанавливается частота ПГ 1, соответствующая минимальной рабочей частоте устройства.

Пусть для определенности в результате сравнения в блоке сравнения кодов сигнал единичного уровня появляется на первом входе. Тогда этот сигнал разрешает прохождение кода Х на выход блока 15 установки кода и далее на информационные входы реверсивного счетчика 10. Импульс переключения частоты, пройдя через элемент 20 задержки, поступает на управляющий вход реверсивного счетчика

10 н производит запись кода Х в ревер сивньп» счетчик IO. При этом частота

ПГ 1 устанавливается равной макси5 15!888 мапьной рабочей частоте устройства. Далее происходит обычная работа ДПКЛ 2 и

ВРЧ 6, в реэупьтате которой на импульсном выходе ВРЧ 6 появляются импульсы, период которых соответствует раэностной частоте между сигналами, поступающими на входы

ВРЧ 6.

HP× 6 н процессе работы определяет также знак частотного рассогласования, о чем свидетельствует сигнал высокого уровня на одном из знаковых выходов ВРЧ 6. В данном случае единичный сигнал на первом знаковом !5 выходе ВРЧ 6 разрешает прохождение сигнала с ныхода ПВИ 13 череэ распределитель 14 импульсов на первый его выход и далее через первый элемент KIH 8 на первый счетный вход реверсивного счетчика 10.

При поступлении первого импульса на вход ПВИ 13 с ВРЧ 6 начинает работу блок ПВИ !3. Первый импульс, поступивший на вход ПВИ 13, устанавливает 25 на выходе первого триггера 21 единичный уровень сигнала, который разрешает работу ГПН 23. В ГПН 23 происходит преобразование временного интервала, соответствующего раэностной частоте, 30 в постоянное напряжение. Поскольку ток через заряжающую емкость С ГПН 23 так зависит от выходного напряжегпн ния ГПН 23 — Бгпн

20 (2) Urnq = гпту C (с учетом 2), (4)

< оС глн TÐÀ3 где Т вЂ” период раэностной частоты

РАЗ на выходе ВРЧ 6.

I = С---- -, à I const (1) (Ш гп 35 гпя 1 гпн и начальное значение выходного напряжения ГПН 23 при наличии цепи сброса равно нулю, то получают 40 где c — длительность импульса на ньисоде первого триггера 21.

Второй импульс на входе ПВИ 3, 45 соответствующий окончанию периода сигнала с разностной частотой на выходе

ВРЧ 6, происходит через первый элемент

И 22 на вход установки второго триггера 26, устанавливая его в единицу. 50

Кроме того, он опрокидывает первый триггер 21 в нуль, останавливая при этом работу ГПН 23, на выходе которого устанавливается напряжение постоянного уровня. 55

При этом начинает работать ИПНК 24.

Ключ 28 замыкается и постоянное напряжение с выхода Г11Н 23 поступает на вход интегратора 30, а на выход! 6

ПВИ !3 начинают поступать импульсы с генератора 27 импульсов через второй элемент И 29. Эти импульсы поступают на счетный вход реверсивного счетчика

l0, изменяя его содержимое в сторону уменьшения частотной расстройки между сравниваемыми сигналами в ВРЧ 6.Выходное напряжение интегратора 30 сраннивается по уровню в компараторе 31 напряжений. При равенстве напряжений на его выходе появляется сигнал высокого уровня, который свидетельствует и6 окончании преобразования в блоке

ИПНК 24. На один из входов компаратора 31 поступает напряжение с выхода

ПЦА 25, которое, в свою очередь, зависит о т кода, поступающего от задатчика 17 кода частоты. При этом необходимо помнить, что в случае использования разных кодов для управления ДПКД 2 и ПВИ 13 необходимо вклю чение специального преобразователя кодов (например преобразователя двоично-десятичного кода в двоичный) между выходом кода задатчика 17 кода частоты и входом управления ПВИ 13. Сигнал с выхода компаратора 31 устанавливает второй триггер 26 в нуль (при этом ключ 28 размыкается), запрещая прохождение импульсов с генератора 27 импульсон через второй элемент И 29 на выход ПВИ 13; осуществляет сброс в нуль ГПН 23; устанавливает RSтриггер 18 в исходное состояние; осуществляет сброс в нуль интегратора 30, после чего уровень сигнала на выходе компаратора, т.е. на управляющем выходе ПВИ 13, снова становится низким, Число импульсов на выходе ПВИ 13 за время его работы определяется длительностью импульса на выходе вто" рого триггера 26, которая, в свою очередь, зависит от времени интегрирования в блоке 30. Напряжение на выходе интегратора 30 равно

ы1 о о поскольку при сбросе U> Пг„„

= co nst где ТЗΠ— постоянная времени интегратора 30; t — время интегрирования. При t t, U 0 U, следовательно, время интегрирования

1518881

Используя (4), получают число импульсов нл выходе ПВИ 13, p

У„Т п С (п (< TI< F<3 3 (5)

5 где Т вЂ” период импульсов с Вых о д а

Г J)t генератора импульсов 27 в блике ПВИ 13;

П1 = П,11 напряжение нл выходе комплрлт< рл 31, U, — опорное напряжение Б блоке

ПЦЛ 25;

N — код частоты, определя(ощи1! величину коэффициента деления ДПКД 2.

Поскольку То„, = NDFFJ>, )1 F)>f(> н )><с

=4N-<« частотная рлсст, )икл на выходе ПГ 1, которую необходи(<с скомпенсировать кольцом ФИ1Ч

Сб„т.. (1 Г, гп>! Т г>(пенсиронана с точнис bio ди посо(ы захвата по í "opot. управляющему входу

ПГ 1 за счет кода, xp(3)tstI!ILrucst Б реверсивном счетчике !О и презбрлзовлп<.> ного в IIKH 11 Б управляющее напряжение Б даль ейшut< пр<лп коцит обыч:i,i» работа устройст«», лнапогичная работ . устройств,)-прототипа.

Таким образом устройстни позьоля50 ет за один период р JItucTktoi частоты проводить измерение часто "ной «и ибкп в кольце ФЛПЧ ): ее компенсацию грубь;и каналом уп!)лн3)ения. Кр(>((е того, и:— пользонание б)3()кoi! сра) пения кодов

53 и установки кодл, а f )bæå коммутатор» позволяет игр;-ничить максима)!ьние значение периода рлзност«ой част (ы на ныходе выдели)еля разнистной

Следовательно, число импульси« нл выходе ПВИ 13, поступивших Б реверсl!В-25 ньп! счетчик 10, припорцио! ально рлз— ностной частоте, т, е. расстрийке, которую необходимо скимпенсировл)1 по первому входу ПГ 1. После ol«>(1 !;!ния преобразования в П1(1< 13 импульс и<<3<7 его первом выходе по<.ту»ае г ) л г> ." сброса триггера 18 и уста) анлпн» ." его н нуль. Снгн;.; с Выхода 118-)(,):} гера 18 разрешает « эi м случ L. р-.)би- у фазоног0 коыплратир.! 7 и, посту:

35 управляющий ()ход к .» ftfy Tлтора 1 3 . >ицключает Выход пер. 01<7 ??!1?? .; .!tl> у входу ПГ >, разрешая <ем самым; бь««3п) работу кольца МП(1) Б:(JII()«, ющего I себя блики 1 — 4 ° Тлк клк <30JII«f.(на начальной ч.зстотнии рлсстро!ки скимчд<}т к суп!е—

< т«енпиму сикрлще)ппв ьр неilii J, <л< не) ия )п!формации и част<>твой ошибке, Ф и р и у !I ;i и a < > б р е т е I и я

1, Устрийст«0 <1>,<зиной лвтипидL"Ið0ffêè частоты, содержащее соединенные послед<3«ательн(> IIL I7(-:;. т!>л t<;.:-((!.и»

fåíåð""T<)ð, деJ!«Toë(. !сто), опорнь(й генеp«ò<)ð. «:(ход

1 .OTOPOI" П()ДК Б() !(.".Н 1 Вт< Pи(Г<<< НХОД)У фазового детектора, выде3пг ль 1>л.зш>СT)(OJi ЧБCТОТЫ Ii фЛЗOI3.1 <»(!!.l 1 PБТ0Р, еppi е и «тир(е >)коды ки >;,b(с.

j!0<(((! " )< > f3(<(i 1<}tJ((7 < w !(I i>P (М

:>ходам((флзи <>»< дс г: к, . (. < Кй

Jt т

r вых: дами ф <-, -, .. р"- (,л, i <)кже со<"д! J!, .J; !»L i л.,«л >и >(> р ве сJ âf>(JI! ч: Гпп, "Г..об!

«".ï1 <((<» J: . —. !i (; "ирои !

t!! ПИХ Ч ° i . i,. .<\Ык ) <(;< > « ) <" »< IJOJ,><7" е« к пе му управ) пщс . )>Киг!у ! р )0òð,>;< ) > м >го ге!.е г.о -, >-ричем ! в ХОДЫ Ii;i<«» О И !J T(!1>С)ГО 7 L: ((ти! !

)зЧИ (. <><. ли !Бнь(с: . ет . Бепн<> с г, р«ым

П )! f <7) I! ) . ,.it Р (В< P(:I>>3И Г() < . < 1 )J JIIi < . < Л !: >) Il< !. БОI (<(<

<,(>к«и;-:. (;<с Гоп ),<7д),;. (:.<).< (к Б; <)р<)((,. пр > ..: . щеf(13:. >дl l(Lp(! стран)Заем<)ги

Г, (Е(П3<О))Л, 0 . Jl П Ч Л .<> Ш Е Е .. Я ! <ъМ Ч, (7 < Ц(° })ЬЮ «0) < < )<) !f ((( ь- !I< I J>Its) > Б :г ) )>;« )< Jlbl <7",е(76 "<1ЗОВл

- ель врем. »Бых интервал в, Баспредезте.:и импу.)ь(ин, пер«ьп <) Бт<)рий

<3jlpl . }!bi<3 ?? ???? ?? kot(7poi ?? (>ЕДИНЕН(> . Тстне!(по с пер«l 1 и 13Topt!)«пав

К()БЬ 1 И ВЫХ:)ДЛМИ БЫЦ<З! .l ГЕЛЯ Р 1.311 < Т>(ий (! с т(>т«() с игнлльнь Й ))xoJ7, 17л! (<17 "????????????????” ???? ??????(???????????? ?????????????????? 1(????????????<?? ???? (0 ???? ????>брлзинлтеля —..ременных и (и L )I3л.<(>п„а п<з173ьп(и второй Б(!киды р; спрепе,fl!T ля змпульсов подключены сиитн(- тст«oil!!(; к Вторым входам г)ерного и второго элементов ИЧИ. зада г.! k к кспл

« lc ГОты Выход кода !iuтo,>огo п<)дк)1}пч(Б

К ПЕр«0Му >,ËOJtó ПрЕ Эбг>аэ(>Б;.3 ЕЛ>),.рЕ(е),«ых интер)залов и уrlp :!îùå(tó ()к() () . пел(i T =.1» час f 0 Ti)(> 1 8 -триггер, << Т,3((<03«оч }»!» Бх >ц к<>т< ри! 0 г<одключен ((i>lIi 7!ьспиму Бык(ду э((

:,л<-т . < (», Бхид сб)7(-.: з 1 .. Григгера зт<, )иму !3<,<..иду пр .и рлз (вателя времен«ых >пl сер: (лон, при (еM выделитель .. 31(00 «>й ч,if TO ы (: лбже импульс1518881 риг2 ным выходом, который соединен с вторым входом преобразователя временных интервалов, фазовый компаратор снабжен управляющим входом, который подключен к выходу RS-триггера, а преобразователь временных интервалов включает в себя первый триггер, счетный вход которого является вторым входом преобразователя временных интервалов, l0 первый элемент И, первый вход которого соединен со счетным входом первого триггера, второй вход — с выходом счетного триггера, генератор пилообразного напряжения, первый вход

15 которого подключен к выходу счетного триггера, преобразователь цифра аналог, вход которого является первым входом преобразователя временных интервалов, интегрирующий преобразователь напряжение — код, содержащий второй триггер, второй элемент И, генератор импульсов и последовательно включенные ключ, интегратор и компаратор, причем выход компаратора соединен25 с входами сброса интегратора, генератора пилообразного напряжения, первого и второго триггеров и является вторым выходом преобразователя временных интервалов, установочный вход второго 30 триггера подключен к выходу первого элемента И, а выход — к первому входу второго элемента И и управляющему входу ключа, сигнальный вход ключа подключен к вь коду генератора пилообразного напряжения, а выход второго элемента И является первым выходом преобразователя временных интервалов, второй вход элемента И соединен с генератором импульсов, второй вход компаратора соединен с выходом преобразователя цифра — аналог.

2. Устройство по п. 1, о т л и ч а —. кще е с я тем, что, с целью повьииения быстродействия, в него введены блок сравнения кодов, вход которого подключен к выходу кода задатчика кода частоты, блок установки кода, первый и второй входы которого соединены соответственно с первым и вторым выходами блока сравнения кодов, элемент задержки, вход которого подключен к импульсному выходу задатчика кода частоты, коммутатор, второй вход коммутатора подключен к источнику постоянного напряжения, а управляю-. щий вход — к выходу RS-триггера, причем реверсивный счетчик снабжен информационными входами, которые подключены к выходам блока установки кода, и управляющим входом, которыи подключен к выходу элемента задержки, а выход первого фильтра нижних частот подключен к второму управляющему входу перестраиваемого генератора через коммутатор.

1518881

Составитель Л.Шурухин

Техред A.Êðàs÷óê

Корректор С.Черни

Редактор И.Касарда

Подписное

Заказ 6610/56

Тираж 884

ВНИИПИ Государственного комитета по изобретениям и открытиям при ГКНТ СССР

113035, Иосква, Ж-35, Раушская наб., д. 4/5

Производственно-издательский комбинат "Патент", r. Ужгород, ул. Гагарина, 101