Устройство для контроля отношения шум-сигнал

Иллюстрации

Показать всеРеферат

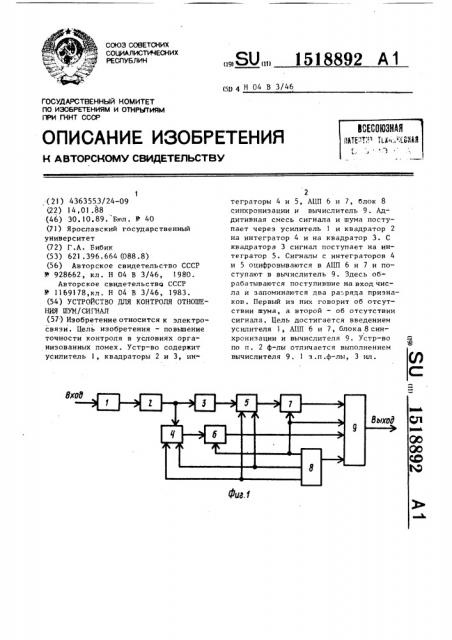

Изобретение относится к электросвязи. Цель изобретения - повышение точности контроля в условиях организованных помех. Устройство содержит усилитель 1, квадраторы 2 и 3, интеграторы 4 и 5, АЦП 6 и 7, блок 8 синхронизации и вычислитель 9. Аддитивная смесь сигнала и шума поступает через усилитель 1 и квадратор 2 на интегратор 4 и на квадратор 3. С квадратора 3 сигнал поступает на интегратор 5. Сигналы с интеграторов 4 и 5 оцифровываются в АЦР 6 и 7 и поступают в вычислитель 9. Здесь обрабатываются поступившие на вход числа и запоминаются два разряда признаков. Первый из них говорит об отсутствии шума, а второй - об отсутствии сигнала. Цель - достигается введением усилителя 1, АЦП 6 и 7, блока 8 синхронизации и вычислителя 9. Устройство по п. 2 ф-лы отличается выполнением вычислителя 9. 1 з.п. ф-лы, 3 ил.

СОЮЗ СОВЕТСКИХ

СОЦИАЛИСТИЧЕСНИХ

РЕСПУБЛИН

1518892 А 1 (19) (11) (pe 4 Н 04 В 3/46

ОПИСАНИЕ ИЗОБРЕТЕНИЯ

ЮхО

ГОСУДАРСТВЕННЫЙ КОМИТЕТ

ПО ИЗОБРЕТЕНИЯМ И ОТНРЫТИЯМ

ПРИ ГКНТ СССР

К АBTOPCHOMY СВИДЕТЕЛЬСТВУ

1 (21) 4363553/24-09 (22) 14,01 .88 (46) 30.10.89. Бюл. У 40 (71) Ярославский государственный университет (72) Г.А. Вибик (53) 621 .396.664 (088.8) (56) Авторское свидетельство СССР

У 928662, кл . Н 04 В 3/46, 1980.

Авторское свидетельство СССР

1(- 1169178,кл. Н 04 В 3/46, 1983. (54) УСТРОЙСТВО ДЛЯ КОНТРОЛЯ OTHOIIIEНИЯ ШУМ/СИГНАЛ (57) Изобретение относится к электросвязи. Цель изобретения — повышение точности контроля в условиях организованных помех. Устр-во содержит усилитель 1, квадраторы 2 и 3, ин2 теграторы 4 и 5, АЦП б и 7, блок 8 синхронизации и вычислитель 9. Аддитивная смесь сигнала и шума поступает через усилитель 1 и квадратор 2 на интегратор 4 и на квадратор 3. С квадратора 3 сигнал поступает на интегратор 5. Сигналы с интеграторов 4 и 5 оцифровываются в АЦП 6 и 7 и поступают в вычислитель 9. Здесь обрабатываются поступившие на вход числа и запоминаются два ра=.ряда признаков. Первый из них говорит об отсутствии шума, а второй — об отсутствии сигнала ° Цель достигается введением усилителя 1, АЦП 6 и 7, блока 8 синхронизации и вычислителя 9. Устр-во по п. 2 ф-лы отличается выполнением вычислителя 9. 1 з .п .ф-лы, 3 ил .

5 1518 се и усиливается до величины, достаточной для нормальной работы квадратора 2.

Сигнал на входе квадратора 2 можно записать в виде

5 где А, — огибающая, (» — частота, 10 (» — фаза полезного сигнала, шум.

Предполагается, что полезный сигнал — сигнал с угловой модуляцией (манипуляцией)» поэтому егибающая его

А, имеет постоянное значение. Шум нормальный, гауссов с нулевым математическим ожиданием и дисперсией G

Нормализации его способствует полосовой фильтр, имеющийся в усилителе 1. 20

После квадратора 2 сигнал пропорционален

2 2

А = А, cos (cat +tP) +

4- 4 » Ъ 30

А = А, cos ((Dt+C(»)+4A»cos(dt+g) P +

+6A соз ((at+a)+4A» соя (Qt+cP) (+(. (3) 35 (8) 40

50

6 и 7 этот уровень может бить единицей (или приближаться к н(.»») . В этом

А = А, сов (Z«««»«) «», (I>

+ 2 ° (A< cos((0t +g) +(, (2) После квадратора 3 сигнал пропорционален

При идентичности квадраторов 2 и 3 ,коэффициенты пропорциональности в окончательном выражении сокращаются.

Кроме того,при построении квадраторов 2 и 3 на выходе каждого из них можно использовать нормализующий усилитель с тем, чтобы коэффициент пропорциснальности выходного сигнала квадрату входного был равен единице. Поэтому в дальнейшем изложении этот коэффициент полагается равным единице.

После квадраторов 2. и 3 сигналы

2 1

А, A поступают на информационные входы соответственно интеграторов .4 и 5. Величина сигнала на выходе интегратора зависит от времени интегрирования, однако в данном случае оно одно и тоже для обоих интеграторов 4 и 5 (задается блоком 8). В окончательный алгоритм входит только отношение сигналов с выхода интеграторов 4 и 5, поэтому время интегрирования можно положить равным единице. В этом случае, в результате усреднения, реализуемого за счет на892 6 копления в интеграторах 4 и 5 за вре-. мя действия сигнала U< (фиг.За), на выходе интеграторов 4 и 5 формируются сигналы.

А А, + (.» (4) в

4 3 4 2 2 4

А = — А, + ЗАC»+ Зо .(5) Эти сигналы оцифровываются АЦП 6 и 7 за время действия сигнала U

3 (фиг.Зв) и в оцифрованном виде поступают соответственно «а первый и второй входы вычислителя 9. Вычислитель 9 обрабатывает поступающие на его первый и второй входы числа, соответствующие сигналам А2 А по алгоритму, который вытекает из решения системы уравнений (4) и (5), а

А, = — (3 (А ) — А ). (6) Подставляя значения А, из (6), полученное из решения уравнений (4) и (5), в соотношение (4), получа»ат

26 (7)

Соотношение (7 } определяет алгоритм вь«числения отношения мощности шума (5 2 ) к мощности сигнала (— А ).

1 2

Особенностью д««нного;»лгорит»»а является то > что результат всегда должен быть положительным. Анализ соотношений (4) и (5) дает, что

1,5 (А ) А =-3(A ) Из этого следует, что знаменатель подкоренного выражения (7) всегда положитепен. Однако, поскольку обрабатываются случайный» процесс реальным вычислителем (с конечной точностью), возможнь» следующие ситуации: 2 — 4 2. 7 если А» = О, то А 3(/, ) (9) если 6 "- О, то А — 9 ), (10) Эти ситуации учтены в алгоритме работы вьчислителя 9, в котором учтено и то, что усилитель 1 нормализирует уровень входного сигнала на каком-то определенном уровне, для АЦП

1518892 случае числитель подкоренного выражения соотношения (7), является величиной нормализованной, что упрощает построение блока 13 деления. Работа вычислителя сводится к последовательности выполнения следующих операций

-г г

Ь,=АхА=(А)

b Зхb -3(A)

b = Ь2 — А 3 (A2) -A знак запоминается в триггере 24, I

1, -2

b =-Ь,=)5(A); )0

Ь4

Ь Зф )2ь,= .)ь,=

b = b — 1 т ь

25 знак запоминается в триггере 23.

Тактовые импульсы с четвертого выхода блока 8 синхронизации посту- плют на второй вход блока 10 управления (четвертый вход вычислителя 9) который или непосредственно, или после преобразования их в последовательность управляющих тактовых

30 импульсов передает их на третьи вхо-, ды блоков 1), 13 и 14. Сигнал, по35 .ступающий с третьerq выхода блока 8 (U> фиг. Зв) на первый вхрд блока

10 (третий вход вычислителя 9) является пусковь1м для блока 10. По

Окончании этОГО сиГнала р блОк .1 0 40 формирует кодовый сигнал Vy (фиг.3г) по коду а ко горого мультиплексоры

15 и ) 6 пропускают оцифрованное значение л на первый и второй входы блока 1) у ножения, реэультат которого 45

b,, = (7 ) по сигналу U< (фиг.Çe) запоминается в регистре 20, а по коду

b это число через мультиплексор 16 поступает на второй вход блока 11, на первый Вход которОГО, по этОму же кО- 0 ду Ь мультиплексор 15 пропускает число "3" злписанное в блоке 22 регистров. В этом блоке записано два числа, это число "3", которое подается на второй вход мультиплексора )5, и число 1, которое в инверсном коде и 51 55 подлется нл первый вход мультиплексора ) 7. Результат второго умножения (Ü2 3 х (A ) )запоминается в регистре 20 по сигналу 0 (фиг. Зе) и со сдвигом вправо на oöèEJ разряд передается на первый вход блока 13, беэ сдвига на — первый вход мультиплексора 18, на третий. вход мультиплексора — 4

17 поступает оцифрованное значение А в инверсном коде с второго входа вычис лителя 9 (выхода АЦП 7) . По кодовому сигналу t I (фиг.ЗЖ) при коде а эти числа через мультиплексоры 18 и 17 поступают соответственно на входы блока 12 сложения. Результат сложения

Ь по сигналу )1 (фиг.Зэ) запоминается в триггере 24 и блоке 13. В триггере 24 запоминается знак результата, а в блоке 1 3 — значащие разряды, гоступающие на его первый вход. Одновременно в блоке 1 3 запоминается число Ь4, поступающего нл его 11ервый вход с регистра 20 через сдвиглтель

25. После запоминания этих чисел блок

13 производит деление: этих чисел. Пля блока 13 запускающим является сигнал

Па (фиг. Зз). Результат деления b передается на блок )4 извлечения квадратного корня, для которого запускающим сигналом является 0, (фиг.,3v). ! . Результат извлечения корня Ь содержит целую и дробную части. Разряды дробной части подаются на первый вход второго мультпплексорл 19, а целой части. — на второй вход пятого мультиплексора ) 8. На первый вход третье о мультиплексора )7 с первого выхода блока 22 регистров подается 1" в инверсном коде. По сигналу U> (фиг.Зж), по коду Ь, эти числа подаются соответственно нл входы olIoка 12 сложения, Результат сложения поступает на первый триггер 23 (знаковый разряд, который злпоминается по сигналу П„ь, фиг, ЗК) и четвертый вход второго мультиплексора !9 (значащие разряды). На первом и втором входах мультиплексора )9 находится число, соответствующее отношению мощности шума 0 к мощности

2 сигнала (— 1 ) вычисленное соглас 2 1 но формуле (71 без учета возможных граничных ситуаций, определенных соотношениями (9) и (10). При отсутствии сигнала или шума это может привести к неверным результатам, поскольку на блок 13 деления и на мультиплексор )9 выдаются числа без знака, поэтому при малых отрицательных числах результат вычислений будет 518892!

1 формулаиэобретения

1, Устройство для контроля отноше40

f ния myM/ñèãíàë, содержащее последовательно соединенные первый квадратор и первый интегратор, последовательно соединенные второй квадратор

45 и второй интегратор, о т л и ч а ю— щ е е с я тем, что, с целью повышения точности контроля в условиях организованных помех, введены вычислитель, усилитель, выход которого подключен к входу первого квадратора, выход которого подключен к входу второго квадратора, первый аналого-цифровой преобразователь, включенный между выходом первого интегратора и первым входом вычислителя, второй аналого-цифровой преобразователь,включенный между выходом второго интегратора и вторым входом нычислителя, блок противоположен истинному состоянию канала, иэ-эа представления отрицательных чисел в дополнительном коде.

Для выявления этих ситуаций используются триггеры 23 и 24. При отсутст5 вии сигнала выполняется соотношение (9), в этом случае (при любом значении чисел на входах мультиплексора

l9) триггер 24 заставляет мультиплексор 19 выдать во всех разрядах результата единицы, которые запоминаются в регистре 21. Кроме разрядов результата, в регистре 21 запоминаются еще два разряда признаков.

Первый иэ них говорит об отсутствии шума (U = О), а второй об отсутстг вии сигнала ф = О) ° При отсутстг

1 вии сигнала триггер 24 заставляет мультиплексор 19 установить первый разряд признаков в нулевое, а второй — в единичное состояния. При отсутствии шума (триггер 23 — в единичном состоянии, триггер 24 — в нулевом) мультиплексор 19 выдает 25 все нули в разрядах результата. Разряды признаков устанавливаются: первый в единичное, а второй - в нулевое состояние. При отсутствии особенностей (оба триггера 23 и 24 — 3Q в нулевом состоянии) мультиплексор

13 пропускает результаты расчета по формуле (7) беэ изменения, т.е. содержание разрядов на соответствуюших входах мультиплексора 19 передаются на его выход без изменения, а н разрядах признаков записываются нули. синхронизации, первый и второй выходы которого соединены соответственно с первым и вторым управляющими входами первого и второго интеграторов, третий выход подключен к управляющим входам первого и второго аналого-цифровых преобразователей и к третьему входу вычислителя, а четнертый выход блока синхронизации подключен к четвертому входу вычислителя.

2. Устройство по п.l, о т л и ч аю щ е е с я тем, что вычислитель содержит последовательно соединенные блох управления, первый мультиплексор, блок умножения, первый регистр, сдвигатель, блок деления, блок извлечения квадратного корня, второй .мультиплексор и второй регистр, другой вход которого соединен с вторым выходом блока управления, последовательно соединенные блок регистров, третий мультиплексор, блок сложения и первый триггер, выход которого подключен к второму входу второго муль типлексора, четвертый мультиплексор, выход которого подключен к второму входу блока умножения, пятый мультиплексор, включенный между выходом первого регистра и другим входом блока сложения, второй триггер, включенный между третьими выходами блока управления и второго мультиплексора, при этом четвертый выход блока управления подключен к второму входу первого триггера, первый вход которого соединен с вторыМ входом второго триггера, третий выход блока управления подключен к второму входу блока деления, третий вход которого соединен с нтоРым выходом блока сложения и четвертым входом второго мультиплексора, пятый выход блока упранления подключен к другому входу первого регистра, выход которого подключен к первому входу четвертого мультиплексора, второй вход которого соединен с первым выходом блока управления, шестой выход которого подключен к вторым входам третьего мультиплексора, и пятого мультиплексора, третий вход которого соединен с вторым выходом блока извлечения квадратного корня, второй выход блока регистров подключен к второму входу первого мультиплексора, седьмой выход блока управления подключен к третьему входу блока умножения, четвертый вход которого соединен с носьмым выходом

1518892

Фиг.2 блока управления, к четвертому входу блока деления, к второму входу блока извлечения квадратного корня, третий вход которого соединен с девятым выходом блока управления, первый и второй вход которого являются соответственно третьим и четвертым входами вычислителя, первым входом которого является третий вход первоI

ro мультиплексора, соединенный с тре" тьим входом четвертого мультиплексора, а третий вход третьего мультиплексора является вторым входом вычислителя, выходом которого является выход второго регистра.

1518892

Составитель А. Сеселкин

Редактор Л. Пчолинская Техред Л.Сердокова Корректор О.Кравцова

Заказ 6612/57 Тирах 626 Подписное

ВНИИПИ Государственного комитета по изобретениям и открытиям при ГКНТ СССР

113035, Москва, Ж-35, Раушская наб., д. 4/5

ll н

Производственно-издательский комбинат Патент, г. Ужгород, у». Гагарина, 101