Система передачи цифровой информации

Иллюстрации

Показать всеРеферат

Изобретение относится к радиотехнике. Цель изобретения - повышение скорости передачи сигналов. Система передачи цифровой информации содержит на передающей стороне кодер 1, буферный запоминающий блок (БЗБ) 2, формирователь 3 управляющих сигналов, блок анализа (БА) 4 сигналов, модулятор 5 и выходной передающий блок 6, а на приемной стороне избирательный приемный блок 7, формирователь 8 управляющих сигналов, блок 9 обработки сигналов, демодулятор 10, БЗБ 11 и декодер 12. Из дискретных сообщений кодер 1 формирует символы кодовых комбинаций, которые поступают в БЗБ 2 и далее в БА 4. Здесь задаются временные промежутки между символами кода, и далее символы поступают на модулятор 5, который формирует соответствующие им бинарные сигналы. После усиления эти сигналы поступают на приемную сторону, где в результате преобразований производится исправление возможных ошибок в коде и выдача дискретных сообщений на выход. Цель достигается введением БЗБ 2 и 11, формирователей 3 и 8, БА 4 и блока 9 обработки. Система по п.п. 2 и 3 ф-лы отличаются выполнением БА 4 и блока 9 обработки, даны их ил. 2 з.п.ф-лы, 3 ил.

СОЮЗ СОВЕТСНИХ

СОЦИАЛИСТИЧЕСНИХ

РЕСПУБЛИК (504 Н 04 1, 2/ 18

ОПИСАНИЕ ИЗОБРЕТЕНИЯ

К АBTOPCKOMY СВИДЕТЕЛЬСТВУ ис 1

ГОСУДАРСТВЕННЫЙ КОМИТЕТ

ПО ИЗОБРЕТЕНИЯМ И ОТКРЫТИЯМ

ПРИ ГКНТ СССР (21) 4246123/24-09 (22) 19.05.87 (46) 30.10.89. Бюл. У 40 (71) Харьковский политехнический институт им.В.И. Ленина (72) В,П. Гетман, М.А. Иванов и И.И. Сватовский (53) 621.376.52(088.8) (56) Пении П.И. и др. Радиотехнические системы передачи информации. М.:

Радио и связь, 1984, с. 192-193. (54) СИСТЕМА ПЕРЕДАЧИ ЦИФРОВОЙ ИНФОРМАЦИИ (57) Изобретение относится к радиотехнике. Цель изобретения - повыщение скорости передачи дискретных сигналов, Система передачи цифровой информации содержит на передающей стороне кодер 1, буферный запоминающий блок (БЗБ) 2, формирователь 3 управляющих сигналов, блок 4 анализа (БА) сигналов, модулятор 5 и выходной передаю„„Я0„1518911 A 1

2 щий блок 6, а на приемной стороне избирательный приемный блок 7, формирователь 8 управляющих сигналов, блок 9 обработки сигналов, демодулятор 10, БЗБ 11 и декодер 12. Из дискретных сообщений кодер 1 формирует символы кодовых комбинаций, которые поступают в БЗБ 2 и далее в БА 4.

Здесь задаются временные промежутки между символами кода, и далее символы поступают на модулятор 5, который формирует соответствующие им бинарные сигналы. После усиления эти сигналы поступают на гриемную сторону, где в результате преобразований производится исправление возможных ошибок в коде и выдача дискретных сообщений на выход. Цель достигается введением БЗБ 2 и 11, формирователей

3 и 8, БА 4 и блока 9 обработки. Система по п.п. 2 и 3 ф-лы отличается выполнением БА 4 и блока 9 обработки, даны их ил. 2 з.п. ф-лы, 3 ил.

18911

Из»бретение огпосится к ради«техн,«<е и может бьггь использовано в радиосистемах передачи дискретной инф< рмации.

Цель изобретения — понышени» скорости передачи дискретных сигналов.

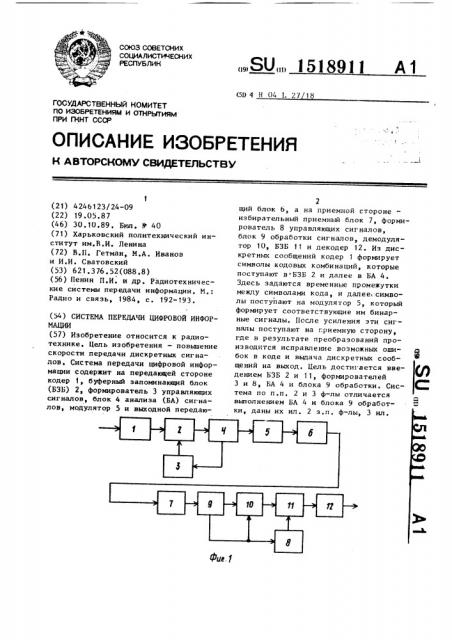

На фиг. 1 изображена структурная элек грическая схема предложенной сис— теил; на фиг. 2 — структурная элект- 10 рическая схема блока анализа сигналон, структурная электрическая схема

GyA "рного запоминающего блока и стр уктурная электрическая схема формир >вателя управляющих сигналов; на фпг . 3 — структурная электрическая ( схема блока обработки сигналов.

Система передачи цифровой информации содержит на передающей стороне кодер I, буферный запоминающий блок

2, формирователь 3 управляющих сигналов, блок 4 анализа сигналов, модулятор 5 и выходной передающий блок

6, а на приемной стороне — избирательный приемный блок 7, формирова- 25 тель 8 управляющих сигналон, блок 9 обработки сигналон, демодулятор 10, буферный запоминающий блок 11 и декодер 12.

Буферный запоминающий блок содержит первый и второй регистры 13 и 14, узел 15 вентилей и элемент ИЛИ 16.

Формирователь управляющих сигна- н лов содержит перный дешифратор 17, генератор 18 тактовых импульсов, эле- 35 мент ИЛИ 19, первый и второй коммутагоры 20 и 21, первый и второй триггеры 22 и 23, третий коммутатор 24, первый и второй счетчики 25 и 26, первый и второй блоки 27 и 28 ненти- 40 лей, первый и второй элементы ИЛИ-НЕ

29 и 30 и второй дешифратор 31.

Блок анализа сигналов содержит элемент ИЛИ 32, первый и второй триггеры 33 и 34, генератор 35 тактовых 45 импульсов, блок 36 равнозначности, ?оммутатор 37, первый и второй счетп1ки 38 и 39 и первый и второй дешифраторы 40 и 41.

Блок обработки сигналон содержит дешифратор 42, вентиль 43, детектор

44 огибающей, генератор 45 тактовых импульсов, пороговый блок 46 и счетчик 47.

Система работает следующим обра5 зом.

На вход кодера 1 поступают дискретные сообщения в виде последова— тельности двоичных символов (нулей и "единиц"), н которые вносится цо специальному алгоритму некоторая избыточность (помехоустойчивое кодирование). Символы кодовых комбинаций с выхода кодера 1 поступают на вход буферного запоминающего блока 2,которое выполняет функции промежуточного хранения символов кода и вывода последних н соответствии с результатами их анализа н блоке 4 анализа сиг налон.

Для выполнения данной функции символы кодов записываются н первый регистр 13 по сигналам записи, поступающим с выхода генератора 18 тактовых импульсов с такой же тактовой частотой 1, что и символы кода т (для простоты считаем, что тактовая частота поступления символов кода уже согласована с услониями дальнейшей передачи по каналу, т.е. f» = 1/

/(г„„ + г.„ ). С началом заполнения первого регистра 13, емкость которого равна N символам, тактовые импульсы поступают через первый коммутатор 20 на вход прямого счета первого счетчика 25, а также через третий коммутатор 24 — на вход обратного счета второго счетчика 26 (счетчики

25 и 26 представляют собой 1-разрядные счетчики с входами прямого и об— ратного счета, в исходном положении первый счетчик 25 обнулен, а в 1 разрядов второго счетчика 26 записаны единицы, при этом 1 = 1о8 (N+1) Поступающие на второй счетчик 26 тактовые импульсы приводят к установке его в нулевое состояние в тот момент, когда полностью заполняется первый регистр 13. Появление нулевых сигналов на всех выходах нторого счетчика

26 вызывает появление единичного сигнал» на выходе элемента ИЛИ-НЕ 30.

Данный единичный сигнал поступает на

S-вход второго триггера 23 и вызывает его переключение из исходного нулевого н единичное состояние. Этот же единичный сигнал поступает через элемент ИЛИ 19 на входы управления первого регистра 13 и нторого регистра 14 и вызывает параллельную перезапись символов кода с первого ре" гистра 13 но второй регистр 14, а также устанавливает первый триггер

22 из исходного нулевого в единичное состояние. Единичный сигнал с выхода элемента ИЛИ-НЕ 30 также разрешает прохождение сигналов с выходов пер1518911 во! о счет п>кы 25 чере-. в."Opol! б..>ок

2/ вентилей на входы первого депплфратора 17, ня N-м выходе которого появляется единичный сигнал, разрешаю!и>лй последовательный вы33од и>!формации из второго регистра 14 через N-й вентиль узла 15 вентилей и элемент

ИЛИ 16 «а выход буферного запоминающего блока. Одновременно единичный сигнал, пос гуntl 3 с выходы тр:Зггеря

23 на управляюш,.>B входы коммутаторов 20, 21, вызыв. "т перекоммутацию первого коммутатора 20 и второго коммутатора 21.

При перезаписи информации из регистра 13 в р гистр 14 вкл>очается генератор тяктоны . импул>,cc!3, Т:ll. голля частота генераторы тактовых;3мпул,—

> сов выбирается равной i = 3иЕ . 11ри этом коэффициент про>3орц33оцы>>3-цос" и

331 77 1 и 3и c M п1 — мцожеcTI3(> цены л

Э ч!сел и m/f, = !. + ь, > и,/f — п>3 (m., } лок 36 равцозна >ности управляет четвер ть м коммутатор оь 3 7: при ры зличных символах ца вь>ходах триггера

33 и триггера 34 выход генератора тактовых и, Зульсов подключается к входу счет..ика 38, а при оди! коньо; символах — к входу счетчика 3 !. П3ц! этом, когда счетчик 38 зыр! >- цст-»3рует m импульсов, на соответстцу! щ! м выходе дешифратора 40 появл>я ется ед33 ничный сигнал, а единичный OHBIIB.! цы (выходе депп>фраторп л1 появляется тогца когда счетчик 39 зарегистрирует .t

m импульсов. Псяв:!яющиеся ня выхо3/ дах дешифраторов 40 или 41 едиц33чные сигналы устанавливают в нулевое состояние соответствующие счетчики и, поступая через элемент ИЛИ 32 на управляющий вход второго регистра 14, вызывают последовательный вывод информации через соответст.>ук>щий вентиль первого узла 15 вентилей и элемент ИЛИ 16 на вход блока 4 анализа.

Таким образом, на основании анализа

/ равнозначности символов кода блок 4 анализа задает временные г>ромежутки между символами кода, выдаваемогc C выхода буферного запоминаю>це! с блока

2, либо посредством счетчика 38 (определяют Bpеменные промежутки между

> выводом различных символов m/f, t + с ) либо посредством четвер— пп пр того счетчика 39 (определяет временные промежутки между выводом одина>

CHMBOJ1OB m / f 3- = t и ) I

Bb1BOt! CIIt tI3oJtOt> Il 3 р Bf !!с т1>я 14 и одновременная BBI»tct в ре! истр 13 будут продолжаться до того момента, пока количество импульсов, управляющих считыванием информации из регистра

14, не стянет равным количеству импульсов, записанных в счетчик 25 при первой записи в ttepBbltt регистр 13.

Указанные импульсы считывания, поступ!вв через коммутатор 21 ца вход обратного счета с Зетчика 25, вызовут появление цулевь!х сигналов ня всех его выходах, что обозначает конец

15 вывода из регистра 14. В этот момент в счетчике 26 будет записано число импульсов, поступив!>их на его вход прямого счета с выходя гettr.paторы

18 тактов!>х IIMIIульсов через ком 3ута20 тор 20 и соответству>о>>!их количеству ры зрялов регистра 13, запол>3инпплхся .>я время вывода ицформа 3и из регистра 14. Нулевьte сигналы на выходах сче1чцка 25 вызывают появление еди25 ц3!чного сигнала ця выходе элемента

ШН1-HK ?9, который поступает ны Rвход второгo триггера 23, а через злеMPktT И>Е 19 — ны управляющие входы регистра 13 ц регистра 14, а так3О ке цы управляющий вход блока ?8 вентилей. Ilo данному сигналу происходит: параллельная зап33сь символов кода первого 1 во второй регистр 14; прохождение сигналов с выходов счетчика

26 через третий блок 28 3>ецтиле!! на

35 входы дешифратора 31>, troropbrt опрел-:ляет номер пенриля в у 3ле 15 вентилей и разрешае г последовательный вывод через данный вентиль символов ,ц> кода из регистр 1 14; переклн> ение тригr pa 23 в нулевое состояние, что в свою очередь вызывает установление коммутации первого коммутатора 20 и

1 второго коммутатора 21, повторяющеи исходную.

>1ал ьней!>3ая работа происходит аналогично описанной, за исклн>чением

roBo, что на вход обратного счета счетчика 26 будут поступыть импульсы

5р не с выхода генератора 18 тактовых импульсов через коммутатор 4, а с

>/ выхода блока 4 анализы через коммутатор 21 и коммутатор 24 (тяк как управляющий коммутатором 24 сигнал с

55 выхода триггера 22 fóttk т ры вцым единице) . Сигналом окс ча>>ия пере дачи информации служит налцчц" единичных сигналов на выхо Iàõ перв! о»>! нгорого элементов ШИ1-ИЕ 29 -! 3(3 (I3 э roM

1518911 случае и первый и второй регистр

13 и 14 пусты) .

Символы кода с выхода блока 4 ана ли »» поступают на модулятор 5, который Формирует соответствующие им би5 парные сигналы. Данные сигналы усиливаются выходным передан1щим блоком 6 и через среду распространения сигна;»ов поступают на избирательный приемный блок 7, где фильтруются, усиливаются и поступают на вход блока 9 обработки сигналов.

С г»нхода блока 9 обработки сигналов манипулированные сигналы поступают на вход детектора 44 огибающей и вход вентиля 43. С выхода детектора

44 огибающей напряжение, соответствующее уровню А огибающей сигнала, поступает на вход порогового блока

46 (ири приеме сигналов уровень их огибающей поддерживается примерно постоянным за счет применения АРУ до блока 9 обработки сигналов) . При из- 25 менении фазы принимаемого сигнала происходит уменьшение амплитуды колебания с предыдущей фазой и нарастание амплитуды колебания с новой фазой (при изменениях амплитуды модулированных сигналов, вызванных их прохождением через избирательные цепи, АРУ не успевает поддерживать постоя»»г»ьп» уровень огибающей в силу своей инерционности) . Для фиксирования момента отклонения уровня огибающей от номинального уровня А - предназначен пороговый блок 46, который представляет собой двухпороговый компаратор. На выходе порогового блока

46 появляется сигнал логической единицы в случае, когда входное напряжение (уровень огибающей) находится в заданном интервале от номинального:

A, -hA А A +АА и сигнал логио ° 45 ческого нуля, когда входное напряжен»»е выходит за этот интервал: А À

-аА или А А + А. При этом заданный интервал изменения уровня огибающей сигнала А выбирается большим

50 изменения амплитуды огибающей за счет быстрых замираний сигнала в канале передачи, т.е. появление едийичного сигнала на выходе порогового блока 46 означает окончание переxup,Hûõ процессов, возникающих при прохождении сигнала через блок 7, а появление нулевог о сигнала — наличие переходных процессов °

Допустим, на выходе порогового блока 46»»оявляется единичный сигнал.

Данный сиг нал поступает на у»»равляющие входы счетчика 4 7 и вентиля 43, открывая первый для подсчеra импульсов, поступающих с выхода генератора . I

45 тактовых импульсов с частотой 1 (счетчик 47 и дешифратор 42 аналогичны счетчику 39 и дешифратору 41), и второй для пропускания сигнала «а обработку в демодулятор 10. Счетчик

47 регистрирует m импульсов с выхода генератора 45 тактовьгх импульсов (m /f = г„ ) и устанавливается в нулевое состояние единичным сигналом с соответствующего m -ro выхода пятого ( дешифратора 42 в демодулятор 10 и формирователь 8. Данный единичный сигнал вызывает считывание принятого символа с выхода демодулятора 10 (а именно — с выхода интегратора со сбросом) и запись его в буферный запоминающий блок 11.

Если следующий принятый сигнал является повторением предыдущего, то работа схемы повторяется. Прием другого сигнала приводит к появлению на выходе порогового блока 46 нулевого сигнала, не разрешающего прохождение сигнала через вентиль 43 и выдачу сигнала в демодулятор 10 и формирователь 8. После окончания переходных процессов работа повторяется. Таким образом, блок 9 обработки сигналов производит определение наличия переходных процессов и управляет работой (точнее — выводом с его выхода принятого решения)демодулятора 10 и записью символов в буферный запоминающий блок 11.

Символы принятого кода записываются с выхода демодулятора 10 в буферный запоминающий блок 11 в соответствии с управляющими сигналами из блока 9 и считываются иэ буферного запоминающего блока 11 с необходимой частотой по сигналам генератора 45 тактовых импульсов, находящегося на приемной стороне. Символы с выхода буферного запоминающего блока 11 поступают на вход декодера 12, который производит исправление возможных ошибок в коде в соответствии с его исправляющей способностью и выдает дискретные сообщения на выход.

Ф о р м у л а и з о б р е т е н и я

1. Система передачи цифровой инФормации, содержащая на передающей

1з18911 стороне кодер, модулятор, выход которо и соединен с входом выходног о передающего блока, а на приемной стороне — избирательный приемный блок, демодулятор и декодер, о т л и ч аю щ а я с я тем, что, с целью повышения скорости передачи дискретных сигналов, введены на передающей стороне буферный запоминающий блок, блок ана10 лиза сигналов и формирователь управляющих сигналов, выход которого соединен с управляющим входом буферного запоминающего блока, выход которого подключен к входу блока анализа сигналов, первый выход которого соединен с входом модулятора, при этом выход кодера подключен к сигнальному входу буферного запоминающего блока, второй выход блока анализа сигналов подключен к входу формирователя управляющих сигналов, а на приемной стороне — буферный запоминающий блок, формирователь управлякицих сигналов и блок обработки сигналов, первый выход 25 которого соединен с первым входом демодулятора, выход которого соединен с сигнальным входом буферного запоминающего блока, выход которого подключен к входу декодера, при этом выход избирательного приемного блока соединен с входом блока обработки сигналов, второй выход которого подключен к второму входу демодулятора и к входу формирователя управляющих сигналов, выход которого соединен с управляющим входом буферного запоминающего блока.

2. Система по п. 1, о т л и ч а ю щ а я с я тем, что блок анализа сигналов содержит два триггера, блок равнозначности, коммутатор, два дешифратора, элемент ИЛИ и генератор тактовых импульсов, выход которого соединен с сигнальным входом комму1 45 татора, первый и второй выходы которого подключены к первым входам соответственно первого и второго снетчиков, выходы которых соединены с входами соответственно первого и второгс дешпфраторов, выходы которых соединены соответственно с первьи и вторым входами элемента ИЛИ, выход которого соединен с синхронизирующими входами первого и второго триггеров, выходы которых соединены соогветственно с первым и вторым входами блока равнозначности, выход которого подключен к управляющему входу коммутатора, при этом выходы первого и второго дешифраторов подключены к вторым входам соответственно первого и второго счетчиков, а D-вход второго триггера соединен с выходом первого триггера, D-вход которого является входом блока анализа сигналов, первым и вторым выходами которого являются соответственно выход второго триггера и выход элемента ИЛИ.

Система по п. 1, о т л и ч аю щ а я с я тем, что блок обработки сигналов содержит вентиль, детектор огибающей, пороговый блок, счетчик, дешифратор и генератор тактовых импульсов, выход которого соединен с первым входом счетчика, выходы которого подключены к соответствующим входам дешифратора, выход которого соединен с вторым входом счетчика, третий вход которого подключен к второму входу вентиля и выходу порогового блока, вход которого подключен к выходу детектора огибающей, вход которого соединен с первым входом вентиля и является входом блока обработки сигналов, первым и вторым выходами которого являются соответственно выход вентиля и выход дешифратора.

Составитель Q. Геллер

Техред Л.Олийнык Корректор Л.Патай

Редактор И. Бандура

Заказ 6613/58 ТиРаж 626 Подписное

ВНИИПИ Государственного комитета по изобретениям и открытиям при ГКНТ СССР

113035, Москва, Ж-35, Раушская наб., д. 4/5

Производственно-издательский комбинат "Патент", r. Ужгород, ул. Гагарина, 101