Многофункциональное устройство

Иллюстрации

Показать всеРеферат

Изобретение относится к области автоматики и вычислительной техники и может быть использовано при построении специализированных и универсальных ЭВМ. Цель изобретения - упрощение устройства за счет сокращения количества внешних связей. Многофункциональное устройство содержит четыре D - триггера 1-4, два мультиплексора 5 и 6, два коммутатора 7 и 8 и элемент 9 запрета. Устройство позволяет в зависимости от кода управления операциями выполнять арифметико-логические операции и операции сдвигов. 1 ил. 1 табл.

СОЮЗ СОВЕТСНИХ

СОЦИАЛИСТИЧЕСНИХ

РЕСПУБЛИН

А1

ОПИСАНИЕ ИЗОБРЕТЕНИЯ

К А ВТОРСНОМ,Ф СВИДЕТЕЛЬСТВУ

ГОСУДАРСТВЕННЫЙ НОМИТЕТ

ПО ИЗОБРЕТЕНИЯМ И ОТНЯТИЯМ

ПРИ fHHT СССР

1 (21) 4854842/24-24 (22) 04.01.88 (46) 07.11„89. Бкл. И 41 (71} Пермский политехнический институт (72} Л.Ф. Викентьев, А.А. Клюкин, О.Л. Лепихина и В.А. Гофман (53) 681.3(088.8) (56) Авторское свидетельство СССР

Ф 894714, кл. G 06 F 15/00, 1979.

Авторское свидетельство СССР

Р 1067497, кл. G 06 Г 7/ОО, G 06 F 15/00, 1981. (54) МНОГОФУНКЦИОНАЛЬНОЕ УСТРОЙСТВО (57) Изобретение относится к области

„.Я0„„1520503 сц) 4 С 06 F 7/00, 15/00

2 автоматики и вычислительной техники и может быть использовано при построении специализированных и универсальных ЭВМ. Цель изобретения— упроцение устройства за счет сокращения количества внешних связей.

Многофункциональное устройство содержит четыре D-триггера 1-4, два мультиплексора 5 и 6, два коммутатора 7 и 8 и элемент 9 запрета.

Устройство позволяет в зависимости от кода управления операциями выполнять арифметико-логические операции и операции сдвигов. 1 ил, 1 табл.

1520503

Изобретение относится к автоматике и вычислительной технике и может быть использовано при построении специализированных и универсальных ЭВИ.

Цель изобретения - упрощение устройства за счет сокращения количества внешних связей.

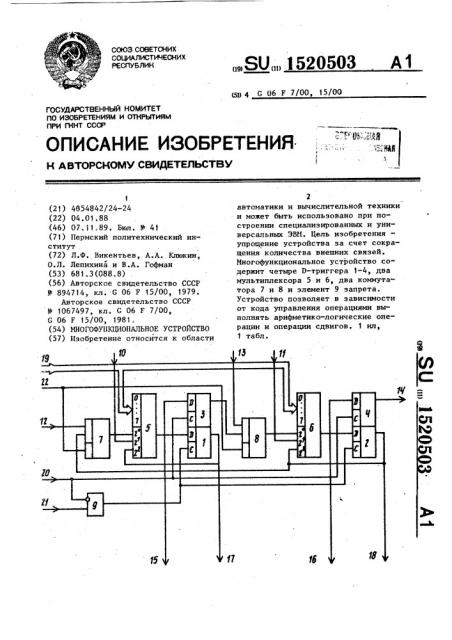

На чертеже представлена функциональная схема многофункционального устройства.

Иногофункциональнсе устройство содержит четыре D-триггера. 1-4, два мультиплексора 5 и 6, два коммутатора 7 и 8, элемент 9 запрета, вход 10 данных нулевого разряда, вход 11 данных первого разряда, первый вход 12 переноса, второй вход, I3..переноса, выход 14 переноса, асинхронный выход 15 нулевого разря-! ,да, асинхронный выход I6 первого. разряда, выход 17 нулевого разряда, выход 18 первого разряда, группу ,настроечных входов 19, первый тактовый вход 20, второй тактовый вход

21, вход 22 управления. арифметическими операциями и операциями сдвигов.

Многофункциональное устройство работает следующим образом.

Все арифметико-логические операции, выполняемые устройством, могут быть разбиты на две группы., В первой из них результат формируется как функция четырех аргуиентов: входных данных разрядов, значений. разрядов, переносов слева и справа.

Во второй группе команд результат формируется без учета переносов.

В многофункциональном устройстве для вычисления переносов и результатов операций используются одни н те же мультиплексоры 5 и 6, нри этом арифметико-логические операции первой группы реапизуются за два такта машинного времени, в первом из которых вычисляется значение переносов из нулевого и первого разрядов, запоминаемое в 9триггерах 3 и 4 соответственно, а во втором - значение операции в этом разряде с учетом переноса.

Команды второй группы выполняются обычным образом эа один такт машинного времени.

" Двоичный 8-разрядный код, подаваемый на группу настроечных входов

19, и значение сигнала на входе управления арифметическими операциями и операциями сдвигов определяют вид операции, реализуемой в данном такте машинного времени. Если значение сигнала на первом тактовом входе 20 устройства принимает значение "Лог. "1", то в устройстве осуществляется вычисление значения переноса каждого из разрядов (в зависимости от значения информации на группе настроечных входов 19) от значения сигналов на входах 10 и 11 данных нулевого и первого разрядов, а также от сигналов, сформированных на D-триггерах 1 и .2, и от выходных сигналов, сформированных на коммутаторах 7 и 8. На выходах коммутаторов 7 и 8 сигналы формируются в соответствии со значением сигнала на входе 22 управления арифметическими операциями и операциями сдвигов, поступающего

На управляющие входы этих коммутаторов, на первые и вторые информационные входы коммутаторов 7 и 8 подаются значения сигналов переноса слева и справа.

В этом такте в D-триггеры 3 и 4 происходит запись вычисленных значений переносов. При этом через элемент 9 запрета блокируется сигнал синхронизации на тактовых входах D-триггеров 1 и 2, в реэуль35 тате чего в данном такте машинного времени эти триггеры сохраняют свое

1 предыдущее значение.

При переходе к следующему такту машинного времени (такту вычисления результата операции) сигнал на первом тактовом входе 20 устройства должен принять значение "Лог. 0", что обеспечит сохранение записанных в

D-триггеры 3 и ч значений переносов из нулевого и первого разрядов соответственно и пропускание синхрониэирующего сигнала через элемент 9 запрета.на тактовые входы D-триггеров . и 2 (нулевого и первого разрядов).

В этом такте машинного времени мультиплексоры 5 и 6 формируют значение результата операции, заданной

8-разрядным кодом.на группе настроечных входов 19 в зависимости от зна55 чений сигналов на входах 10 и 11 данных, на выходах коммутаторов 7 и

8 и на выходах D-триггеров 1 и 2.

По фронту тактового сигнала, ноступающего с второго тактового входа 21 устройства через элемент 9 запрета на тактовые входы D-триггеров 1 и 2, происходит запись результатов операции с выходов мультиплексоров 5 и 6.

При реализации операций второй группы сигнал на первом тактовом входе 20 равен "Лог. 0". При этом в каждом такте машинного времени происходит вычисление результата операции так же, как во втором такте.

При последовательном соединении нескольких устройств для образования многоразрядного вычислителя выход 14 каждого предыдущего устройства должен соединяться с входом 12 последующего устройства для образования цепи переноса вправо.

Работа многофункционального устройства в режимах формирования сигналов переноса и результата характеризуется таблицей истинности.

Коды управления операциями получены иэ предположения, что первый управляющий вход мультиплексора имеет вес 22 второй 2! третий — 2 о.

Многофункциональное устройство, содержащее четыре D-триггера, два мультиплексора и элемент запрета, причем выход первого мультиплексора соединен с информационными входами первого и второго D-триггеров и с асинхронным выходом нулевого разряда устройства, асинхронный выход первого разряда которого соединен с выходом второго мультиплексора и информационными входами третьего.и четвертого

B-триггеров, первый тактовый вход устройства соединен с тактовыми вхоВычисление вычислении

Операция

Вход 22 Вход 20

Сложение

А:А+В

1 1 1

0 О 1

0 О

О О 1

1 1

1 О 1

1 О 1

1 О 1

1 1

О .1 1

О О О 1 О

0 1 1 0 1

О 1 1 1 О

0 1 1 0 1

0 1 0 1 1 ! 0 1 0 О

1 1 1 1 О

0 1 О О

О 0 1 1 1

О О О О О

1

О

О

1

О

О

Х

1

О

0

О t

О

О

Перенос

Результат

Перенос

Результат

Перенос

Результат

Перенос

Результат

То же

Вычитание

А:А-В Инкремент

А:=А+!

Декремент

А:=А-1

ИЛИ А: АЧВ

И А:=AAB

Инв рсия

А: * А

1 1 1 О 0 О О

Формула и э обретения

20503 6 дами второго и четвертого D-триггеров и первым входом элемента запрета, второй вход которого соединен с вторым

5 тактовым входом устройства выход пе1 реноса которого соединен с выходом четвертого D-триггера, выход первого разряда устройства соединен с выходом третьего D-триггера, тактовый вход которого соединен с выходом элемента запрета и тактовым входом первого

D-триггера, выход которого соединен с выходом нулевого разряда устройства, информационные входы первого и второго мультиплексоров соединены с группой настроечных входов устройства, о т л и ч а ю щ е е с я тем, что, с целью упрощения устройства за счет сокращения количества внеш20 них связей, оно дополнительно еодержит два коммутатора, выходы которых соединены соответственно с первыми управляющими входами первого и второго мультиплексоров, вторые

25 управляющие входы которых соединены соответственно с входами данных нулевого и первого разрядов устройства, первый и второй входы переноса которого соединены соответственно с пер 0 выми информационными входами первого и второго коммутаторов, управляющие входы которых соединены с входом управления арифметическими операциями и операциями сдвигов устройства, вы35 ход третьего D-триггера соединен с вторым информационным входом первого коммутатора и третьим управляющим входом второго мультиплексора, третий управляющий вход первого мультиплексора соединен с выходом первого Dтриггера, выход второго D-триггера соединен с вторым информационным входом второго коммутатора.

1520503

Продолжение таблицы

Вычисление

Операция вычислении

Вход 22 од 20

О О О 0 О

1 ! О

Результат

Перенос

О О О

О О О

Х

О !

О О 1

О О О О

О О 1

О О О О

О 1 О

Результат

Перенос

Результат

Перенос

Результат

О 0 1

1 1

О 1 О

1 1 1

О 1 О

Х

О

О

0 1 О 1 О

О О 1 1 О

0 О О О

1 О 1

О 1

1 1

П р и и е ч а н и е . Х - безразличное состояние (О или 1).

Редактор В. Данко

Закаэ 6758(49 Тиржк 668 Подписное

ВНИИПИ Государственного комитета по иэобретениям и открытиям при ГКНТ СССР

113035 ° Москва, Ж-35, Рау!нская наб., д. 4/5

МВ

Проиэаодственно-иэдательский комбинат "Патент", г.ужгород, ул. Гагарина,101

Очистка Л: О

Проверка АО

Присвоение

А: В

Сдвиг А + Аь, вправо

Сдвиг h» А, ! Ьз влаво

Аргументы (управлещие входы мультиплексора) Составитель В. Сорокин

Текред А.Кравчук . Корректор М. Иакснмишинец