Устройство для диагностирования логических блоков

Иллюстрации

Показать всеРеферат

Изобретение относится к автоматике и вычислительной технике и может быть использовано для контроля работоспособности и поиска дефектов в логических блоках ОЗУ. Цель изобретения - повышение достоверности контроля. Устройство содержит генератор 1 импульсов, задатчик 2 тестов, блок 3 управления, блок 4 индикации, два блока 5, 6 элементов И, блок 7 сравнения. Перед началом диагностирования во все ячейки ОЗУ записывается нулевая информация. Для организации диагностирования используется цикл обращения к одной ячейке ОЗУ, состоящий из трех этапов: первый этап - считывание хранимой информации, второй этап - запись информации в выбранную ячейку ОЗУ, третий этап - считывание записанной на втором этапе информации. Положительный эффект определяется введением блока сравнения и соответствующей структуры задатчика тестов. 8 ил.

СОЮЗ СОВЕТСНИХ

СОЦИАЛИСТИЧЕСНИХ

РЕСПУБЛИН (5D 4 G 06 F 11 00

ГОСУДАРСТВЕННЫЙ НОМИТЕТ

ПО ИЗОБРЕТЕНИЯМ И ОТНРЫТИЯМ

ПРИ ГКНТ СССР

1 (21) 4 145263/24-24 (22) 10. 11.86 (46) 07. 11.89. Бюл. N - 41 (7? ) В. В.Данилов, И. H. Клюев и В.Т.Тяжев (53) 681.3 (088.8) (56) Патент США N - 3573751, кл. G 06 F 11/02, 1971.

Авторское свидетельство СССР

Р 875390, кл. С 06 Р 15/46, 1981. (54) УСТРОЙСТВО ДЛЯ ДИАГНОСТИРОВА,НИЯ ЛОГИЧЕСКИХ БЛОКОВ (57) Изобретение относится к автоматике и вычислительной технике и может быть использовано для контроля работоспособности и поиска дефектов в логических блоках ОЗУ. Цель изоб.ретения — повышение достоверности

„.зо„„152051я А1

2 контроля. Устройство содержит генератор 1 импульсов, задатчик 2 тестов, блок 3 управления, блок 4 индикации, два блока 5, 6 элементов И, блок 7 сравнения. Перед началом диагностирования во все ячейки ОЗУ записывается нулевая информация. Для организации диагностирования используется цикл обращения к одной ячейке.

ОЗУ, состоящий из трех этапов: первый этап — считывание хранимой информации, второй этап — запись информации в выбранную ячейку ОЗУ, третий этап — считывание записанной на втором этапе информации. Положительный эффект определяется введением блока сравнения и соответствующей структуры задатчика тестов. 8 ил.

1520518

Изобретение относится к автоматике и вычислительной технике и может быть использовано для контроля работоспособности и поиска дефектов в логических блоках.

Целью изобретения является повышение достоверности контроля °

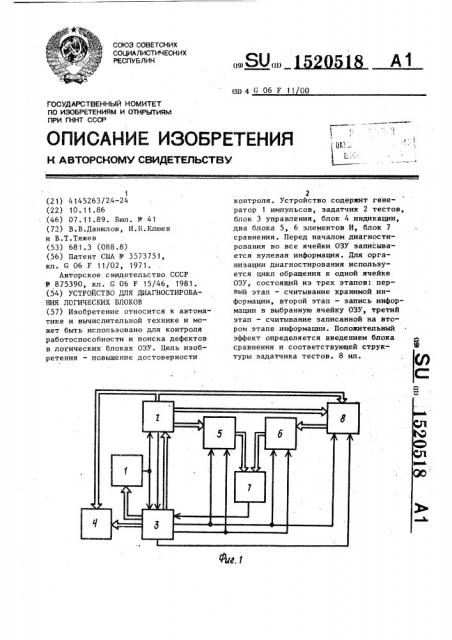

На фиг.1 представлена блок-схема предлагаемого устройства, на фиг.2— схема эадатчика тестов, на фиг.3— схема блока управления, на фиг.4— схема генератора адреса, на фиг.5схема генератора псевдослучайной последовательности; на фиг.б — схема узла синхронизации, на фиг.7 — схема первого распределителя импульсов, на фиг.8 — схема второго распределителя импульсов.

Устройство для диагностирования логических блоков (фиг. 1) содержит генератор 1 импульсов, задатчик 2 тестов, блок 3 управления, блок 4 индикации, два блока 5 и 6 элементов И, 1 блок 7 сравнения и контролируемыи блок 8.

Задатчик,2 тестов (фиг.2) содержит.генератор 9 адреса, четыре блока 10-13 элементов И, регистр 14, счетчик 15, блок 16 сравнения, делитель 17 частоты, генератор 18 псевдослучайной последовательности.

Блок 3 управления (фиг. 3) содержит триггер 19, узел 20 синхронизации, два делителя 21 и 22, узел

23 формирования начальных условии, 35 счетчик 24, два элемента ИЛИ 25 и

26, генератор 27 одиночных импульсов, два дешифратора 28 и 29, два элемента 30 и 31 задержки.

Генератор 9 адреса (фиг. 4) содержит элемент 32 задержки, элемент И

33, реверсивный генератор 34 псевдослучайной последовательности, блок

35 элементов И, реверсивный счетчик

36, блок 37 сравнения, регистр 38

45 и триггер 39.

Генератор 18 псевдослучайной последовательности (фиг.5) содержит базовые ячейки 40-43, элементы И 44-47, элемент НЕ.48, элементы ИЛИ 49-51, сумматор 52 по модулю два, триггер 53.

Реверсивный генератор 34 псевдослучайной последовательности выполнен по такой же схеме как и генератор 18 псевдослучайной последователь- 55 ности

Узел 20 синхронизации (фиг. 6) содержит два распределителя 54 и 55 импульсов, элементы ИЛИ 56 и 57 и элемент И 58.

Распределитель 54 импульсов (фиг.7) содержит триггер 59, элементы И 6064, элемент 65 задержки, элемент

И-НЕ 66.

Распределитель 55 импульсов (фиг.8) содержит элемент НЕ 67, элементы И

68-71, счетчик 72, элемент 73 задержки и дешифратор 74.

Устройство для диагностирования логических блоков работает следующим образом. . С помощью органов управления узла

23 устанавливается код числа циклов (КЧЦ)., т.е. число начальных состояний генератора 9 адресов в эадатчике

2 тестов ° Кроме этого, с блока 3 управления на задатчик 2 тестов подается код места нулевой комбинации (КИНК) s генераторе 9 адресов задатчика 2 тестов.

С помощью органов управления узла

23 подается команда "Пуск", по которой производится запуск работы всего устройства.

По команде "Пуск" блок 3 управления производит следующие операции: а) вырабатывает сигнал ПГИ-пуск геневатора тактовых импульсов, после чего тактовые импульсы с генеоатора

1 импульсов поступают на задатчик 2 тестов и на узел 20 синхронизации блока 3 управления; б) одновременно с сигналом ПГИ вырабатывает сигнал Уст. 0 - установка в состояние "0" делителя 21. Это состояние дешифрируется и на выходе

ДШ 1 дешифратора 29 появляется разрешающий сигнал, который поступает на узел 20 синхронизации, в) с задержкой относительно сигнала ПГИ вырабатывает сигнал записи

ЗП 1, который поступает в задатчик 2 тестов. По сигналу ЗП 1 в эадатчике

2 тестов запоминается начальное состояние генератора 9 адресов; г) с задержкой относительно сигнала ПГИ большей, чем для сигнала

ЗП 1, вырабатывает сигнал записи ЗП

2, который поступает в эадатчик 2 тестов..По сигналу ЗП 2 в генератор

9 адресов записывается начальное состояние, которое было запомнено по сигналу ЗП 1 ранее; д) одновременно с сигналом ЗП 2 вырабатывает сигнал РЗТИ. - сигнал разрешения прохождения тактовых им15205

lIvJIE сов на узел 20 синхронизации.

Сигнал РЗТИ поступает на узел 20 синхронизации.

Далее производится запись 0 в ячейки памяти проверяемого блока 8 при изменении адресов в прямом направ ленин. Сигналы ЗП, СЧ2 Зп/Сч, РСРВ устанавливаются равными "0". Сигнал

ЗП подается на задатчик 2 тестов и устанавливает значение эталонной ответной реакции равным "0". Сигнал СЧ 2 поступает на задатчик 2 тестов и устанавливает значение записываемой информации равным "0". Сигнал Зп/Сч поступает на блоки 5 и 6 элементов И и на проверяемый блок 8 и устанавливает режим записи. Сигнал PCPB по ступает на блоки 5 и 6 элементов И и запрещает прохождение через них сиг- 20 налов. С приходом очередного тактового импульса в узле 20 синхронизации вырабатывается отрицательный импульс

РЗЗС. По этому импульсу производится запись информации в проверяемый 25 блок 8.

Если перебор адресов не закончен : то с приходом очередного тактового импульса производится выработка положительнОГО импульса СДВ с пОмОЩью 3О узла 20 синхронизации. Импульс СДВ поступает в задатчик 2 тестов и вызывает изменение адреса, по которому будет записываться информация.

Если перебор адресов закончен, то в,задатчике 2 тестов вырабатывается сигнал СРВ, который поступает на блок 3 управления. Сигнал CPB учитывается при подсчете начальных состояний генератора 9 адресов в эадатчике 2 тестов. В делителе 21 сигнал CPB вызывает смену c,oñòoÿíèÿ и дешифратор 29 вырабатывает сигнал

ДШ 2. При этом устройство переходит в режим проверки работы ячеек памяти проверяемого блока 8. Для этого узел

20 синхронизации вырабатывает необходимые последовательности сигналов

РСРВ, РЗЗС, Зп/Сч, ЗП, СЧ 2. Организуется трехкратное обращение к про- 5О веряемому блоку 8. Сначала считывает= ся содержащаяся в ячейке информация, происходит сравнение ответной реакции (OP) проряемого блока 8 с эталонной ответной реакцией (ЭОР), вырабатываемой эадатчиком 2 тестов (ЭОР = О) .

Далее, не меняя адреса, производится запись информации, выработан18 6 ной генератором. 18 ЛСП задатчика 2 тестов, в проверяемый блок 8, сравнение OP и ЭОР не производится °

При обращении к ячейке памяти в третий раз производится считывание только что записанной информации и сравнение OP и ЭОР.

Если проверка всех ячеек памяти успешно прошла и перебор адресов в прямом направлении закончен, то производится переход на перебор тех же адресов в строго обратном направлении. При этом в задатчике 2 тестов изменяется сигнал ПН на обратный и генераторы 9 и 18 адресов и ПСП соответственно будут изменять свои состояния в строго обратной последовательности.

Если проверка ячеек памяти на одном начальном состоянии генератора 9 адреса в прямом и обратном направлениях изменения адресов прошла успешно и не было сбоев, то осущесТвляется установка и запоминание нового начального состояния генератора 9 адреса. Для этого блок 3 управления с приходом соответствующего сигнала

СРВ вырабатывает последовательность сигналов ПГИ, ЗП 1, ЗП 2.

Проверка конца перебора начальных состояний производится в блоке 3 уп- равления.

Если при любом иэ сравнения OP u

ЭОР выявилось несравнение, тогда блок

7 сравнения вырабатывает сигнал HCPB— несравнение, который поступает в блок 3 управления.

Блок 3 управления формирует сигнал НИСП вЂ” неисправно, который поступает на блок 4 индикации, и сигнал СГИ, Блок 4 индикации вырабатывает сообщение "Неисправно" и сообщает адрес, по которому произошла ошибка.

Задатчик 2 тестов (фиг. 2) работает следующим образом.

В исходном состоянии, т.е. после включения питания, генератор 9 адреса и генератор 18 ПСП находятся в произвольном состоянии на выходе делителя 17 частоты присутствует нулевое значение сигнала, а на счетчик

15 с генератора 1 импульсов поступают тактовые импульсы (ТИ), по которым происходит изменение состояния счет- .

1520518 чика 15. Из блока 3 управления в генератор 9 адреса записывается код места нулевой комбинации (KMHK) по которому определяется в ПСП положение нулевой комбинации, т.е. место нулевого адреса в последовательности адресов, Затем по сигналу ЗП 1 от бло.ка 3 управления открывается блок 12 элементов И и состояние счетчика 15 через блок 12 элементов И записывается в регистр 14 ° Затем по

1 сигналу ЗП 2 от блока 3 управления, во-первых, открывается блок 10 элементов И и содержимое регистра.14 поступает в генератор 9 адреса, откуда поступает адрес (АДР) на блок 16 сравнения, к блоку 4 индикации и к проверяемому блоку 8, вовторых, генератор 9 адреса устанавливается в рабочее состояние. Затем по сигналу ЗП от блока 3 управления в задатчик 2 тестов иэ содержимого генератора 18 ПСП формируется: вопервых, через блок 11 элементов И 25 ненулевая эталонная ответная реакция (ЭОР), поступающая на блок 5 элементов И, во-вторых, через блок 13 .элементов И нулевой тестовый набор (ТН), поступающий на проверяемый блок 3О

8. Затем по сигналу СЧ 2 от блока 3 управления формируются нулевая ЭОР и ненулевой ТН. Затем по сигналу СДВ происходит сдвиг информации в генераторах 9 адреса и 18 ПСП. После этого работа задатчика 2 тестов повторяется по сигналам ЗП,, СЧ2, СДВ, Если на информационном выходе генератора 9 адреса появляется нулевая комбинация, то на управляющем выходе 4О появится сигнал РЗС вЂ” разрешения сравнения, поступающий на блок 16 сравнения. Если содержимое регистра 14 начальных состояний равно адресу на выходе генератора 9 адреса, то иа вы- 45 ходе блока 16 сравнения появляется сигнал СРВ, поступающий: во-первых, на блок 3 управления, во-вторых, на делитель 17 частоты. Каждый второй сигнал CPB вызывает изменение сигнала перемены направления (ПН) на выходе делителя 17 частоты. Этот сигнал поступает на генераторы 9 адреса и 18

ПСП и вызывает изменение направления сдвига содержимого этих генераторов.

После проверки проверяемого блока

8 на первом начальном состоянии работа задатчика 2 тестов повторяется на следующем начальном сoc"тоянии по сигналам ТИ, ЗП 1, ЗП 2, ЗП, СЧ 2 и

СДВ.

Генератор 9 адреса (фиг. 4) работает следующим образом.

От блока 3 управления в регистр 38 записывается КИНК вЂ” код места нулевой комбинации в ПСП. Затем от блока 3 управления поступает сигнал ЗП 2, который обнуляет счетчик 36 и триггер

39. Одновременно с этим осуществляется запись НС вЂ” начального состояния из регистра 14 начальных состояний в генератор 34 ПСП через блок 10 элементов И. Затем от блока 3 управления поступает импульс СДВ, который, вопервых, увеличивает на единицу содержимое счетчика 36, во-вторых, через время, достаточное для изменения содержимого счетчика 36 и определяемое элементом 32 задержки, поступает через элемент И 33 как задержанный импульс СДВ на генератор IICII 34 и изменяет содержимое этого генератора.

Если содержимое счетчика 36 равно

KNHK, запомненного в регистре 38, то на выходе блока 37 сравнения появится нулевой сигнал НСРВ, который, во-первых, устанавливает в единицу триггер 39, ha прямом выходе которого появляется единичный сигнал РЗС, поступающий на блок 16 сравнения,. во-вторых, закрывает блок 35 элементов И и обеспечивает нулевую комбинацию в ПСП, в-третьих, поступает на вход элемента И 33 и запрещает прохождение импульса СДВ на генератор

ПСП 34, что позволяет избежать по-. тери текущего состояния этого генератора. Следующий импульс СДВ изменяет содержимое счетчика 36, на выходе блока 37 сравнения появляется единица, блок 35 элементов И и элемент И

33 открывается и на выходе генератора

IICH 34 появляется текущее состояние.

Если генератор ПСП 34 вернулся в начальное состояние, то от делителя 17 частоты поступает сигнал ПН, который, во-первых, подается на счетчик 36 и переводит его иэ режима суммирования в режим вычитания, во-вторых, поступает на генератор ПСП 34 и изменяет направление сдвига информации. После этого работа генератора 9 адреса повторяется при обратном переборе состояний генератора ПСП 34 °

1520518 формула изобретения

Устройство для диагностирования логических блоков, содержащее генератор импульсов, задатчик тестов, блок управления, блок индикации и два блока элементов И, причем входы пуска и останова генератора импульсов соединены с соответствующими выходами бло10 ка управления, группа выходов синхронизации которого соединена с группой соответствующих входов задатчика тестов, первая группа информационных выходов которого является группой информационных выходов устройства для подключения к группе информационных входов контролируемого блока, о т личающееся тем,что,с целью повышения достоверности контроля, в него введен блок сравнения, причем группа адресных выходов задатчика тестов соединена с группой информационных входов блока индикации и является группой адресных вы- у5 ходов устройства для подключения к группе адресных входов контролируемого блока, вторая группа информационных выходов эадатчика тестов соединена с группой информационных входов первого блока элементов И, первый вход стробирования которого объединен с первым входом стробирования второго блока элементов И и подключен к выходу разрешения сравнения блока управления, выход записи-чтения которого соединен с вторыми входами стробирования первого и второго блоков элементов И и является выходом записи-чтения устройства для подключения к входу записи-чтения

40 контролируемого блока, выхОд разрешения записи блока управления является выходом устройства для подключения к входу записи контролируемого

45 блока, группа информационных входов устройства для подключения группы выходов контролируемого блока соединена с группой информационных входов второго блока элементов И, группа выходов которого соединена с первой группой входов блока сравнения, вторая группа входов которого соединена с группой выходов первого блока элементов И, группа управляющих входов блока индикации соединена с группой

1 выходов адреса неисправной точки блока управления, вход признака неисправности которого соединен с выходом неравенства блока сравнения, вход начала цикла контроля блока управления соединен с соответствующим выходом задатчика тестов, вход синхронизации которого объединен с входом синхронизации блока управления и подключен к выходу генератора импульсов, причем блок управления содержит узел синхронизации, узел формирования начальных условий, два делителя, два дешифратора, два элемента ИЛИ, счетчик, генератор одиночного импульса, триггер и два элемента задержки, причем вход признака неисправности блока соединен с первым входом первого элемента ИЛИ и является выходом "Неисправно блока управления, выход первого дешифратора которого соединен с вторым входом первого элемента ИЛИ и является выходом "Исправно" блока, вход первого дешифратора соединен с информационным выходом счетчика, группа информационных входов которого соединена с первой группой выходов начальных условий узла формирования начальных условий, вторая группа выходов начальных условий которого, группа выходов узла синхронизации и выходы первого и второго элементов задержки образуют группу выходов синхронизации блока управления, выход пуска генератора одиночного импульса которого соединен с входами первого и второго элементов задержки, с вывходом установки в " 1" триггера, с входом установки в "0" первого делителя и с выходом генератора одиночного импульса, вход которого соединен с выходом второго элемента ИЛИ, первый вход которого объединен с входом синхронизации счетчика и подключен к выход второго делителя, вход синхронизации которого объединен с входом синхронизации первого делителя и является входом начала цикла контроля блока управления, вход синхронизации которого соединен с входом узла синхронизации, первый и второй входы режима которого соединены соответственно с первым и вторым выходами второго дешифратора, вход которого соединен с выходом первого делителя, первый, второй,и третий выходы узла синхронизации являются соответственно выходами запись-чтение, разрешения сравнения и разрешения записи блока управления, выход останова генератора одиночного импульса

i 520518

)2 которого соединен с выходом первого элемента ИЛИ, второй вход второго элемента ИЛИ соединен с выходом пуска узла формирования начальных условий, выход второго элемента задержки соединен с входом установки в "0" триггера, инверсный выход которого соединен с входом запуска узла синхронизации, причем задатчик тестов содержит генератор адреса, генератор псевдослучайной последовательности, блок сравнения, счетчик, регистр, делитель и четыре блока элементов И, причем группа выходов генератора адреса сое- 15 динена с первой группой входов блока сравнения задатчика тестов и является группой адресных выходов задатчика тестов, выход начала цикла контроля которого соединен с выходом равенства блока сравнения эадатчика тестов и входом делителя задатчика тестов, выход делителя которого соединен с входами задания режима работы генератора адреса и генератора псев- 2 дослучайной последовательности, входы сдвига которых объединены и подключены к группе входов синхронизации задатчика тестов, первая группа информационных выходов которого соединена с группой выходов первого блока элементов И эадатчика тестов, группа входов первого блока элементов И которого соединена с группой выходов, генератора псевдослучайной последовательности.и с группой входов второго блока элементов И зада чика тестов, группа выходов второго блока элементов И которого является второй группой информационных выходов эадатчика тестов, вход синхронизации которого соединен со счетным входом счетчика задатчика тестов, группа информационных выходов счетчика которого соединена с группой входов третьего бло- „ ка элементов И задатчика тестов, группа выходов третьего блока элементов

И которого соединена с группой входов регистра эадатчика тестов, группа выходов регистра которого соединена с второй группой входов блока сравнения задатчика тестов и группой входов четвертого блока элементов И, вход которого соединен с установочным входом генератора адреса и подключен к группе входов синхронизации задатчика тестов, вход разрешения сравнения блока сравнения задатчика тестов соединен с выходом разрешения сравнения генератора адреса, группа информационных входов которого соединена с группой выходов четвертого блока элементов И, входы первого,второго, третьего блоков элементов И задатчика тестов и группа входов начальных условий генератора адреса вместе с входом четвертого блока элементов И и входом сдвига генератора адреса и генератора псевдослучайной последовательности образуют группу входов синхронизации задатчика тестов, причем генератор адреса содержит реверсивный генератор псевдослучайной последовательности, реверсивный счетчик, блок сравнения, регистр, триггер, блок элементов И, элемент И и элемент задержки, выход которого соединен с первым входом элемента И генератора адреса, выход элемента И которого соединен с входом сдвига реверсивного генератора псевдослучайной последовательности, группа выходов которого соединена с группой входов блока элементов И генератора адреса, вход сдвига которого соединен с входом элемента задержки генератора адреса и счетным входом реверсивного счетчика, группа выходов которого соединена с первой группой входов блока сравнения генератора адреса, установочный вход которого соединен с установочным входом реверсивного счетчика и с входом установки в

"0" триггера генератора адреса, группа информационных входов которого соединена с группой входов реверсивного генератора псевдослучайной последовательности, вход режима которо-. го соединен с входом режима реверсивного счетчика и является входом за" дания режима работы генератора адреса, группа входов начальных условий которого соединена с группой входов регистра генератора адреса, группа выходов регистра которого соединена с второй группой входов блока сравнения генератора адреса, выход не-. сравнения блока. сравнения которого соединен с входом установки в " 1" триггера, с входом блока элементов

И и с вторым входом элемента И генератора адреса, группа выходов блока элементов И которого является группой выходов генератора адреса, выход триггера которого является выходом разрешения сравнения генератора адреса.

1520518 фик 2 ко.1

&. д, 6,8 дл. д;. b

6>.Ю

1520518

1920518

1520518

С ос тавител ь И. Ива ныкин

Редактор В.Бугренкова Техред Л.Сердюкова Корректор Л.Бескид

Заказ 6759/50 Тираж 668 Подписное

BHHHIIH Государственного комитета по изобретениям и открытиям при ГКНТ СССР

113035, Москва, Ж-35, Раушская наб., д. 4/5

Производственно-издательский комбинат "Патент", r. Ужгород, ул. Гагарина, 101