Стоковое запоминающее устройство

Иллюстрации

Показать всеРеферат

Изобретение относится к вычислительной технике, в частности к запоминающим устройствам, и может быть использовано в системах приема и передачи дискретной информации специализированных вычислителей, а также в буферных запоминающих устройствах систем ввода информации многоканальных измерительных комплексов. Цель изобретения - повышение плотности хранения данных за счет полного заполнения стека при хаотично поступающей приоритетной и обычной информации. Устройство содержит накопитель, адресный счетчик, три блока оперативной памяти, два коммутатора, два распределителя импульсов, дешифратор, три реверсивных счетчики, элемент памяти, два элемента ИЛИ, блок управления. В устройстве разбиение единого адресного поля накопителя на уровни (обычный и приоритетный) происходит по мере поступления информации. Запись информации, следующей за циклом считывания, происходит в первую очередь по уже свободным адресам считанной информации и лишь при отсутствии таковых увеличивается глубина стекла. 4 ил.

СОЮЗ СОВЕТСНИХ

СОЦИАЛИСТИЧЕСКИХ

РЕСПУБЛИН

А1

„„SU(I)) (50 4 G 11 С 19/00

ОПИСАНИЕ ИЗОБРЕТЕНИЯ

ГОСУДАРСТВЕННЫЙ НОМИТЕТ

ПО ИЗОБРЕТЕНИЯМ И ОТНРЫТИЯМ

ПРИ ГКНТ СССР

Н А BTOPCHOMY СВИДЕТЕЛЬСТВУ

1 (21} 44027 29/24-24 (22} 04.04.88 (46) 07.11 89. Бюл, К 41 (7l) Институт проблем моделирования в энергетике АН УССР и Специальное . конструкторско-технологическое бюро с опытным производством Института проблем моделирования в энергетике

АН УССР (72) 10,П. Логвиненко, Г.А. Лобок и Н.М. Лещенко (53) 681.327 .6(088.8) (56) Авторское свидетельство СССР

В 993333, кл. G 11 С 19/00, 1981.

Авторское свидетельство СССР

У 1304078, кл. G ll С 19/00, 1985. (54) СТЕКОВОЕ ЗАПОМИНА10ЩЕЕ УСТРОЙСТВО (57) Изобретение относится к вычислительной технике, в частности к за поминающим устройствам, и может быть использовано в системах приема и передачи дискретной информации специаИзобретение относится к вычислительной технике, в частности к запоминающим устройствам, и может быть использовано в системах приема и передачи дискретной информации специализированных вычислителей, а также в буферных запоминающих устройствах систем ввода информации многоканальных измерительных комплексов, Целью изобретения является увеличение плотности хранения данных: за счет полного заполнения стека при ха2 лизированных вычислителей, а также в буферных запоминающих устройствах систем ввода информации многоканальных измерительных комплексов. Цель изобретения — повышение плотности хранения данных за счет полного за- полнения стека при хаотично поступающей приоритетной и обычной информации. Устройство содержит накопитель, адресный счетчик, три блока оперативной памяти, два коммутатора, два распределителя импульсов, дешифратор, три реверсивных счетчика, элемент памяти, два элемента ИЛИ, блок управления. В устройстве разбиение единого адресного поля накопителя на уровни (обычный и приоритетный) происходит по мере поступления информации. Запись информации, следующей за циклом считывания, происходит в первую очередь по уже свободным адресам считанной информации и лишь при отсутствии таковых увеличивается глубина стека. 4 ил. отично поступающей приоритетной и обычной информации.

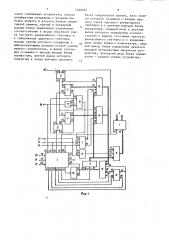

На фиг. 1 представлена схема стекового запоминающего устройства; на фиг, 2 — схема блока управления; на фиг..3 — схема распределителя импульсов; на фиг, 4 — временная диаграмма работы устройства, Стековое запоминающее устройство содержит накопитель 1, блок 2 управления, первый 3 и второй 4 реверсивные счетчики, первый 5 и второй Ь

1520597 коммутаторы, дешифратор 7, первый 8 и второй 9 распределители импульсов, адресный счетчик 10, третий реверсивный счетчик 11, первый элемент ИЛИ

12, первый 13 второй 14 и третий

I5 блоки оперативной памяти, элемент

16 памяти, второй элемент ИЛИ 17, входы записи 18 и чтения 19 устройства, первый 20 и второй 21 входы синх11 ронизации устройства, выход Стек занят" 22„ управляющий выход 23 считывания, выход "Стек пуст" 24 и выход

25 признака приоритета.

Блок управления (фиг. 2) содержит узел 26 постоянной памяти, триггеры

27 и 28 и элементы ИЛИ 29 и 30.

Распределитель импульсов (фиг. 3) содержит иквертор 31 и элементы ИЛИ

32 и 33.

Стековое запоминающее устройство работает следующим образом.

Перед началом работы все. счетчики устройства устанавливаются в одинаковое нулевое состояние (цепь начальной установки не показана), При этом на всех выходах состояния реверсивных счетчиков 3, 4 и 11 сигналы низкого уровня. Следовательно, на выходе

"Стек пуст" 24 устройства также сигнал низкого уровня, свидетельствующий об отсутствии записанной информации в накопителе l.

При поступлении на вход 18 уст" ройства сигнала ""Запись" второй коммутатор 6 подклю-.:ает (по сигналу на его управляющем входе,"1=0) через первый коммутатор 5 (K2=0) выходы адресного счетчика .10 к адресным входам накопителя 1. По сигналам t< (фиг. 4) на первом входе 20 синхронизации устройства блок 2 управления формирует сигналы записи с, и л

IIo которым осуществляется запись 9 информации в накопитель 1, и адресный счетчик 10 переводится (положительным перепадом из "О" в "1") в следующее фазовое состояние. Одновременно осуществляется запись использованного адреса накопителя в зависимости от наличия сигнала признака приоритета на входе 25 устройства в первый блок 13 оперативной памяти сигналом,, либо во второй блок 14 оперативной памяти сигналом,,, после чего соответствующий реверсивный счетчик (первый 3 или второй 41 также переходит в следующее фазовое состояние. При этом

55 все адреса хранящейся в накопителе 1 информации, пришедший с признаком приоритета, запоминаются во втором блоке 14 оперативной памяти, а без признака — в первом блоке 13 опера- тивной памяти, Вход "Запись" 18 устройства имеет приоритет по отношению к входу "Чтение" 19 во всех случаях, кроме того, когда накопитель полностью загружен несчитанной информацией, т.е. имеет место высокий уровень сигнала на выходе "Стек занят" 22 устройства. Такая организация позволяет исключить потерю поступающей информации.

Считывание информации, записанной в стек, осуществляется следующим образом.

При низком уровне сигнала "Чтение" на входе 19 устройства блок 2 управления формирует по сигналу t (фиг.4) второй тактирующей последовательности л на входе 21 сигнал считывания z на своем втором выходе. Одновременно этим же сигналом ñ, в блоке 2. управления взводится триггер 28 и на второй вход элемента ИЛИ 30 поступает разрешающий сигнал низкого уровня, Первый распределитель 8 импульсов пропускает на вход обратного счета перво-о реверсивного счетчика 3 сигнал с,, при отсутствии записанной информации на приоритетном уровне стека либо на вход обратного счета второго реверсивного счетчика 4 сигнал, при. наличии информации на приоритетном уровне стека. После этого соответствующий реверсивный счетчик устанавливает на адресных входах соответствующего блока оперативной памяти (13 или 14) адрес последней записанной информации на данном уровне стека. Дешифратор устанавливает разрешающий сигнал (Ч,или V низкого уровня )на управляющем входе выборки данного блока оперативной памяти, после чего адрес для считывания информации устанавливается на адресных входах накопителя 1, так как ка управляющем входе второго коммутатора 6 присутствует сигнал высокого уровня (К21). Для управления внешними устройствами выдается на управляющий выход 21 устройства сигнал

"Считывание" низкого уровня (V 0).

В то же время адрес, по которому производится считывание информации из накопителя, запоминается третьим бло"

5 15, ком 15 оперативной памяти по сигналу

Этот сигнал формируется блоком

2 управления на девятом выходе по сигналу t< с выхода элемента ИЛИ 30, после чего второй триггер 28 устанавливается в исходное состояние.

По окончании сигнала (положительным перепадом) третий реверсивный счетчик ll переходит в следующее фазовое состояние и на его выходе состояния устанавливается сигнал V 1 высокого уровня. После этого первый коммутатор сигналом K=1 подключает к своим выходам выходы третьего блока

15 оперативной памяти и в дальнейшем запись в накопитель новой информации осуществляется по адресам ранее считанной информации. При такой записи сигналом третий реверсивный счетчик 11 переводится в предыдущее фазовое состояние, сигналом V осуществляется выборка запомненного адреса, который устанавливается (Кl=l, К2=0) на адресных входах накопителя

1, В то же время в блоке 2 управления осуществляется взведение триггера 27, выходной сигнал которого разрешает формирование на первом выходе блока

2 управления сигнала записи ., по сигналу tl первой тактирующей последоВательности. По окончании записи триггер 27 сбрасывается положительным перепадом импульса

Формула изобретения

Стековое запоминающее устройство, содержащее накопитель, информацион-. ные входы и выходы которого являются одноименными входами и выходами устройства, блок управления, первый и второй реверсивные счетчики, первый и второй коммутаторы, о т л и ч а— ю щ е е с я тем, что, с целью увеличения плотности хранения данных за счет полного заполнения стека при хаолично поступающей приоритетной и обычной информации, в устройство введены первый, второй и третий блоки оперативной памяти, первый и второй распределители импульсов, дешифратор, адресный счетчик, третий реверсивный счетчик, первый и второй элементы

ИЛИ, элемент памяти, причем адресные входы накопителя соединены с выходами второго коммутатора, информационные входы первой группы которого подключены к выходам первого и второго

20597 6 блоков оперативной памяти и к информационным входам третьего блока оперативной памяти, адресные входы и вы5 ходы которого соединены соответственно с информационными выходами третьего реверсивного счетчика и первой группы первого коммутатора, выходы которого подключены к информационным входам второй группы второго коммутатора и первого и второго блоков оперативной памяти, адресные входы которых соединены соответственно с информационными выходами первого и второго реверсивных счетчиков, входы обратного счета которых подключены соответственно к первому и второму выходам первого распределителя импульсов, первый вход которого соединен

20 с установочным входом элемента памяти и вторым выходом блока управления, первый выход которого подключен к входу записи накопителя и к первому входу второго распределителя им25 пульсов, второй Вход которого явля ется входом признака приоритета уст— ройства, а первый выход соединен с входом записи первого блока оперативной памяти и с входом прямого счета первого реверсивного счетчика, выход состояния которого подключен к первому входу второro элемента ИЛИ, выход которого является выходом признака

ВСтек пуст" устройства и соединен с пятым входом блока управления, первый и второй входы которого являются первым и вторым входами синхронизации устройства, третий вход блока управления является Входом записи устрой40 ства и подключен к первым входам дешифратора и первого элемента ИЛИ, второй вход которого соединен с восьмым выходом блока управления и является выходом признака "Стек занят"

45 устрОЙства Выход перВОГО элемента

ИЛИ подключен к управляющему входу второго коммутатора, второй выход второго распределителя импульсов соединен с входом записи второго блока

50 оперативной памяти и с входом прямого счета второго реверсивного счетчика, выход состояния которого подключен к вторым входам первого распределителя импульсов и второго элемента

ИЛИ H K ВхОду сброса элемента памяти, выход которого соединен с третьим вхо-. дом дешифратора, второй вход которого подключен к пятому выходу блока управления и является управляющим вы1520597 ходом считывания .устройства, выходы дешифратора соединены с входами выборки первого и второго блоков оперативной памяти, третий и четвертый выходы блока управления. подключены соответственно к входу обратного счета третьего реверсивного счетчика и к синхровходу адресного счетчика, выходы группы которого соединены с информационными входами второй группы первого коммутатора, а выход состояния соединен с шестым входом блока управления, шестой выход которого подклю"- ен к входу выборки третьего блока оперативной памяти, вход записи которого соединен с входом прямого счета третьего реверсивного

5 счетчика и с девятым выходом блока управления, седьмой вход и десятый выход которого подключены соответственно к выходу состояния третьего реверсивного счетчика и к управляющему входу первого коммутатора, седьмой выход блока управления является выходом установочных импульсов устройства, четвертый вход блока управления — входом чтения устройства. (1) (2) 1520597

Фиг 2 (Й) (г) 1520597

Составитель О, Исаев

Техред 11.Дидык

Редактор О, Головач

Корректор И. Пожо

Заказ 7831 Тираж 558 Подписное

ВНИИПИ Государственного комитета по изобретениям и открытиям при ГКНТ СССР

113035, Москва, Ж-35, Раушская наб., д. 4/5

Производственно-издательский комбинат "Патент", г. Ужгород, ул. Гагарина, 101